Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение операционные усилители с двумя токовыми зеркалами, которые управляются входным дифференциальным каскадом (ДК), имеющим на низких частотах широкий диапазон активной работы (повышенные значения напряжения ограничения проходной характеристики ДК [3-12]). Архитектура ОУ данного класса нашла применение в ряде зарубежных быстродействующих ОУ, например, 154УД4, выпускаемом НПО «Биполяр» (Латвия), а также фирмой США Intersil Corporation (микросхема HA2530). Однако, в этом классе известных ОУ не решаются проблемы существенного (выше 200-300 В/мкс) повышения максимальной скорости нарастания выходного напряжения (SR), что обусловлено несовершенством его схемотехники. Указанные недостатки устраняются в предлагаемом ниже схемотехническом решении ОУ.

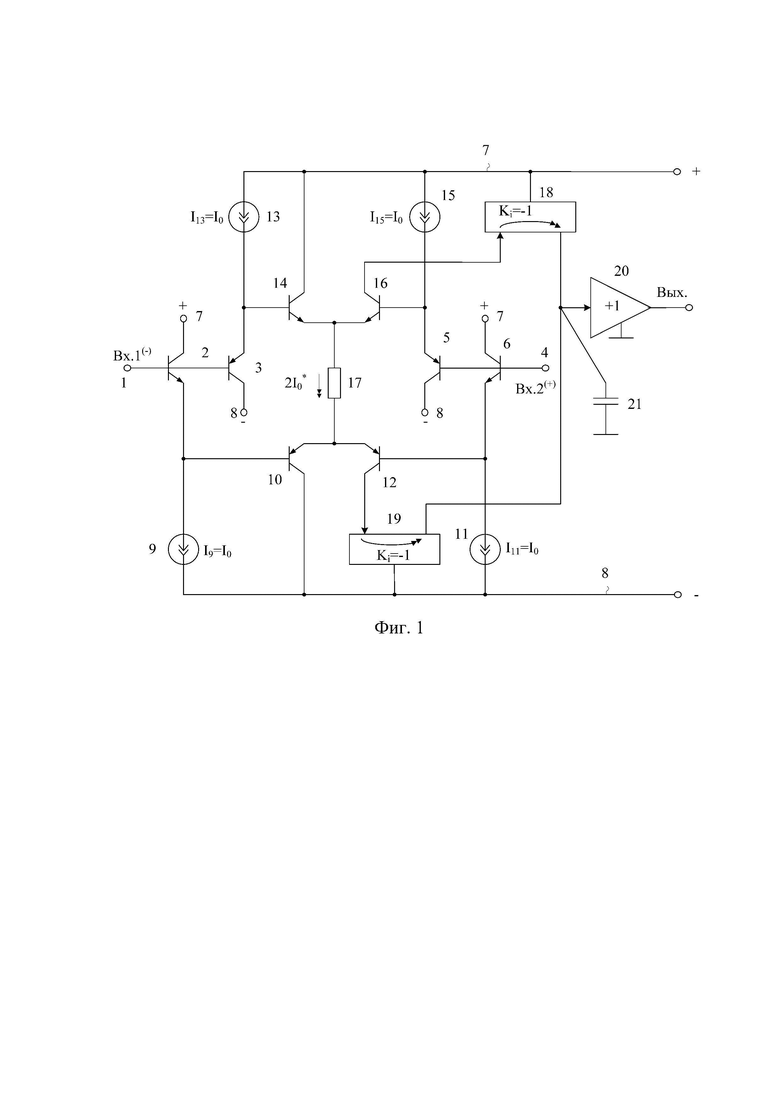

Ближайшим прототипом (фиг. 1) заявляемого ОУ является микромощный операционный усилитель повышенного быстродействия 154УД4, представленный на сайте «Справочный портал по микросхемам» (https://ic-info.ru/upload/iblock/e91/154%D0%A3%D0%941_4.pdf). Он содержит (фиг.1) первый 1 вход, связанный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход, связанный с базами третьего 5 и четвертого 6 входных транзисторов, коллекторы первого 2 и четвертого 6 входных транзисторов согласованы с первой 7 шиной источника питания, а коллекторы второго 3 и третьего 5 входных транзисторов согласованы со второй 8 шиной источника питания, эмиттер первого 2 входного транзистора связан со второй 8 шиной источника питания через первый 9 токостабилизирующий двухполюсник и подключен к базе первого 10 транзистора промежуточного каскада, эмиттер четвертого 6 входного транзистора связан со второй 8 шиной источника питания через второй 11 токостабилизирующий двухполюсник и подключен к базе второго 12 транзистора промежуточного каскада, эмиттер второго 3 входного транзистора связан с первой 7 шиной источника питания через третий 13 токостабилизирующий двухполюсник и подключен к базе третьего 14 транзистора промежуточного каскада, эмиттер третьего 5 входного транзистора соединен с первой 7 шиной источника питания через четвертый 15 токостабилизирующий двухполюсник и подключен к базе четвертого 16 транзистора промежуточного каскада, между объединенными эмиттерами третьего 14 и четвертого 16 транзисторов промежуточного каскада и объединенными эмиттерами первого 10 и второго 12 транзисторов промежуточного каскада включен ограничивающий резистор 17, коллектор третьего 14 транзистора промежуточного каскада согласован с первой 7 шиной источника питания, коллектор первого 10 транзистора промежуточного каскада согласован со второй 8 шиной источника питания, коллектор четвертого 16 транзистора промежуточного каскада подключен ко входу первого 18 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор второго 12 транзистора промежуточного каскада подключен ко входу второго 19 токового зеркала, согласованного со второй 8 шиной источника питания, выходы первого 18 и второго 19 токовых зеркал соединены со входом буферного усилителя 20 и корректирующим конденсатором 21.

Существенный недостаток известного серийного ОУ латвийского производства 154УД4 и его зарубежного аналога HA2530 (фиг. 1) состоит в том, что он имеет сравнительно невысокие предельные значения максимальной скорости нарастания выходного напряжения (SR= 200-300 В/мкс).

Основная задача предлагаемого изобретения состоит в обеспечении повышенных значений максимальной скорости нарастания выходного напряжения ОУ в режиме большого сигнала и уменьшении времени установления переходного процесса без увеличения статического токопотребления и применения дорогостоящих высокочастотных технологических процессов, например, SiGe.

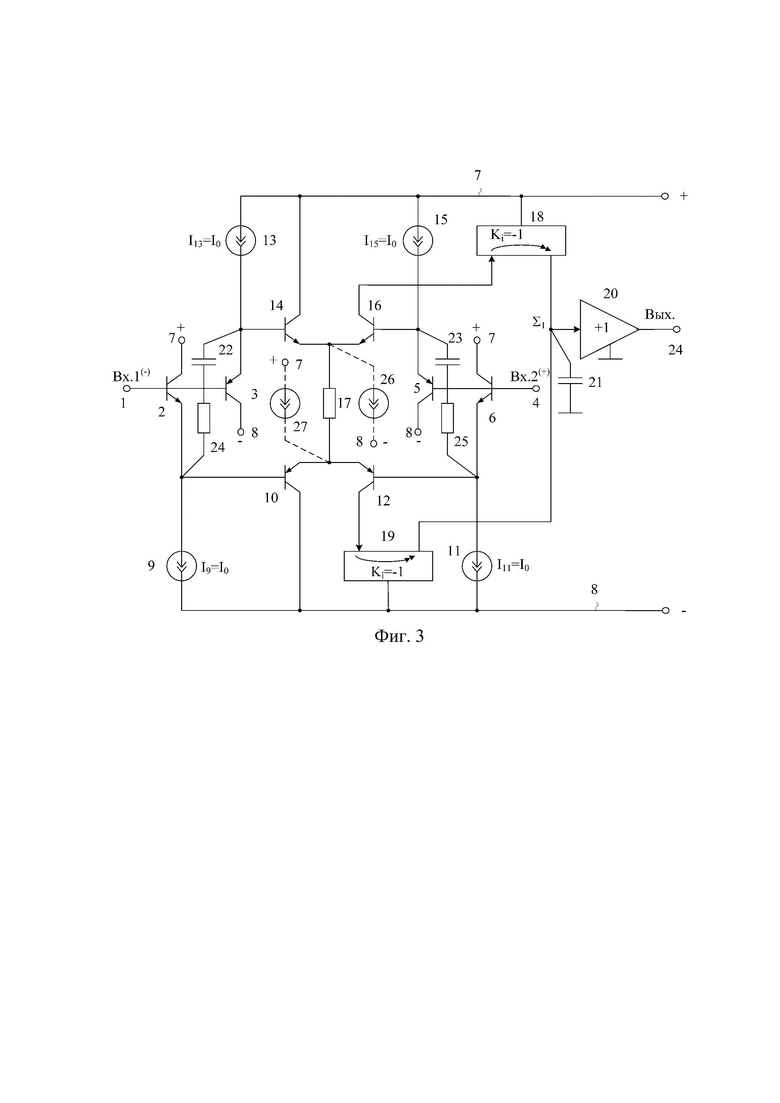

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 вход, связанный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход, связанный с базами третьего 5 и четвертого 6 входных транзисторов, коллекторы первого 2 и четвертого 6 входных транзисторов согласованы с первой 7 шиной источника питания, а коллекторы второго 3 и третьего 5 входных транзисторов согласованы со второй 8 шиной источника питания, эмиттер первого 2 входного транзистора связан со второй 8 шиной источника питания через первый 9 токостабилизирующий двухполюсник и подключен к базе первого 10 транзистора промежуточного каскада, эмиттер четвертого 6 входного транзистора связан со второй 8 шиной источника питания через второй 11 токостабилизирующий двухполюсник и подключен к базе второго 12 транзистора промежуточного каскада, эмиттер второго 3 входного транзистора связан с первой 7 шиной источника питания через третий 13 токостабилизирующий двухполюсник и подключен к базе третьего 14 транзистора промежуточного каскада, эмиттер третьего 5 входного транзистора соединен с первой 7 шиной источника питания через четвертый 15 токостабилизирующий двухполюсник и подключен к базе четвертого 16 транзистора промежуточного каскада, между объединенными эмиттерами третьего 14 и четвертого 16 транзисторов промежуточного каскада и объединенными эмиттерами первого 10 и второго 12 транзисторов промежуточного каскада включен ограничивающий резистор 17, коллектор третьего 14 транзистора промежуточного каскада согласован с первой 7 шиной источника питания, коллектор первого 10 транзистора промежуточного каскада согласован со второй 8 шиной источника питания, коллектор четвертого 16 транзистора промежуточного каскада подключен ко входу первого 18 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор второго 12 транзистора промежуточного каскада подключен ко входу второго 19 токового зеркала, согласованного со второй 8 шиной источника питания, выходы первого 18 и второго 19 токовых зеркал соединены со входом буферного усилителя 20 и корректирующим конденсатором 21, предусмотрены новые элементы и связи – между эмиттером второго 3 входного транзистора и эмиттером первого 2 входного транзистора включен первый 22 дополнительный конденсатор, а между эмиттером третьего 5 входного транзистора и эмиттером четвертого 6 входного транзистора включен второй 23 дополнительный конденсатор.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа.

На чертеже фиг. 2 представлена схема заявляемого ОУ в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 показана схема заявляемого ОУ в соответствии с п. 2 и п. 3 формулы изобретения.

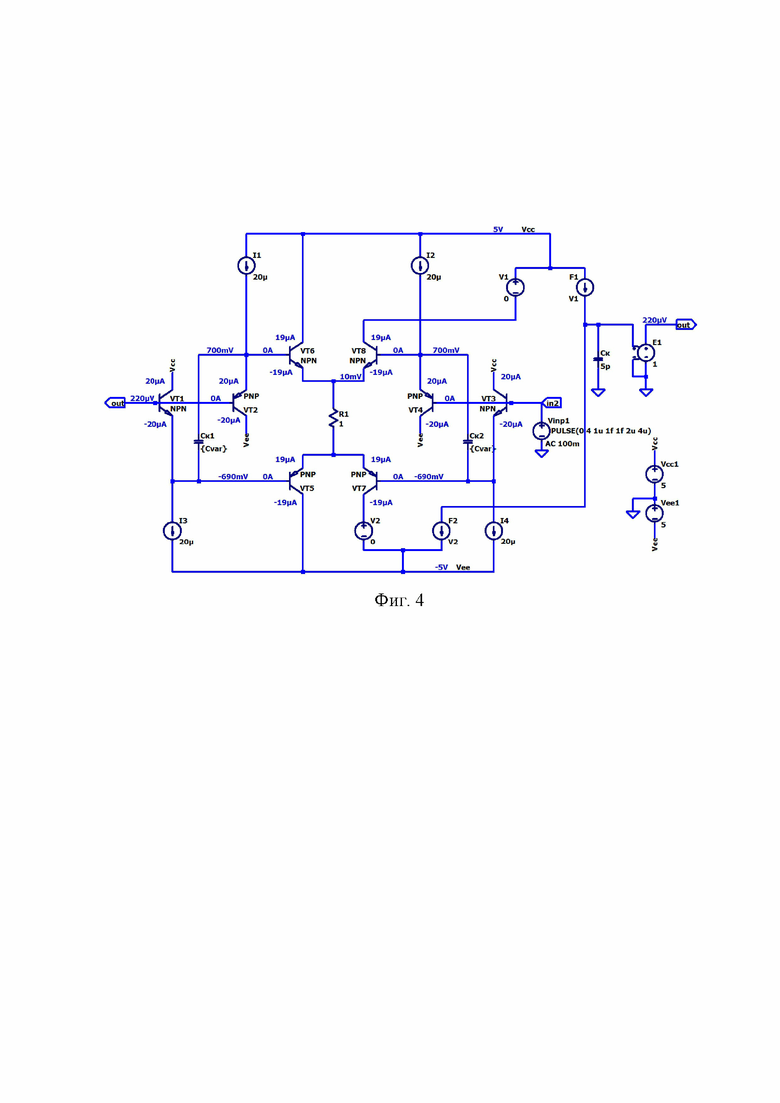

На чертеже фиг. 4 приведен статический режим заявляемого ОУ фиг. 2 в среде LTspice при t= 27oC, Ск=С21=5пФ, R1=1Ом, I1=I2=I3=I4=20мкА, Vсс= -Vee=5 В.

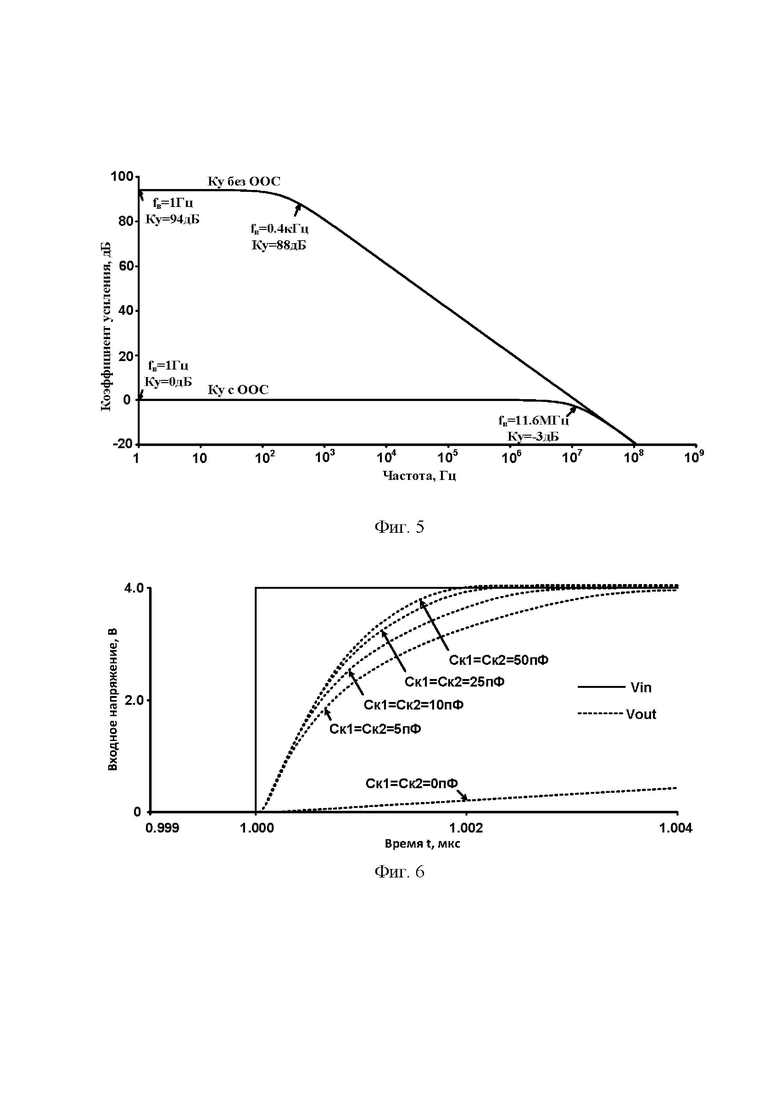

На чертеже фиг. 5 показана логарифмическая амплитудно-частотная характеристика ОУ фиг. 4 в среде LTspice при t= 27oC, Ск1=С22=Ск2=С23=0пФ, Ск=С21=5пФ, R1=1Ом, I1=I2= I3= I4=20мкА, Vсс= -Vee=5 В.

На чертеже фиг. 6 представлен передний фронт переходного процесса ОУ фиг. 4 в среде LTspice, при t= 27oC, разных значениях емкостей дополнительных конденсаторов 22 и 23 (Ск1=С22=Ск2=С23=0пФ; 5пФ; 10пФ; 25пФ; 50пФ), Ск=С21=5пФ, R1=1Ом, I1=I2= I3= I4=20мкА, Vсс= -Vee=5 В.

На чертеже фиг. 7 (мелкий масштаб) приведен задний фронт переходного процесса ОУ фиг.4 в среде LTspice при t= 27oC, разных значениях емкостей первого22 и второго 23 дополнительных конденсаторов (Ск1=С22=Ск2=С23=0пФ; 5пФ; 10пФ; 25пФ; 50пФ), Ск=С21=5пФ, R1=1Ом, I1=I2= I3= I4=20мкА, Vсс= -Vee=5 В.

На чертеже фиг. 8 (крупный масштаб) показан задний фронт переходного процесса ОУ фиг. 4 в среде LTspice при t= 27oC, разных значениях емкостей первого22 и второго 23 дополнительных конденсаторов (Ск1=С22=Ск2=С23=0пФ; 5пФ; 10пФ; 25пФ; 50пФ), Ск=С21=5пФ, R1=1Ом, I1=I2= I3= I4=20мкА, Vсс= -Vee=5 В.

Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения фиг. 2 содержит первый 1 вход, связанный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход, связанный с базами третьего 5 и четвертого 6 входных транзисторов, коллекторы первого 2 и четвертого 6 входных транзисторов согласованы с первой 7 шиной источника питания, а коллекторы второго 3 и третьего 5 входных транзисторов согласованы со второй 8 шиной источника питания, эмиттер первого 2 входного транзистора связан со второй 8 шиной источника питания через первый 9 токостабилизирующий двухполюсник и подключен к базе первого 10 транзистора промежуточного каскада, эмиттер четвертого 6 входного транзистора связан со второй 8 шиной источника питания через второй 11 токостабилизирующий двухполюсник и подключен к базе второго 12 транзистора промежуточного каскада, эмиттер второго 3 входного транзистора связан с первой 7 шиной источника питания через третий 13 токостабилизирующий двухполюсник и подключен к базе третьего 14 транзистора промежуточного каскада, эмиттер третьего 5 входного транзистора соединен с первой 7 шиной источника питания через четвертый 15 токостабилизирующий двухполюсник и подключен к базе четвертого 16 транзистора промежуточного каскада, между объединенными эмиттерами третьего 14 и четвертого 16 транзисторов промежуточного каскада и объединенными эмиттерами первого 10 и второго 12 транзисторов промежуточного каскада включен ограничивающий резистор 17, коллектор третьего 14 транзистора промежуточного каскада согласован с первой 7 шиной источника питания, коллектор первого 10 транзистора промежуточного каскада согласован со второй 8 шиной источника питания, коллектор четвертого 16 транзистора промежуточного каскада подключен ко входу первого 18 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор второго 12 транзистора промежуточного каскада подключен ко входу второго 19 токового зеркала, согласованного со второй 8 шиной источника питания, выходы первого 18 и второго 19 токовых зеркал соединены со входом буферного усилителя 20 и корректирующим конденсатором 21. Между эмиттером второго 3 входного транзистора и эмиттером первого 2 входного транзистора включен первый 22 дополнительный конденсатор, а между эмиттером третьего 5 входного транзистора и эмиттером четвертого 6 входного транзистора включен второй 23 дополнительный конденсатор.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, последовательно с первым 22, а также вторым 23 дополнительными конденсаторами включены соответствующие первый 24 и второй 25 согласующие резисторы.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, объединенные эмиттеры третьего 14 и четвертого 16 транзисторов промежуточного каскада связаны со второй 8 шиной источника питания через первый 26 вспомогательный токостабилизирующий двухполюсник, а объединенные эмиттеры первого 10 и второго 12 транзисторов промежуточного каскада связаны с первой 7 шиной источника питания через второй 27 вспомогательный токостабилизирующий двухполюсник.

Рассмотрим работу ОУ фиг.2.

Статический режим ОУ фиг. 2 обеспечивается первым 9, вторым 11, третьим 13 и четвертым 15 токостабилизирующими двухполюсниками. В большинстве случаев для снижения энергопотребления и уменьшения входных токов данные токи приходится выбирать в диапазоне десятков микроампер. Статический режим рассматриваемого ОУ представлен на чертеже фиг. 4.

ОУ-прототип фиг. 1, несмотря на потенциальные возможности, не обеспечивает повышенные значения SR из-за влияния инерционности входных повторителей напряжения на первом 2, втором 3, третьем 5 и четвертом 6 входных транзисторах, которые во многом зависят от топологических норм используемых технологических процессов.

В соответствии с п. 3 формулы изобретения (фиг. 3) введение первого 26 и второго 27 вспомогательных токостабилизирующих двухполюсников рекомендуется для установления заданных статических режимов третьего 14, четвертого 16 и первого 10, второго 12 транзисторов промежуточного каскада при повышенных значениях сопротивления ограничивающего резистора 17.

Существенное повышение SR от уровня 72 В/мкс до уровня 3000 В/мкс в схеме фиг. 2 обеспечивается за счет введения первого 22 и второго 23 дополнительных конденсаторов. Об этом свидетельствуют графики переходных процессов фиг. 6, фиг. 7, фиг. 8, а также данные таблицы 1.

Таблица 1 - Значение SR при разных значениях емкостей первого 22 и второго 23 дополнительных конденсаторов (Ск1=С22=Ск2=С23=0пФ;5пФ;10пФ;25пФ;50пФ), Ск=С21=5пФ, R1=1Ом, I1=I2= I3= I4=20мкА

Следовательно, введение первого 22 и второго 23 дополнительных конденсаторов повышает быстродействие ОУ более чем в 40 раз при использовании освоенных в России, а также в рамках Союзного государства технологических процессов. Первый 24 и второй 25 согласующие резисторы позволяют управлять численными значениями SR в широких пределах.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения замкнутого ОУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483

3. Матавкин В.В. Быстродействующие операционные усилители. – М.: Радио и связь, 1989, рис. 4.16

4. Патент US 3.668.538, fig. 1, 1972 г.

5. Патент RU 2319290, фиг. 1, 2008 г.

6. Патент US 5140074, fig. 1, 1992 г.

7. Патент US 6437645, fig. 1, 2002 г.

8. Патент US 5343164, fig. 2, fig. 3, 1994 г.

9. Патент US 6600343, fig. 1, 2003 г.

10. Патент US 5374897, fig.4, 1994 г.

11. Linear & Data Acquisition Products // Harris Semiconductor Analog Products, Volume 1, 1977, pp. 2-59: HA-2700/2704/2705. URL: http://www.bitsavers.org/components/harris/1977_Harris_Linear_and_Data_Acquisition_Products_Volume_1.pdf

12. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983. – С. 115, рис. 3.27

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2811071C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2802049C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2626667C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

Изобретение относится к радиоэлектронике. Технический результат - обеспечение повышенных значений максимальной скорости нарастания выходного напряжения операционного усилителя в режиме большого сигнала и уменьшение времени установления переходного процесса. Для этого в схеме операционного усилителя с повышенной максимальной скоростью нарастания выходного напряжения между эмиттером второго (3) входного транзистора и эмиттером первого (2) входного транзистора включен первый (22) дополнительный конденсатор, а между эмиттером третьего (5) входного транзистора и эмиттером четвертого (6) входного транзистора включен второй (23) дополнительный конденсатор. 2 з.п. ф-лы, 8 ил., 1 табл.

1. Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения, содержащий первый (1) вход, связанный с базами первого (2) и второго (3) входных транзисторов, второй (4) вход, связанный с базами третьего (5) и четвертого (6) входных транзисторов, коллекторы первого (2) и четвертого (6) входных транзисторов согласованы с первой (7) шиной источника питания, а коллекторы второго (3) и третьего (5) входных транзисторов согласованы со второй (8) шиной источника питания, эмиттер первого (2) входного транзистора связан со второй (8) шиной источника питания через первый (9) токостабилизирующий двухполюсник и подключен к базе первого (10) транзистора промежуточного каскада, эмиттер четвертого (6) входного транзистора связан со второй (8) шиной источника питания через второй (11) токостабилизирующий двухполюсник и подключен к базе второго (12) транзистора промежуточного каскада, эмиттер второго (3) входного транзистора связан с первой (7) шиной источника питания через третий (13) токостабилизирующий двухполюсник и подключен к базе третьего (14) транзистора промежуточного каскада, эмиттер третьего (5) входного транзистора соединен с первой (7) шиной источника питания через четвертый (15) токостабилизирующий двухполюсник и подключен к базе четвертого (16) транзистора промежуточного каскада, между объединенными эмиттерами третьего (14) и четвертого (16) транзисторов промежуточного каскада и объединенными эмиттерами первого (10) и второго (12) транзисторов промежуточного каскада включен ограничивающий резистор (17), коллектор третьего (14) транзистора промежуточного каскада согласован с первой (7) шиной источника питания, коллектор первого (10) транзистора промежуточного каскада согласован со второй (8) шиной источника питания, коллектор четвертого (16) транзистора промежуточного каскада подключен к входу первого (18) токового зеркала, согласованного с первой (7) шиной источника питания, коллектор второго (12) транзистора промежуточного каскада подключен к входу второго (19) токового зеркала, согласованного со второй (8) шиной источника питания, выходы первого (18) и второго (19) токовых зеркал соединены со входом буферного усилителя (20) и корректирующим конденсатором (21), отличающийся тем, что между эмиттером второго (3) входного транзистора и эмиттером первого (2) входного транзистора включен первый (22) дополнительный конденсатор, а между эмиттером третьего (5) входного транзистора и эмиттером четвертого (6) входного транзистора включен второй (23) дополнительный конденсатор.

2. Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения по п. 1, отличающийся тем, что последовательно с первым (22), а также вторым (23) дополнительными конденсаторами включены соответствующие первый (24) и второй (25) согласующие резисторы.

3. Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения по пп. 1 и 2, отличающийся тем, что объединенные эмиттеры третьего (14) и четвертого (16) транзисторов промежуточного каскада связаны со второй (8) шиной источника питания через первый (26) вспомогательный токостабилизирующий двухполюсник, а объединенные эмиттеры первого (10) и второго (12) транзисторов промежуточного каскада связаны с первой (7) шиной источника питания через второй (27) вспомогательный токостабилизирующий двухполюсник.

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| US 5225791 A1, 06.07.1993. | |||

Авторы

Даты

2023-12-27—Публикация

2023-10-09—Подача