Изобретение относится к области обработки цифровых данных с помощью электронных устройств, а именно к способам распределения данных по многофункциональным блокам, предназначенных для процессоров со сверхдлинной командной строкой {Very Long Instruction Word {VLIW), Explicitly Parallel Instruction Computing (EPIC)) и может быть использовано для сокращения времени обработки цифровых данных процессорами VLIW и EPIC.

Известен способ автоматического распараллеливания программ, заключающийся в том, что в алгоритмической части программы предварительно получают граф потока управления, дерево доминаторов, дерево циклов, граф потока данных; выполняют подстановки промежуточного представления процедур в места вызовов; выполняют межпроцедурный анализ потока данных; для обнаружения эквивалентных операций выполняют анализ потока данных, предпочтительно способом нумераций значений; выполняют анализ переменных цикла на инвариантность и индуктивность; выполняют анализ операций доступа в массивы, строят индексы доступа в массивы в виде канонических форм сумм произведений; выполняют слияния циклов; выполняют вынос инвариантных условий; изменяют порядок обхода итерационного пространства циклов; выполняют анализ параллельных циклов [1].

Известен способ построения программы, заключающийся в определении в исходном коде программы на ассемблере помеченные циклы и классифицируют их на несколько предопределенных типов, выравнивают адреса начала помеченных циклов, если это требуется для цикла данного типа путем добавления ассемблерных инструкций и, сохраняя исходный код на ассемблере в памяти, строят путем компиляции и компоновки модифицированный ассемблерный код для устройства назначения [2].

Недостатками данных способов являются отсутствие учета конкретной архитектуры процессора и отсутствие учета параметра времени работы многофункциональных блоков процессора.

Одним из возможных путей повышения эффективности обработки данных является организация распределения данных процессов в многофункциональных блоках процессора. Однако при распределении данных программы в многофункциональных блоках возникают проблемы временной синхронизации, что приводит к снижению эффективности цифровой обработки данных, что необходимо учитывать при выборе моментов времени начала выполнения операторов при параллельном выполнении исходной программы.

Цель изобретения - повысить эффективность цифровой обработки данных (снизить время обработки данных) за счет оптимизации равномерности загрузки многофункциональных блоков процессора.

Указанная цель достигается способом распределения данных по многофункциональным блокам процессора со сверхдлинной командной строкой, заключающимся в выполнении следующих процедур:

1. Загрузка последовательного кода программы в виде нумерованных последовательностей длинных команд, каждая длинная команда включает тип операции, адрес первого операнда, адрес второго операнда и адрес результата, и множество длинных команд включает подмножество взаимно независимых операторов исходной программы с установленными соответствиями каждому оператору момента начала и длительности его реализации определенному временному шагу и распределенными операторами, имеющими одинаковое значение параметра начала реализации, на соответствующий временной шаг, чем больше длительность выполнения операции, тем раньше операция должна начать выполнение, и при наличии первого и второго операндов определены как команды, готовые к выполнению.

2. Загрузка выполняемых длинных команд для хранения.

3. Передача операндов для распределения между многофункциональными блоками исполнительного устройства для параллельного выполнения.

4. Распределение операндов между многофункциональными блоками исполнительного устройства и передача для параллельного выполнения.

5. Выполнение операций, получение результатов и передача результатов выполнения для определения наличии первого и второго операндов и готовности к выполнению следующих длинных команд, для распределения множества результатов выполнения длинной команды в интересах выполнения следующей длинной команды, для хранения всех данных при решении задачи.

6. Определение при наличии первого и второго операндов команд готовых к выполнению и распределение операндов между многофункциональными блоками исполнительного устройства и передача для параллельного выполнения.

7. Выполнение многофункциональными блоками исполнительного устройства операций и получение результата выполнения параллельной программы с временной параметризацией и передача результата для записи.

Таким образом, для повышения эффективности цифровой обработки данных (снижения времени обработки данных) следует разработать временные нити программы с учетом требования оптимизации равномерности загрузки многофункциональных блоков в процессе параллельного решения задачи, тем самым обеспечить необходимую временную синхронизацию многофункциональных блоков процессора.

Новыми признаками, обладающими существенными отличиями, являются:

1. Учет архитектуры процессора со сверхдлинной командной строкой.

2. Учет параметра времени начала выполнения инструкций параллельного алгоритма в многофункциональных блоках процессора со сверхдлинной командной строкой.

Данные признаки обладают существенными отличиями, так как в известных способах не обнаружены.

Применение новых признаков, в совокупности с известными позволит повысить эффективность цифровой обработки данных за счет оптимизации равномерности загрузки многофункциональных блоков процессора в процессе параллельного решения задачи.

Способ распределения данных по многофункциональным блокам процессора со сверхдлинной командной строкой реализуется следующим образом.

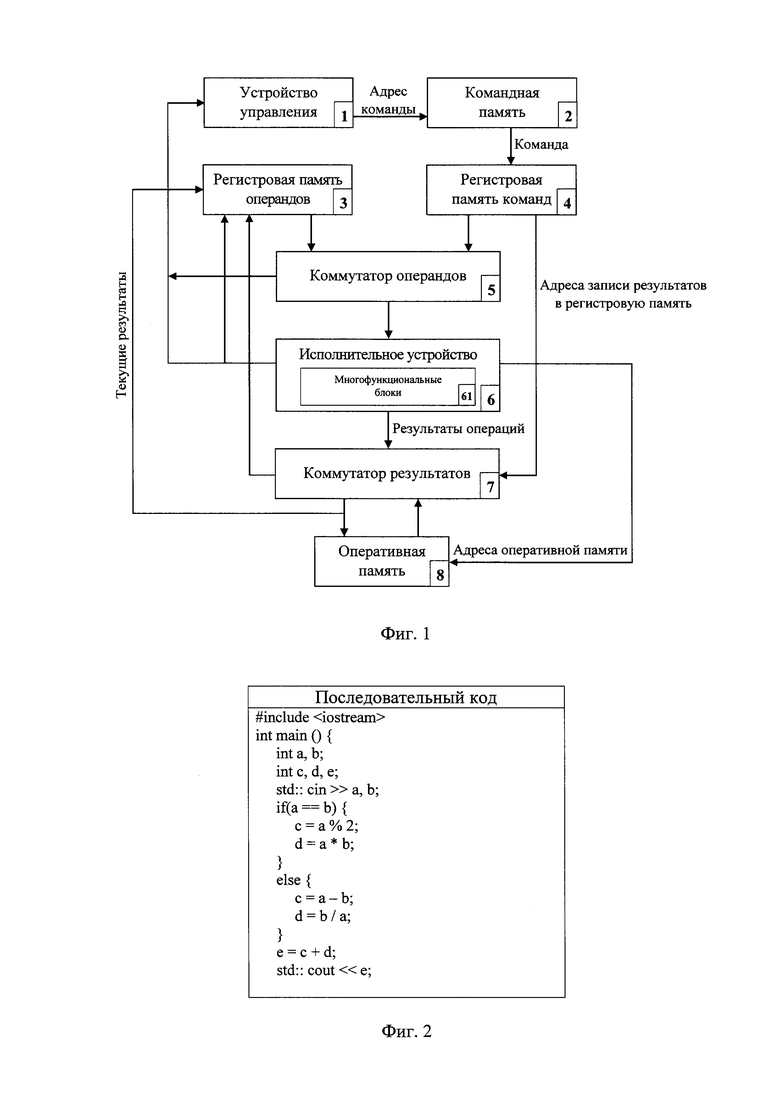

На фиг. 1 показана схема основных компонентов процессора со сверхдлинной командной строкой состоящего из устройства управления 1, командной памяти 2, регистровой памяти операндов 3, регистровой памяти команд 4, коммутатора операндов 5, исполнительного устройства 6, включающего многофункциональные блоки 61, коммутатора результатов 7 и оперативной памяти 8, которые реализует предложенный способ. Устройство управления 1 обеспечивает управление обработкой данных и передачей команд в командную память 2 в которой хранится исходный последовательный код программы в виде конечного числа длинных команд, каждая из которых включает тип операции, адрес первого операнда, адрес второго операнда и адрес результата. Регистровая память команд 4 получает выполняемые длинные команды от командной памяти 2 и обеспечивает хранение этих команд программы, управляет коммутатором операндов 5 при распределении операндов между многофункциональными блоками 61 исполнительного устройства 6 и управляет коммутатором результатов 7 при записи результатов операций в регистровую память операндов 3 и оперативную память 8. Регистровая память операндов 3 обеспечивает прием из исполнительного устройства 6 результатов вычислений или выдачу в исполнительное устройство 6 множества операндов (исходных данных и текущих результатов) для операций, входящих в конкретную длинную команду программы. Оперативная память 8 обеспечивает хранение всех используемых при решении задач данных. Исполнительное устройство 6 представляет собой набор многофункциональных блоков 61. Многофункциональные блоки 61 представляют собой операционные блоки, выполняющие арифметические и логические операции над поданными на вход операндами. Коммутатор операндом 5 обеспечивает распределение данных, считываемых из регистровой памяти операндов 3 между блоками исполнительного устройства 6. Коммутатор результатов 7 обеспечивает распределение множества результатов выполнения длинной команды между регистрами памяти операндов 3 для выполнения следующей длинной команды программы.

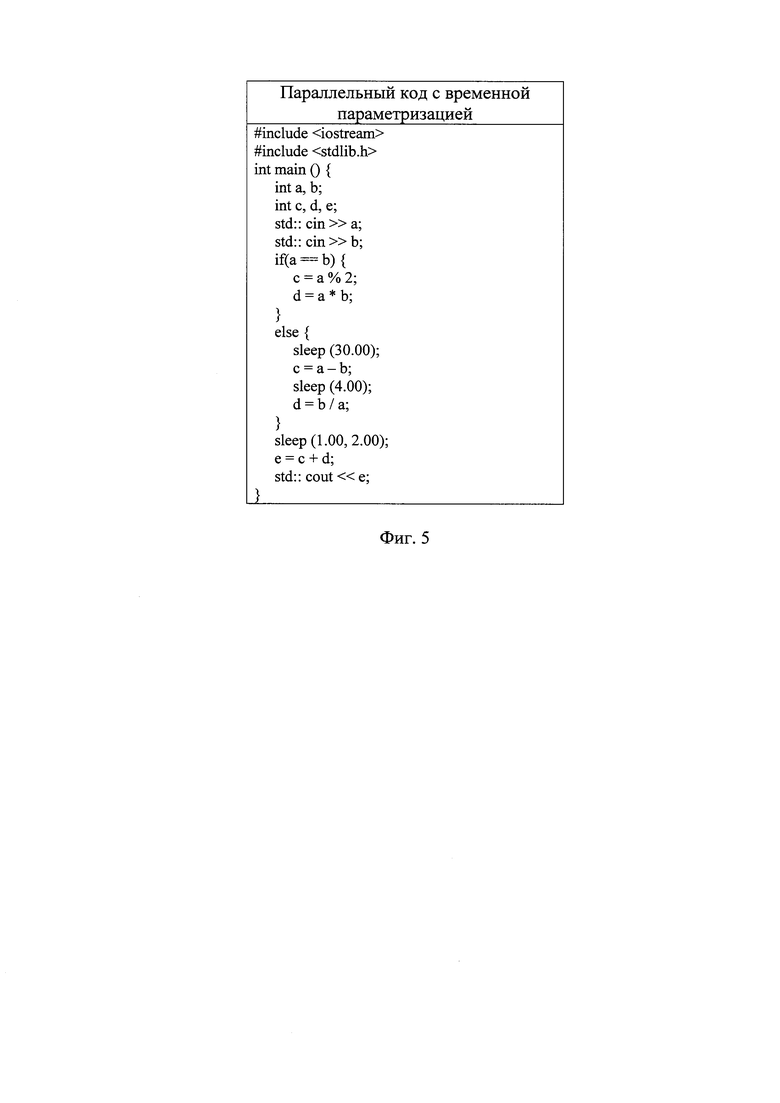

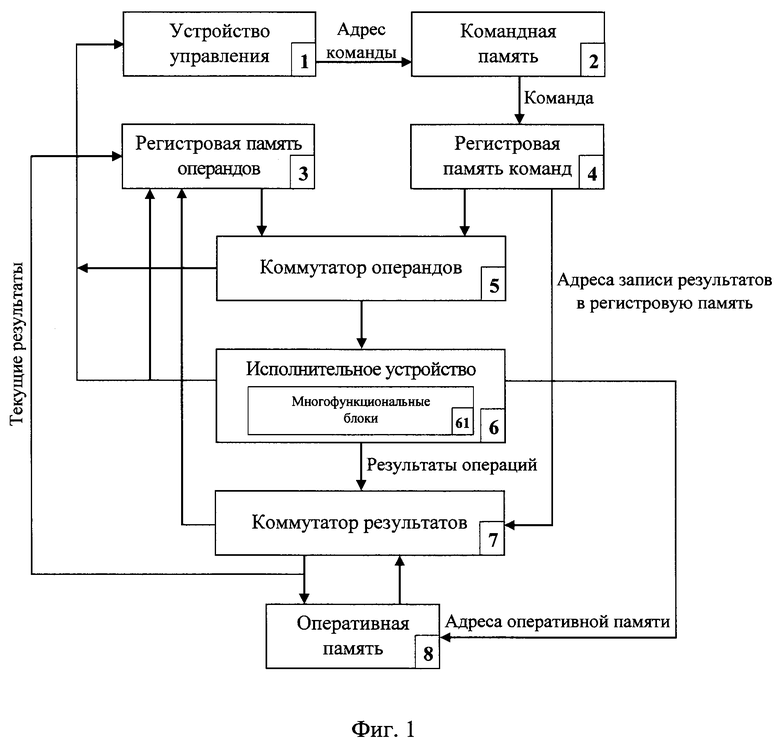

Рассмотрим пошаговое выполнение предложенного способа в описанной выше системе (фиг. 1). Загрузка устройством управления 1 в командную память 2 для хранения последовательного кода программы (фиг. 2) в виде нумерованных последовательностей длинных команд, каждая длинная команда включает тип операции, адрес первого операнда, адрес второго операнда и адрес результата, и множество длинных команд включает подмножество взаимно независимых операторов исходной программы с установленными соответствиями каждому оператору момента начала и длительности его реализации определенному временному шагу (фиг. 3) и распределенными операторами, имеющими одинаковое значение параметра начала реализации, на соответствующий временной шаг (фиг. 4), чем больше длительность выполнения операции, тем раньше операция должна начать выполнение, и при наличии первого и второго операндов определены как команды, готовые к выполнению (шаг 1). Загрузка из командной памяти 2 в регистровую память команд 4 выполняемых длинных команд для хранения (шаг 2). Передача операндов из регистровой памяти команд 4 в коммутатор операндов 5 для распределения между многофункциональными блоками 61 исполнительного устройства 6 для параллельного выполнения (шаг 3). Распределение операндов коммутатором операндов 5 между многофункциональными блоками 61 исполнительного устройства 6 и передача для параллельного выполнения (шаг 4). Выполнение многофункциональными блоками 61 исполнительного устройства 6 операций, получение результатов и передача результатов выполнения в устройство управления 1 для определения наличии первого и второго операндов и готовности к выполнению следующих длинных команд, коммутатор результатов 7 для распределения множества результатов выполнения длинной команды между регистрами регистровой памяти операндов 3 в интересах выполнения следующей длинной команды, и оперативную память 8 для хранения всех данных при решении задачи (шаг 5). Определение устройством управления 1 при наличии первого и второго операндов команд готовых к выполнению и передача операндов посредством командной памяти 2 и регистровой памяти команд 4 в коммутатор операндов 5, а также передача операндов из регистровой памяти операндов 3 в коммутатор операндов 5 и распределение операндов коммутатор операндов 5 между многофункциональными блоками 61 исполнительного устройства 6 и передача для параллельного выполнения (шаг 6). Выполнение многофункциональными блоками 61 исполнительного устройства 6 операций и получение результата выполнения параллельной программы с временной параметризацией и передача результата для записи в оперативную память 8 (шаг 7). Ниже приведен пример созданного параллельного кода с временной параметризацией (фиг. 5).

Таким образом, предлагаемый способ позволит снизить время обработки данных на многофункциональных блоках процессора до 9% при распределении данных по многофункциональным блокам процессора со сверхдлинной командной строкой, то есть повысить эффективность цифровой обработки данных за счет оптимизации равномерности загрузки многофункциональных блоков процессора в процессе параллельного решения задачи.

Источники информации

1. Дроздов А.Ю., Новиков С.В. Способ автоматического распараллеливания программ. Патент на изобретение № 2411569, бюл. № 4, 2011 г. (аналог).

2. Яковлев С.В., Сафонов И.В., Быкова Т.В. Способ построения программы. Патент на изобретение № 2406112, бюл. № 34, 2010 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ распределения данных по монофункциональным блокам процессора с управлением потоком данных | 2024 |

|

RU2818497C1 |

| Способ распределения данных по монофункциональным блокам процессоров вычислительной системы с управлением потоком данных | 2024 |

|

RU2820032C1 |

| Способ временной синхронизации работы массивно-параллельной вычислительной системы с распределенной памятью | 2022 |

|

RU2815189C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительный модуль и способ обработки с использованием такого модуля | 2018 |

|

RU2689433C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОСТАДИЙНОЙ МНОГОПОТОЧНОЙ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ И СПОСОБ ОБРАБОТКИ С ИСПОЛЬЗОВАНИЕМ ДАННОГО МОДУЛЯ | 2018 |

|

RU2681365C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в сокращении времени обработки цифровых данных процессорами со сверхдлинной командной строкой. Технический результат достигается за счет выполнения многофункциональными блоками исполнительного устройства операций, получения результатов и передачи результатов выполнения в устройство управления для определения наличия первого и второго операндов и готовности к выполнению следующих длинных команд, коммутатор результатов для распределения множества результатов выполнения длинной команды между регистрами регистровой памяти операндов в интересах выполнения следующей длинной команды и оперативную память для хранения всех данных при решении задачи; определения устройством управления при наличии первого и второго операндов команд, готовых к выполнению, и передачи операндов посредством командной памяти и регистровой памяти команд в коммутатор операндов, а также передачи операндов из регистровой памяти операндов в коммутатор операндов и распределения операндов коммутатором операндов между многофункциональными блоками исполнительного устройства и передачи для параллельного выполнения; выполнения многофункциональными блоками исполнительного устройства операций и получения результата выполнения параллельной программы с временной параметризацией и передачи результата для записи в оперативную память. 5 ил.

Способ распределения данных по многофункциональным блокам процессора со сверхдлинной командной строкой, заключающийся в том, что для реализации способа устройствами процессора выполняются следующие операции:

загрузка устройством управления в командную память для хранения последовательного кода программы в виде нумерованных последовательностей длинных команд, каждая длинная команда включает тип операции, адрес первого операнда, адрес второго операнда и адрес результата, а множество длинных команд включает подмножество взаимно независимых операторов исходной программы с установленными соответствиями каждому оператору момента начала и длительности его реализации определенному временному шагу и распределенными операторами, имеющими одинаковое значение параметра начала реализации, на соответствующий временной шаг, чем больше длительность выполнения операции, тем раньше операция должна начать выполнение, и при наличии первого и второго операндов определены как команды, готовые к выполнению;

загрузка из командной памяти в регистровую память команд выполняемых длинных команд для хранения;

передача операндов из регистровой памяти команд в коммутатор операндов для распределения между многофункциональными блоками исполнительного устройства для параллельного выполнения;

распределение операндов коммутатором операндов между многофункциональными блоками исполнительного устройства и передача для параллельного выполнения;

выполнение многофункциональными блоками исполнительного устройства операций, получение результатов и передача результатов выполнения в устройство управления для определения наличия первого и второго операндов и готовности к выполнению следующих длинных команд, коммутатор результатов для распределения множества результатов выполнения длинной команды между регистрами регистровой памяти операндов в интересах выполнения следующей длинной команды и оперативную память для хранения всех данных при решении задачи;

определение устройством управления при наличии первого и второго операндов команд, готовых к выполнению, и передача операндов посредством командной памяти и регистровой памяти команд в коммутатор операндов, а также передача операндов из регистровой памяти операндов в коммутатор операндов и распределение операндов коммутатором операндов между многофункциональными блоками исполнительного устройства и передача для параллельного выполнения;

выполнение многофункциональными блоками исполнительного устройства операций и получение результата выполнения параллельной программы с временной параметризацией и передача результата для записи в оперативную память.

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| СИСТЕМА ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ И СПОСОБ РАБОТЫ СИСТЕМЫ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2559723C2 |

| Способ распараллеливания программ на графическом процессоре вычислительной машины | 2022 |

|

RU2803581C1 |

Авторы

Даты

2024-05-02—Публикация

2024-02-27—Подача