Изобретение относится к радиоэлектронике и может быть использовано (при реализации на широкозонных полупроводниках SiC, GaN, GaAs и др.) в высокотемпературных устройствах автоматики и вычислительной техники [1-15].

В настоящее время в современных микроэлектронных операционных усилителях применяются схемы входных каскадов, в которых для повышения максимальной скорости нарастания выходного напряжения (SR) в режиме большого сигнала предусмотрено (во время фронта переходного процесса) существенное увеличение выходных токов входного дифференциального каскада [16-18]. Данные схемотехнические решения повышают SR ОУ для многих существующих технологических процессов до уровня средних значений (SR=200-400 В/мкс), однако не позволяют получить предельно возможные SRmax из-за влияния паразитных емкостей (Ср1, Ср2) в цепи баз выходных транзисторов промежуточного каскада и задержек сигнала в токовых зеркалах.

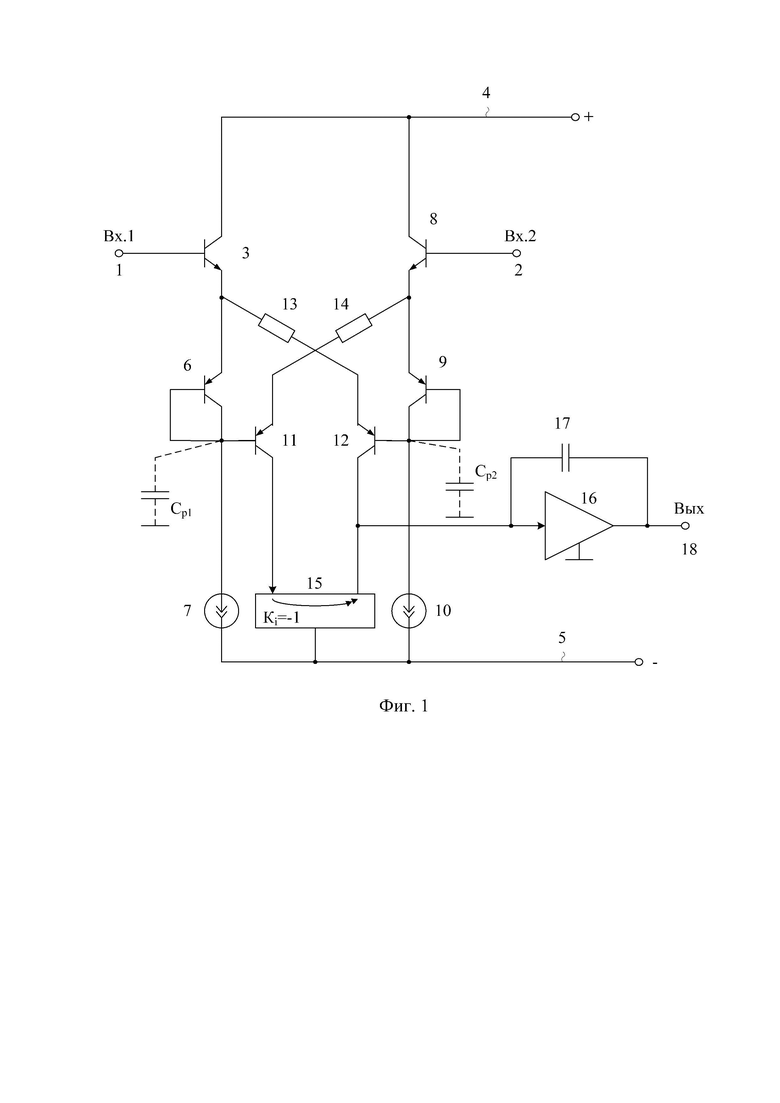

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту US 3668538, 1972 г. Он содержит (фиг. 1) первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные первый 6 p-n переход на биполярном транзисторе и первый 7 источник опорного тока, второй 8 входной транзистор, база которого подключена ко второму 2 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные второй 9 p-n переход на биполярном транзисторе и второй 10 источник опорного тока, первый 11 выходной транзистор, база которого соединена с первым 7 источником опорного тока, а коллектор согласован со второй 5 шиной источника питания, второй 12 выходной биполярный транзистор, база которого соединена со вторым 10 источником опорного тока, первый 13 и второй 14 токоограничивающие резисторы, первое 15 токовое зеркало, согласованное со второй 5 шиной источника питания, выходной буферный усилитель 16, вход которого соединен с выходом первого 15 токового зеркала и корректирующим конденсатором 17, причем выход буферного усилителя 16 является потенциальным выходом устройства 18.

Существенный недостаток известного ОУ на чертеже фиг. 1, например, при его неинвертирующем включении, состоит в том, что он не обеспечивает (при использовании многих технологических процессов (Si, GaN, GaAs, SiC), освоенных российскими и зарубежными предприятиями) получение предельно возможных для данной архитектуры значений SRmax для отрицательных импульсных входных сигналов. Это обусловлено влиянием паразитных емкостей Ср1, Ср2 в цепи баз выходных транзисторов 6 и 12 промежуточного каскада. Повысить SR(-) здесь можно за счет применения более дорогостоящих технологических процессов, например, SiGe, уменьшающих Ср1 и Ср2.

Основная задача предлагаемого изобретения состоит в дальнейшем увеличении максимальной скорости нарастания выходного напряжения отрицательного фронта с уровня 200-400 В/мкс до уровня 12000 В/мкс без ужесточения требований к технологическим нормам процесса его изготовления для Si, GaN, GaAs, SiC. Это позволит выпускать быстродействующие ОУ по имеющимся в России технологиям с одинаковыми значениями SR для положительных и отрицательных импульсных сигналов большой амплитуды SR(+)≈SR(-). Кроме этого, данное схемотехническое решение при его практической реализации на широкозонных полупроводниках (SiC, GaN, GaAs и др.) [1-15] может быть использовано в высокотемпературных устройствах радиотехники, автоматики и вычислительной техники.

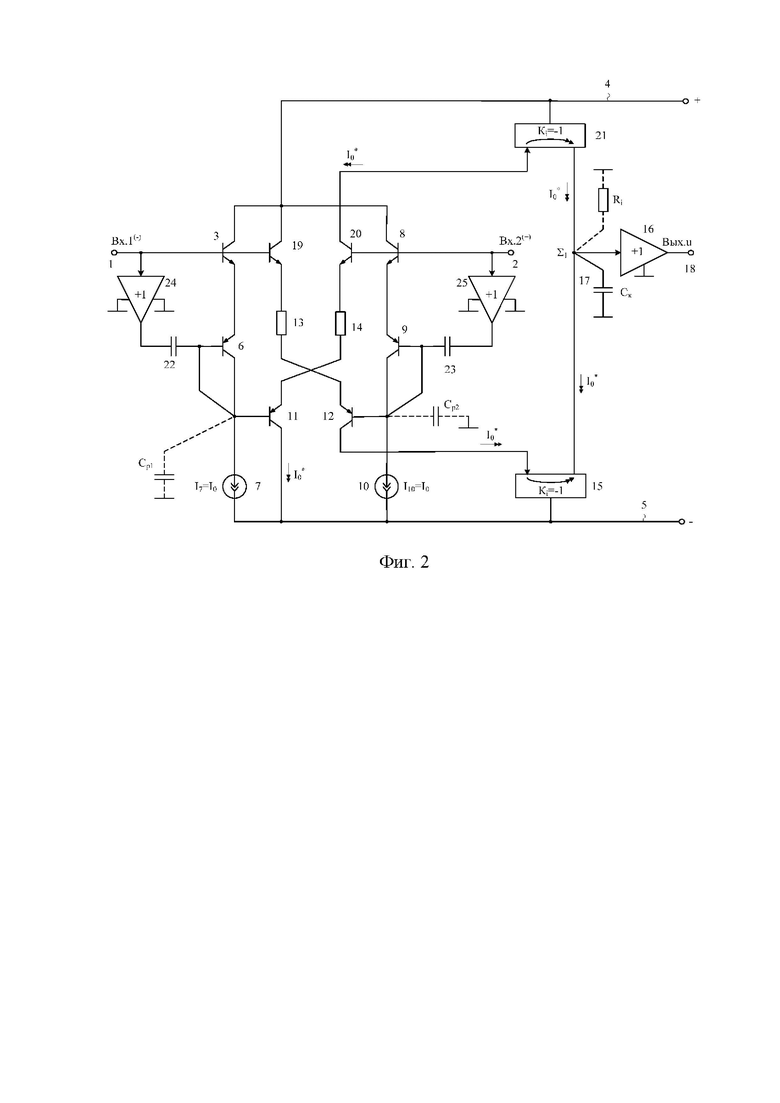

Поставленная задача достигается тем, что в дифференциальном операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные первый 6 p-n переход на биполярном транзисторе и первый 7 источник опорного тока, второй 8 входной транзистор, база которого подключена ко второму 2 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные второй 9 p-n переход на биполярном транзисторе и второй 10 источник опорного тока, первый 11 выходной транзистор, база которого соединена с первым 7 источником опорного тока, а коллектор согласован со второй 5 шиной источника питания, второй 12 выходной биполярный транзистор, база которого соединена со вторым 10 источником опорного тока, первый 13 и второй 14 токоограничивающие резисторы, первое 15 токовое зеркало, согласованное со второй 5 шиной источника питания, выходной буферный усилитель 16, вход которого соединен с выходом первого 15 токового зеркала и корректирующим конденсатором 17, причем выход буферного усилителя 16 является потенциальным выходом устройства 18, предусмотрены новые элементы и связи - в схему введены первый 19 и второй 20 дополнительные транзисторы, базы которых соединены с соответствующими первым 1 и вторым 2 входами устройства, коллектор первого 19 дополнительного транзистора подключен к первой 4 шине источника питания, коллектор второго 20 дополнительного транзистора соединен со входом дополнительного 21 токового зеркала, согласованного с первой 4 шиной источника питания, выход первого 15 токового зеркала соединен с выходом дополнительного 21 токового зеркала и подключен ко входу буферного усилителя 16, эмиттер первого 19 дополнительного транзистора соединен с эмиттером второго 12 выходного биполярного транзистора через первый 13 токоограничивающий резистор, эмиттер второго 20 дополнительного транзистора соединен с эмиттером первого 11 выходного транзистора через второй 14 токоограничивающий резистор, первый 1 вход устройства связан с базой первого 11 выходного биполярного транзистора через первый 22 дополнительный корректирующий конденсатор, а вход 2 устройства соединен с базой второго 12 выходного биполярного транзистора через второй 23 дополнительный корректирующий конденсатор, причем между первым 1 входом устройства и первым 22 дополнительным корректирующим конденсатором включен первый 24 дополнительный буферный усилитель, а между вторым 2 входом устройства и вторым 23 дополнительным корректирующим конденсатором включен второй 25 дополнительный буферный усилитель, кроме этого, первый 24 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на первом 26 вспомогательном транзисторе, эмиттер которого связан с первой 4 шиной источника питания через первый 27 вспомогательный источник опорного тока, а второй 25 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на втором 28 вспомогательном транзисторе, эмиттер которого соединен с первой 4 шиной источника питания через второй 29 вспомогательный источник опорного тока, причем коллекторы первого 26 и второго 28 вспомогательных транзисторов согласованы со второй 5 шиной источника питания.

На чертеже фиг. 1 показана схема операционного усилителя-прототипа по патенту US 3668538, 1972 г.

На чертеже фиг. 2 приведена схема заявляемого быстродействующего ОУ, в которую введены дополнительные буферные усилители 24 и 25, однако не показана их схемотехническая реализация.

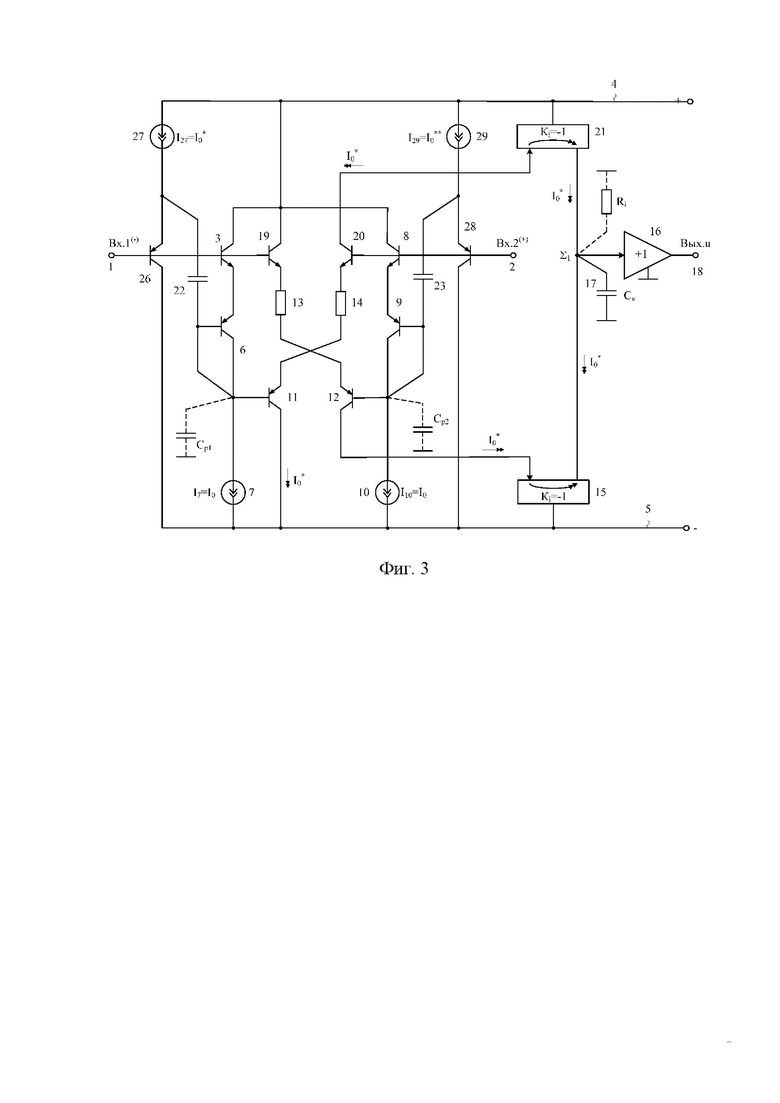

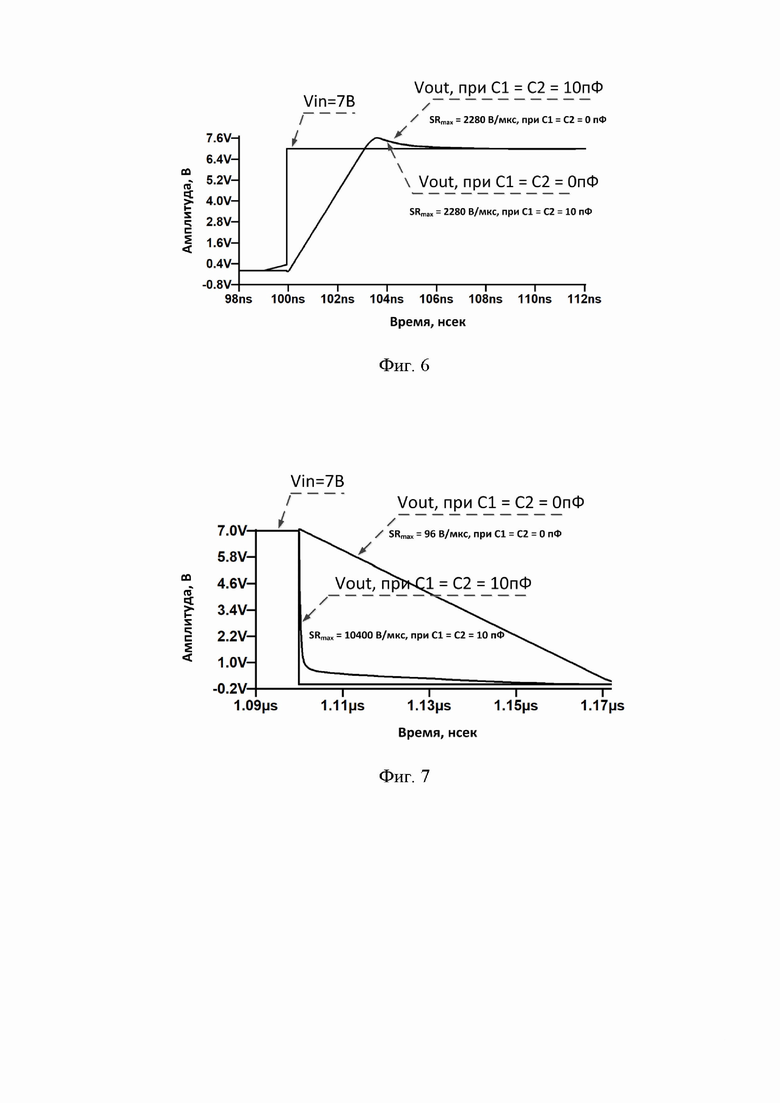

На чертеже фиг. 3 показана схема заявляемого быстродействующего ОУ (фиг.2) с конкретным выполнением буферного усилителя 24 на первом 26 вспомогательном транзисторе и первом 27 источнике опорного тока, а также конкретным выполнением второго 25 дополнительного буферного усилителя на втором вспомогательном транзисторе 28 и втором 29 источник опорного тока.

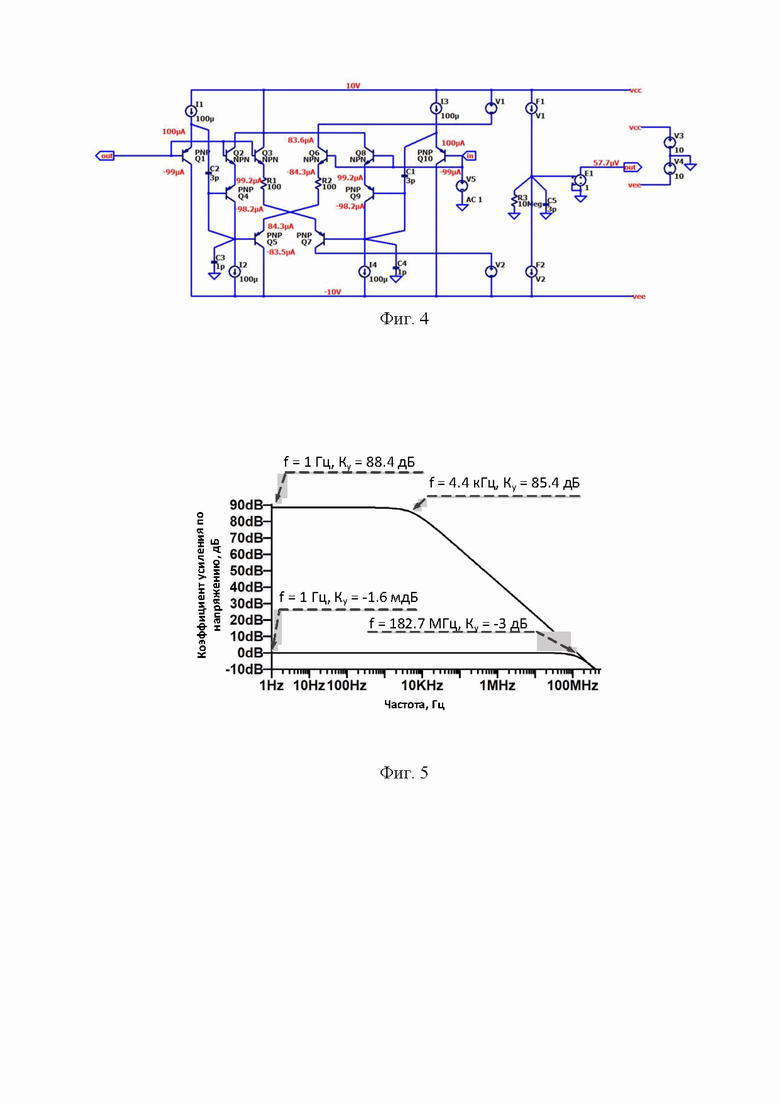

На чертеже фиг. 4 представлен статический режим транзисторов быстродействующего ОУ на чертеже фиг. 3 при R1÷R2=100 Ом, I1÷I4=100 мкА, T=27°C.

На чертеже фиг. 5 приведена амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ на чертеже фиг. 4 при R1÷R2=100 Ом, C1÷C2=3 пФ, C3÷C4=1 пФ, I1÷I4=100 мкА.

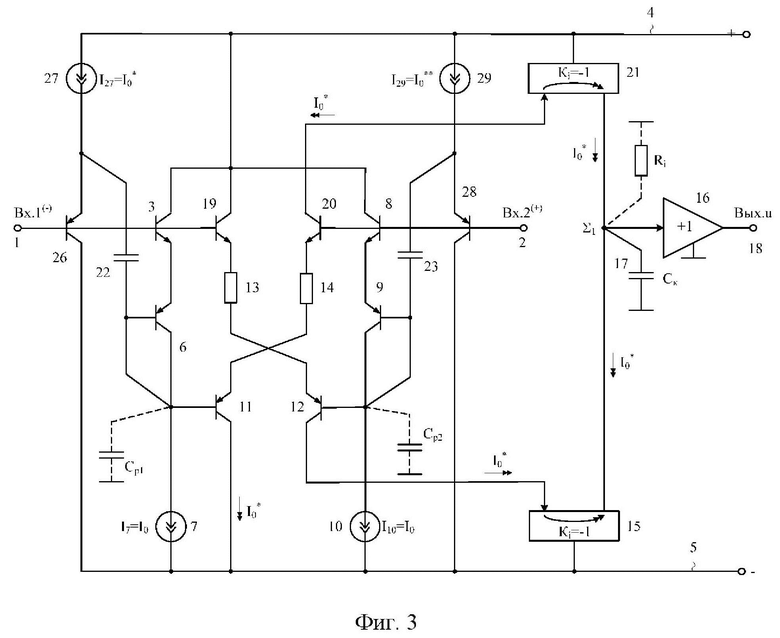

На чертеже фиг. 6 показан передний фронт переходного процесса в ОУ на чертеже фиг. 4 при C1=С2=0÷10 пФ.

На чертеже фиг. 7 представлен задний фронт переходного процесса в ОУ на чертеже фиг. 4 при C1=С2 = 0÷10 пФ.

Быстродействующий дифференциальный операционный усилитель на комплементарных биполярных транзисторах фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные первый 6 p-n переход на биполярном транзисторе и первый 7 источник опорного тока, второй 8 входной транзистор, база которого подключена ко второму 2 входу устройства, коллектор соединен с первой 4 шиной источника питания, а эмиттер связан со второй 5 шиной источника питания через последовательно соединенные второй 9 p-n переход на биполярном транзисторе и второй 10 источник опорного тока, первый 11 выходной транзистор, база которого соединена с первым 7 источником опорного тока, а коллектор согласован со второй 5 шиной источника питания, второй 12 выходной биполярный транзистор, база которого соединена со вторым 10 источником опорного тока, первый 13 и второй 14 токоограничивающие резисторы, первое 15 токовое зеркало, согласованное со второй 5 шиной источника питания, вход которого соединен с коллектором второго 12 выходного биполярного транзистора, выходной буферный усилитель 16, вход которого соединен с выходом первого 15 токового зеркала и корректирующим конденсатором 17, причем выход буферного усилителя 16 является потенциальным выходом устройства 18. В схему введены первый 19 и второй 20 дополнительные транзисторы, базы которых соединены с соответствующими первым 1 и вторым 2 входами устройства, коллектор первого 19 дополнительного транзистора подключен к первой 4 шине источника питания, коллектор второго 20 дополнительного транзистора соединен со входом дополнительного 21 токового зеркала, согласованного с первой 4 шиной источника питания, выход первого 15 токового зеркала соединен с выходом дополнительного 21 токового зеркала и подключен ко входу буферного усилителя 16, эмиттер первого 19 дополнительного транзистора соединен с эмиттером второго 12 выходного биполярного транзистора через первый 13 токоограничивающий резистор, эмиттер второго 20 дополнительного транзистора соединен с эмиттером первого 11 выходного транзистора через второй 14 токоограничивающий резистор, первый 1 вход устройства связан с базой первого 11 выходного биполярного транзистора через первый 22 дополнительный корректирующий конденсатор, а вход 2 устройства соединен с базой второго 12 выходного биполярного транзистора через второй 23 дополнительный корректирующий конденсатор, причем между первым 1 входом устройства и первым 22 дополнительным корректирующим конденсатором включен первый 24 дополнительный буферный усилитель, а между вторым 2 входом устройства и вторым 23 дополнительным корректирующим конденсатором включен второй 25 дополнительный буферный усилитель, кроме этого, первый 24 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на первом 26 вспомогательном транзисторе, эмиттер которого связан с первой 4 шиной источника питания через первый 27 вспомогательный источник опорного тока, а второй 25 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на втором 28 вспомогательном транзисторе, эмиттер которого соединен с первой 4 шиной источника питания через второй 29 вспомогательный источник опорного тока, причем коллекторы первого 26 и второго 28 вспомогательных транзисторов согласованы со второй 5 шиной источника питания.

На чертеже фиг. 3 показана схема заявляемого быстродействующего ОУ (фиг.2) с конкретным выполнением первого 24 дополнительного буферного усилителя на первом 26 вспомогательном транзисторе и первом 27 источнике опорного тока, а также конкретным выполнением второго 25 дополнительного буферного усилителя на втором вспомогательном транзисторе 28 и втором 29 источник опорного тока.

На чертеже фиг. 4 первый 24 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на первом 26 вспомогательном транзисторе, эмиттер которого связан с первой 4 шиной источника питания через первый 27 вспомогательный источник опорного тока, а второй 25 дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на втором 28 вспомогательном транзисторе, эмиттер которого соединен с первой 4 шиной источника питания через второй 29 вспомогательный источник опорного тока, причем коллекторы первого 26 и второго 28 вспомогательных транзисторов согласованы со второй 5 шиной источника питания.

Рассмотрим работу предлагаемого ОУ на чертеже фиг. 3 при отрицательном импульсном входном сигнале большой амплитуды на неинвертирующем входе Вх.2(+) при 100% отрицательной обратной связи. В таком режиме паразитный конденсатор Ср2 достаточно быстро перезаряжается большим импульсным током через второй 23 дополнительный корректирующий конденсатор, который создается по эмиттерной цепи второго 28 вспомогательного транзистора. Как показывают экспериментальные исследования на чертеже фиг. 7, за счет рационального выбора емкости второго 23 дополнительного корректирующего конденсатора максимальная скорость нарастания выходного напряжения для отрицательного фронта переходного процесса увеличивается с SRmax(-)=96В/мкс до SRmax(-)=10400 В/мкс.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения и может быть использовано при производстве аналоговых микросхем как на основе кремния (Si), так и на основе широкозонных полупроводников (GaN, GaAs, SiC) для высокотемпературных применений.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Hedayati R. et al. A monolithic, 500 C operational amplifier in 4H-SiC bipolar technology // IEEE Electron Device Letters. - 2014. - Т. 35. - №. 7. - С. 693-695.

2. Tian Y., Zetterling C.M. High frequency characteristic of a monolithic 500° C OpAmp-RC integrator in SiC bipolar IC technology //Solid-State Electronics. - 2017. - Т. 135. - С. 65-70.

3. Kargarrazi S., Lanni L., Zetterling C.M. A study on positive-feedback configuration of a bipolar SiC high temperature operational amplifier //Solid-State Electronics. - 2016. - Т. 116. - С. 33-37.

4. Tian Y. et al. Silicon carbide fully differential amplifier characterized up to 500° C // IEEE Transactions on Electron Devices. - 2016. - Т. 63. - №. 6. - С. 2242-2247.

5. Bimbi C. et al. Single-Branch Wide-Swing-Cascode Subthreshold GaN Monolithic Voltage Reference // Electronics. - 2022. - Т. 11. - №. 12. - С. 1840.

6. Hassan A. et al. Circuit Techniques in GaN Technology for High-Temperature Environments // Electronics. - 2021. - Т. 11. - №. 1. - С. 42.

7. Hassan A. et al. GaN-based LSK demodulators for wireless data receivers in high-temperature applications // Microelectronics Journal. - 2019. - Т. 84. - С. 129-135.

8. Nomoto K., Hasegawa K., Nakamura T. High-temperature operation of GaN-based OPAMP on silicon substrate // physica status solidi c. - 2010. - Т. 7. - №. 7-8. - С. 1952-1954.

9. A GaN-Based Wireless Monitoring System for High-Temperature Applications / A. Hassan [et al] // Sensors. - 2019. - 19(8). - P. 1785-1802.

10. Дворников О.В. и др. Особенности проектирования зарядочувствительных усилителей на арсенид-галлиевом базовом кристалле // Доклады Белорусского государственного университета информатики и радиоэлектроники. - 2022. - Т. 20. - №. 5. - С. 57-64.

11. Дворников О.В. и др. Арсенид-галлиевый аналоговый базовый кристалл // Проблемы разработки перспективных микро-и наноэлектронных систем (МЭС). - 2021. - №. 2. - С. 47-54.

12. Morris F.J. et al. Integrated circuit composed of group III-V compound field effect and bipolar semiconductors: пат. 5068756 США. - 1991.

13. Yang J.Y. et al. GaAs BIJFET technology for linear circuits // 11th Annual Gallium Arsenide Integrated Circuit (GaAs IC) Symposium. - IEEE, 1989. - С. 341-344.

14. Kobayashi K.W. et al. Integrated complementary HBT microwave push-pull and Darlington amplifiers with pnp active loads // IEEE journal of solid-state circuits. - 1993. - Т. 28. - №. 10. - С. 1011-1017.

15. Тимошенков В.П. Интегральная схема синхронизатора на арсенид-галлиевых гетеропереходных биполярных транзисторах // Оборонный комплекс - научно-техническому прогрессу России. - 2006. - №. 2. - С. 44-50.

16. Патент US 3.668.538, фиг .1, 1972 г.

17. Матавкин В. Быстродействующие операционные усилители. - М: Радио и связь, 1989. - С. 75, рис. 4.16.

18. Патент US 5.343.164, фиг. 2/3, 1994 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2022 |

|

RU2784706C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2022 |

|

RU2790616C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2659476C1 |

Изобретение относится к радиоэлектронике и может быть использовано в высокотемпературных устройствах автоматики и вычислительной техники. Техническим результатом изобретения является увеличение максимальной скорости нарастания выходного напряжения отрицательного фронта до уровня 12000 В/мкс без ужесточения требований к технологическим нормам процесса его изготовления для Si, GaN, GaAs, SiC. Быстродействующий дифференциальный операционный усилитель на комплементарных биполярных транзисторах дополнительно содержит первый (19) и второй (20) дополнительные транзисторы, дополнительное (21) токовое зеркало, первый (22) и второй (23) дополнительные корректирующие конденсаторы, первый (24) и второй (25) дополнительные буферные усилители, первый (26) и второй (28) вспомогательные транзисторы, первый (27) и второй (29) вспомогательные источники опорного тока. 7 ил.

Быстродействующий дифференциальный операционный усилитель на комплементарных биполярных транзисторах, содержащий первый (1) и второй (2) входы устройства, первый (3) входной транзистор, база которого подключена к первому (1) входу устройства, коллектор соединен с первой (4) шиной источника питания, а эмиттер связан со второй (5) шиной источника питания через последовательно соединенные первый (6) p-n переход на биполярном транзисторе и первый (7) источник опорного тока, второй (8) входной транзистор, база которого подключена ко второму (2) входу устройства, коллектор соединен с первой (4) шиной источника питания, а эмиттер связан со второй (5) шиной источника питания через последовательно соединенные второй (9) p-n переход на биполярном транзисторе и второй (10) источник опорного тока, первый (11) выходной транзистор, база которого соединена с первым (7) источником опорного тока, а коллектор согласован со второй (5) шиной источника питания, второй (12) выходной биполярный транзистор, база которого соединена со вторым (10) источником опорного тока, первый (13) и второй (14) токоограничивающие резисторы, первое (15) токовое зеркало, согласованное со второй (5) шиной источника питания, вход которого соединен с коллектором второго (12) выходного биполярного транзистора, выходной буферный усилитель (16), вход которого соединен с выходом первого (15) токового зеркала и корректирующим конденсатором (17), причем выход буферного усилителя (16) является потенциальным выходом устройства (18), отличающийся тем, что в схему введены первый (19) и второй (20) дополнительные транзисторы, базы которых соединены с соответствующими первым (1) и вторым (2) входами устройства, коллектор первого (19) дополнительного транзистора подключен к первой (4) шине источника питания, коллектор второго (20) дополнительного транзистора соединен со входом дополнительного (21) токового зеркала, согласованного с первой (4) шиной источника питания, выход первого (15) токового зеркала соединен с выходом дополнительного (21) токового зеркала и подключен ко входу буферного усилителя (16), эмиттер первого (19) дополнительного транзистора соединен с эмиттером второго (12) выходного биполярного транзистора через первый (13) токоограничивающий резистор, эмиттер второго (20) дополнительного транзистора соединен с эмиттером первого (11) выходного транзистора через второй (14) токоограничивающий резистор, первый (1) вход устройства связан с базой первого (11) выходного биполярного транзистора через первый (22) дополнительный корректирующий конденсатор, а вход (2) устройства соединен с базой второго (12) выходного биполярного транзистора через второй (23) дополнительный корректирующий конденсатор, причем между первым (1) входом устройства и первым (22) дополнительным корректирующим конденсатором включен первый (24) дополнительный буферный усилитель, а между вторым (2) входом устройства и вторым (23) дополнительным корректирующим конденсатором включен второй (25) дополнительный буферный усилитель, кроме этого, первый (24) дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на первом (26) вспомогательном транзисторе, эмиттер которого связан с первой (4) шиной источника питания через первый (27) вспомогательный источник опорного тока, а второй (25) дополнительный буферный усилитель выполнен на основе эмиттерного повторителя на втором (28) вспомогательном транзисторе, эмиттер которого соединен с первой (4) шиной источника питания через второй (29) вспомогательный источник опорного тока, причем коллекторы первого (26) и второго (28) вспомогательных транзисторов согласованы со второй (5) шиной источника питания.

| US 3668538 A, 06.06.1972 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2022 |

|

RU2784706C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| JOANN CLOSE High Speed Op Amps: Performance, Process and Topologies // IEEE Bipolar / BiCMOS Circuits and Technology Meeting (BCTM) | |||

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| WO 2016031120 A1, 03.03.2016 | |||

| Предохранительное устройство подъемника | 1980 |

|

SU901220A1 |

Авторы

Даты

2024-10-01—Публикация

2024-03-11—Подача