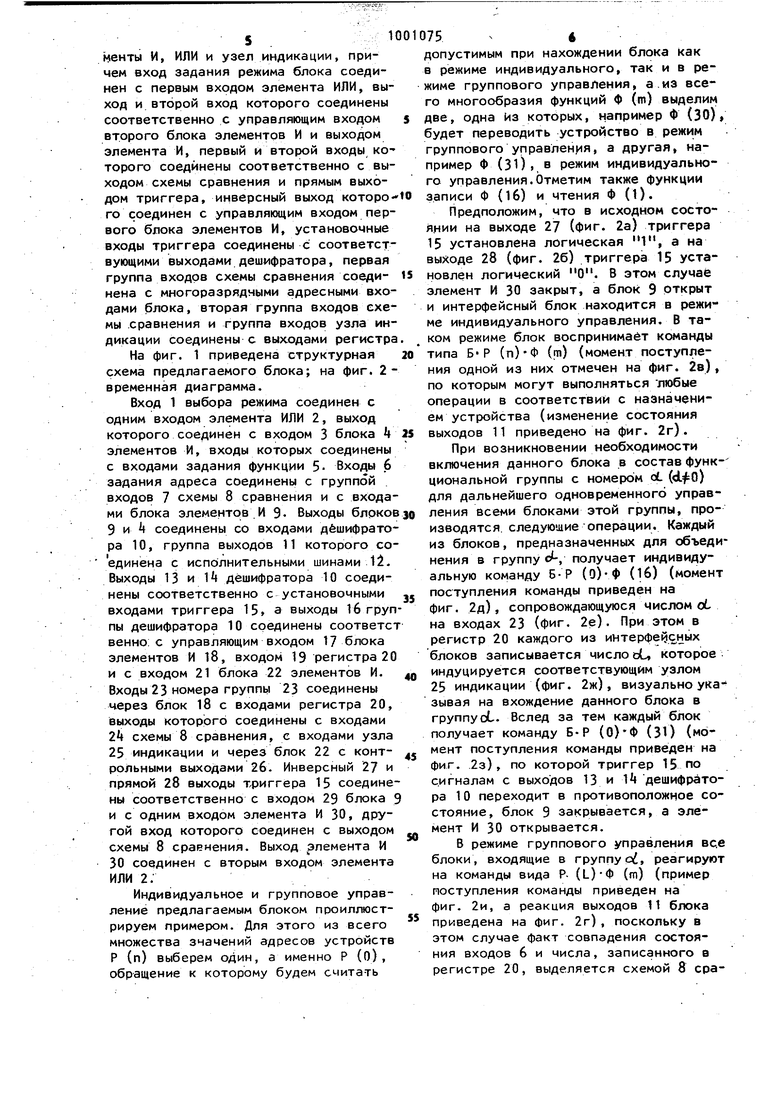

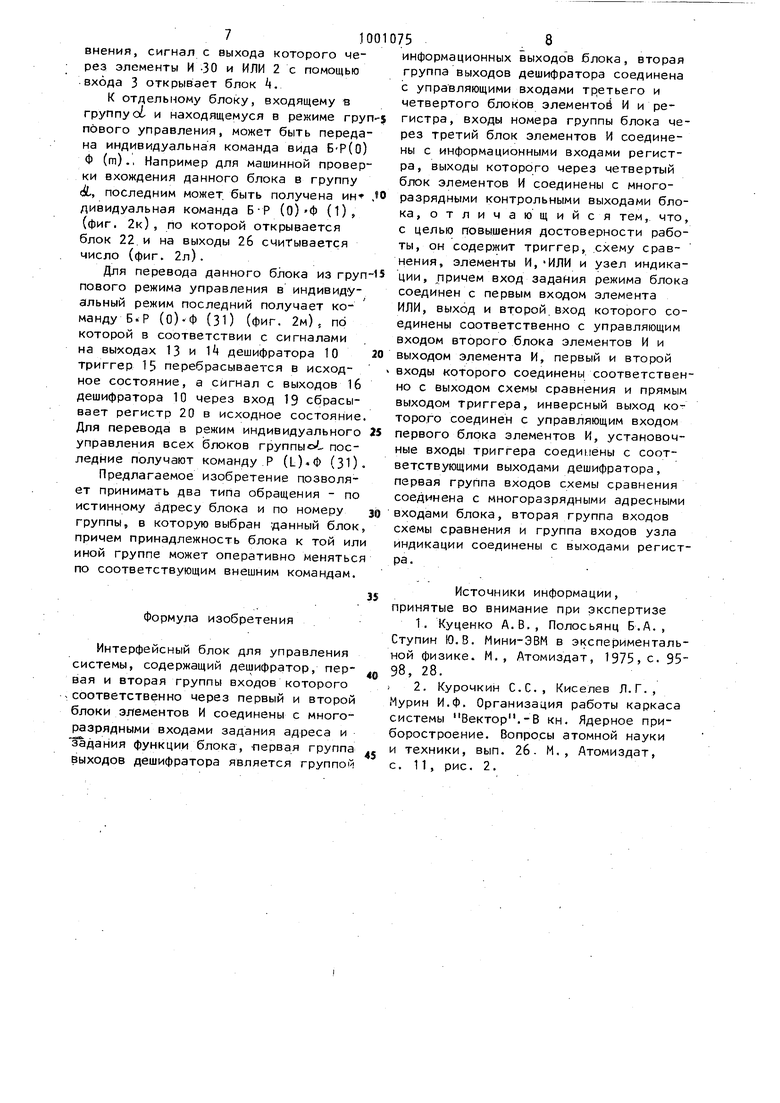

(5) ИНТЕРФЕЙСНЫЙ БЛОК ДЛЯ УПРАВЛЯЮЩЕЙ СИСТЕМЫ Изобретение относится к технической физике.и может быть использовано в составе многоканальных управляющих систем для обеспечения индивидуального и синхронного группового управления различными устройствами, например электрон+ными измерительно-управляющими модулями экспериментальных критических сборок при изучении переходных процессов. В этом случае возникает необходи- мость разбиения всей совокупности измерительно-управляющих модулей, обслуживающих органы регулирования критической сборки, на группы по их функ циональному назначению (группы собственно- управления, компенсации и аварийной защиты). Общее число модулей равно числу органов регулирования и для стенда В-1000 составляет 109 шт. Общее число групп, используемых в одном эксперименте, лежит в пределах 1-15. Число же модулей, включаемых в дйнную группу, а также их конкретные номера могут быть любыми и определяются из условий эксперимента в зависимости от типа исследуемой зоны. В процессе подготовки эксперимента информация в каждой из измерительно-управляющих модулей (исходные параметры, контрольные уставки и др.) в соответствии с намеченным разбиением на группы заносится индивидуально, причем в этом случае время получения данных каждым модулем не критично. При проведении же эксперимента все измерительно-управляющие модули должны управляться строго синхронно, поскольку временной разброс и временная неопределенность моментов поступления. управляющих сигналов накаждый из измерительно-управляющих модулей одной группы приводит к неоднозначности управления стендом и снижает достоверность получаемых результатов эксперимента. Известно устройство (Интерфейсная карта), содержащее декрдировщик адреса, вход которого соединен С шинами приема адреса. На декодировщик адреса поступают также с внешних шин стробирующие сигналы (10Р1, 10Р2, 10Р), вырабатываемые внешним управляющим устройством. Декодировщик адре са осуществляет сравнение адреса, поступающего на его адресный вход, с адресом устройства. Кроме того, устройство имеет схемы приема управляющих сигналовj буферный регистр и вентили связи с шинами данных. Декодировщик адреса и буферный регистр вырабатывают информацию для воздействия на внешние устройства (Код, Запуск).: Данное устройство является универсальньЫ, способно передавать машинные команды в любые внешние устройства. При использовании нескольких идентичных устройств в составе многоканальной управляющей системы управление ими осуществляется поочередноС1. Недостатком этого устройства являются его малые функциональные возможности, поскольку, требуя при всяком обращении к нему передачи адреса модуля, устройсхво не допускает группового управления. Наиболее близким к предлагаемому является устройство, содержащее шину выбора блока и дешифратор, входы управления которого через первую и вторую группы ключей соединены соответст венно с шинами выбора регистра в модуле и функции. Одна группа выходов дешифратора соединена с исполнительными шинами, другая группа выходов соединена с входами управления регист ра и третьей и четвертой групп ключей Шины записи через третью группу ключей соединены с входами- регистра, выход которого через четвертую группу ключей соединен с шинами чтения. Шина выбора блока в известном устройстве соединена с входами управления первой и второй групп ключей. Известное устройство предназначено для работы в номализованном каркасе, все позиции которого пронизанУ шинами записи чтения, выбора регистра и задания функции.. Шина выбора блока подводится от блока связи с ЭВМ к каж дой позиции каркаса индивидуально, поэтому oбpaщef иe к данному модулю зависит от его места в каркасе и имеет вид Б (j) Р (п) Ф (т), где Б (j) - позиция, занимаемая устройством в каркасе, Р (п) - адрес устройства, которому надлежит выполнить функцию Ф (т). Известное устройство получает команду в виде БР (п) |) (т), которая после расшифровки дешифратором порождает соответствующие сигналы на исполйительных шинах. Кроме того, известное устройство принимает ряд команд, по которым дешифратор открывает третью группу ключей и записывает информацию с шин записи в регистр для дальнейшего использования , а также ряд команд, по которым открывается четвертая группа ключей, и информация с регистра через шины чтения поступает во внешнее устройство. Таким образом, известное устройство является универсальным модулем, способным выполнять по индивидуальным командам большую номенклатуру операций.. При использовании нескольких таких устройств в составе многоканальной управляющей системы управление осущесвляется поочередно 2 3Недостатком известного устройства являются его малые функциональные « возможности, поскольку оно допускает только индивидуальное управление. Цель изобретения - повышение достоверности работы, расширение функциональных возможностей устройства путем обеспечения синхронного группового и индивидуального управления. Поставленная цель достигается тем, что в интерфейсный блок, содержащий дешифратор, входы управления которого соответственно через первый и второй блоки элементов И соединены с многоразрядными входами задания адреса и задания функции, первая группа выходов дешифратора является группой информационных выходов блока, вторая группа выходов дешифратора соединена с управляющими входами третьего и четвертого блоков элементов И и регистра, входы номера группы через третий блок элементов И соединены с информационными входами регистра, выходы которого через четвертый блок элементов И соединены с многоразрядными контрольными выходами блока, введены триггер, схема сравнения, менты И, ИЛИ и узел индикации, причем вход задания режима блока соединен с первым входом элемента ИЛИ, выход и второй вход которого соединены соответственно с управляющим входом второго блока элементов И и выходом элемента И, первый и второй входы которого соединены соответственно с выходом схемы сравнения и прямым выходом триггера, инверсный выход которого соединен с управляющим входом первого блока элементов И, установочные входы триггера соединены с соответствующими выходами дешифратора, первая группа входов схемы сравнения соединена с многоразрядными адресными входами блока, вторая группа входов схемы .сравнения и группа входов узла индикации соединены с выходами регистра На фиг. 1 приведена структурная схема предлагаемого блока; на фиг. 2временная диаграмма. Вход 1 выбора режима соединен с одним входом элемента ИЛИ 2, выход которого соединен с входом 3 блока k элементов И, входы которых соединены с входами задания функции 5- Входы 6 задания адреса соединены с группой входов 7 схемы 8 сравнения и с входами блока элементов И 9- Выходы блрков 9 и 4 соединены со входами дешифратора 10, группа выходов 11 которого соединена с исполнительными шинами 11, Выходы 13 и Ij дешифратора 10 соединены соответственно с установочными входами триггера 15 а выходы 16 груп пы дешифратора 10 соединены соответст венно: с управляющим входом 17 блока элементов И 18, входом 19 регистра 20 и с входом 21 блока 22 элементов И. Входы 23 номера группы 23 соединены через блок 18 с входами регистра 20, выходы которого соединены с входами 24схемы 8 сравнения, с входами узла 25индикации и через блок 22 с контрольными выходами 2б. Инверсный 27 и прямой 28 выходы триггера 15 соединены соответственно с входом 29 блока 9 и с одним входом элемента И 30, другой вход которого соединен с выходом схемы 8 сравнения. Выход элемента И 30 соединен с вторым входом элемента ИЛИ 2. Индивидуальное и групповое управление предлагаемым блоком проиллюстрируем примером. Для этого из всего множества значений адресов устройств Р (п) выберем один, а именно Р (О), обращение к которому будем считать 75 4 допустимым при нахождении блока как в режиме индивидуального, так и в режиме группового управления, а.из всего многообразия функций Ф (т) выделим две, одна из которых, например Ф (ЗО), будет переводить устройство в режим группового управления, а другая, например Ф (31) , в режим индивидуального управления.Отметим также функции записи Ф (16) и чтения Ф (1). Предположим, что в исходном состоянии на выходе 27 (фиг. 2а) триггера 15 установлена логическая 1, а на выходе 28 (фиг. 2б) триггера 15 установлен логический О. В этом случае элемент И 30 закрыт, а блок 9 открыт и интерфейсный блок находится в режи ме индивидуального управления. В таком режиме блок воспринимает команды типа БР (п)-Ф (т) (момент поступления одной из них отмечен на фиг. 28), по которым могут выполняться любые операции в соответствии с назначением устройства (изменение состояния выходов 11 приведено на фиг. 2г). При возникновении необходимости включения данного блока в состав функциональной группы с номером oL (dfО) для дальнейшего одновременного управления всеми блоками этой группы, производятся, следующие операции. Каждый из блоков, предназначенных для объединения в группу , получает индивидуальную команду Б-Р (0)-Ф (16) (момент поступления команды приведен на фиг. 2д), сопровождающуюся числом oL на входах 23 (фиг. 2е). При этом в регистр 20 каждого из интерфе сных блоков записывается число oU которое индуцируется соответствующим узлом 25 индикации (фиг. 2ж), визуально указывая на вхождение данного блока в группуoL. Вслед за тем каждый блок получает команду Б-Р (0)Ф (ЗО (момент поступления команды приведен на фиг. 2з), по которой триггер 15 по сигналам с выходов 13 и 14 дешифратора 10 переходит в противоположное состояние, блок 9 закрывается, а элемент И 30 открывается. В режиме группового управления все блоки, входящие в группу oi, реагируют на команды вида Р- (1)-ф (т) (пример поступления команды приведен на фиг. 2и, а реакция выходов 11 блока приведена на фиг. 2г), поскольку в этом случае факт совпадения состояния входов 6 и числа, записанного в регистре 20, выделяется схемой 8 ера710внения, сигнал с выхода которого через элементы И -30 и ИЛИ 2 с помощью входа 3 открывает блок 4, К отдельному блоку, входящему в группу oi- и находящемуся в режиме гру пового управления, может быть передана индивидуальная команда вида БР(О) Ф (т)., Например для машинной проверки вхождения данного блока в группу ciL, последним может, быть получена ин дивидуальная команда Б-Р (о)«Ф (1), (фиг. 2к), по которой открывается блок 22. и на выходы 2б считывается число (фиг. 2л). Для перевода данного блока из груп пового режима управления в индивидуальный режим последний получает команду Б.Р (0)-Ф (31) (фиг. 2м), по которой в соответствии с сигналами на выходах 13 и дешифратора 10 триггер 15 перебрасывается в исходное состояние, а сигнал с выходов 16 дешифратора 10 через вход 19 сбрасывает регистр 20 в исходное состояние Для перевода в режим индивидуального управления всех блоков группы , последние получают команду Р (1)«Ф (31) Предлагаемое изобретение позволяет принимать два типа обращения - по истинному адресу блока и по номеру группы, в которую выбран данный блок причем принадлежность блока к той или иной группе может оперативно меняться по соответствующим внешним командам. Формула изобретения Интерфейсный блок для управления системы, содержащий дешифратор, первая и вторая группы входов которого соответственно через первый и второй блоки элементов И соединены с многоразрядными входами задания адреса и задания функции блока, первая группа выходов дешифратора является группой 5 8 информационных выходов блока, вторая группа выходов дешифратора соединена с управляющими входами третьего и четвертого блоков элементов И и регистра, входы номера группы блока через третий блок элементов И соединены с информационными входами регистра, выходы которого через четвертый блок элементов И соединены с многоразрядными контрольными выходами блока, отличающийся тем, что, с целью повышения достоверности работы, он содержит триггер, .схему сравнения, элементы И,ИЛИ и узел индикации, причем вход задания режима блока соединен с первым входом элемента ИЛИ, выход и второй.Вход которого соединены соответственно с управляющим входом второго блока элементов И и выходом элемента И, первый и второй входы которого соединены соответственно с выходом схемы сравнения и прямым выходом триггера, инверсный выход которо.го соединен с управляющим входом первого блока элементов И, установочные входы триггера соединены с соответствующими выходами дешифратора, первая группа входов схемы сравнения соединена с многоразрядными адресными входами блока, вторая группа входов схемы сравнения и группа входов узла индикации соединены с выходами регистра. Источники информации, принятые во внимание при экспертизе 1. Куценко А.В., Полосьянц Б.А., Ступин Ю,В. Мини-ЭВМ в экспериментальной физике. М., Атомиздат, 1975, с. 95 98, 28. 2. Курочкин С.С., Киселев Л.Г., Мурин И.Ф. Организация работы каркаса системы Вектор.-В кн. Ядерное приборостроение. Вопросы атомной науки и техники, вып. 26- М., Атомиздат, с. 11, рис. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для централизованного управления вычислительной системой | 1987 |

|

SU1674146A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Интерфейсный блок | 1983 |

|

SU1120311A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012035C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения модулей вычислительной системы с общей шиной | 1984 |

|

SU1179357A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

Авторы

Даты

1983-02-28—Публикация

1981-10-12—Подача