гистра, выход которого соединен с входом дешифратора второй вход шестого элемента И соединен с единичным входом первого триггера, второй вход первого регистра соединен с выходом

1179357

шестого элемента И, выход первого элемента И соединен с единичным входом третьего триггера, нулевой выход которого соединен с третьим входом второго элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1472910A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для обмена информацией | 1988 |

|

SU1536395A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией | 1985 |

|

SU1278872A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МОДУЛЕЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ С ОБЩЕЙ ШИНОЙ, содержащее элемент ИЛИ, дешифратор, первый триггер, первый элемент И, первый блок сравнения и первый регистр, причем группа выходов дешифратора образует информационный выход устройства, первый вход первого блока сравнения соединен с первым входом первого регистра и является информационным входом устройства, выход элемента ИЛИ является выходом записи устройства, первый выход дешифратора соединен с единичным входом первого триггера, нулевой вход которого соединен с вторым выходом дешифраторе, выход первого регистра соединен с вторым входом первого блока сравнения, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, отличающееся тем, что, с целью повьш1ения быстро действия, в-него введены второй блок сравнения, второй регистр, одновибратор, два триггера и семь элементов И, причем первый вход второго регистра соединен с первым входом второго блока сравнения и первым входом первого регистра, второй вход второго блока сравнения является входом задания адреса устройства, вход одновибратора соединен с вторым входом второго регистра и нулевым входом второго триггера и является входом обмена устройства, выход второго элемента И является выходом чтения устройства, нулевой вход третьего триггера соединен с первым входом третьего элемента И и является входом ответа устройства, первый вход второго элемента И соединен с § выходом четвертого элемента И и является входом чтения данных устройства, выход третьего элемента И соединен .с первым входом пятого элемента И и является выходом ответа устройства, первый вход шестого элемента И соединен с первым входом седьмого элемента И и является входом записи данных устройства, выход второго блока сравнения соединен с первым входом восьмого элемента И, второй вход которого соединен с выходом :л одновибратора, третьим входом первоК го элемента И и первым входом четвертого элемента И, второй вход которого соединен с единичным выходом треть-его триггера ft вторым входом пятого элемента И, выход которого соединен с первым входом элемен а ИЛИ, второй вход которого соединен с выходом седьмого элемента И, второй вход которого соединен с вторыми входами второго и третьего элементов И и выходом второго 1риггера, единичный вход которого соединен с выходом восьмого элемента И и третьим входом второго ре

Изобретение относится к вычислительной технике и может быть использовано для обмена информацией между мoдyля 0i вычислительной системы с общей шиной, в частности, по интерфейсу межмодульному МПИ (ОСТ 11 305.903-80).

Цель изобретения - повьш1ение быстродействия путем совмещения операций чтения и записи при трансляции информации.

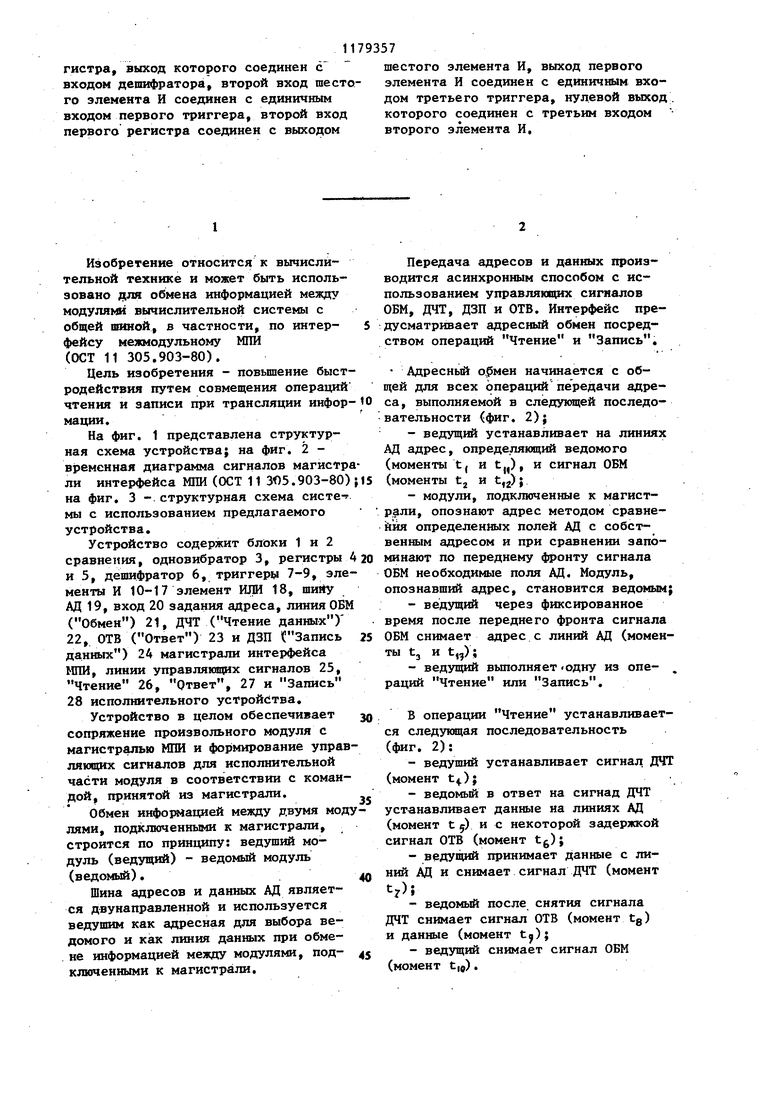

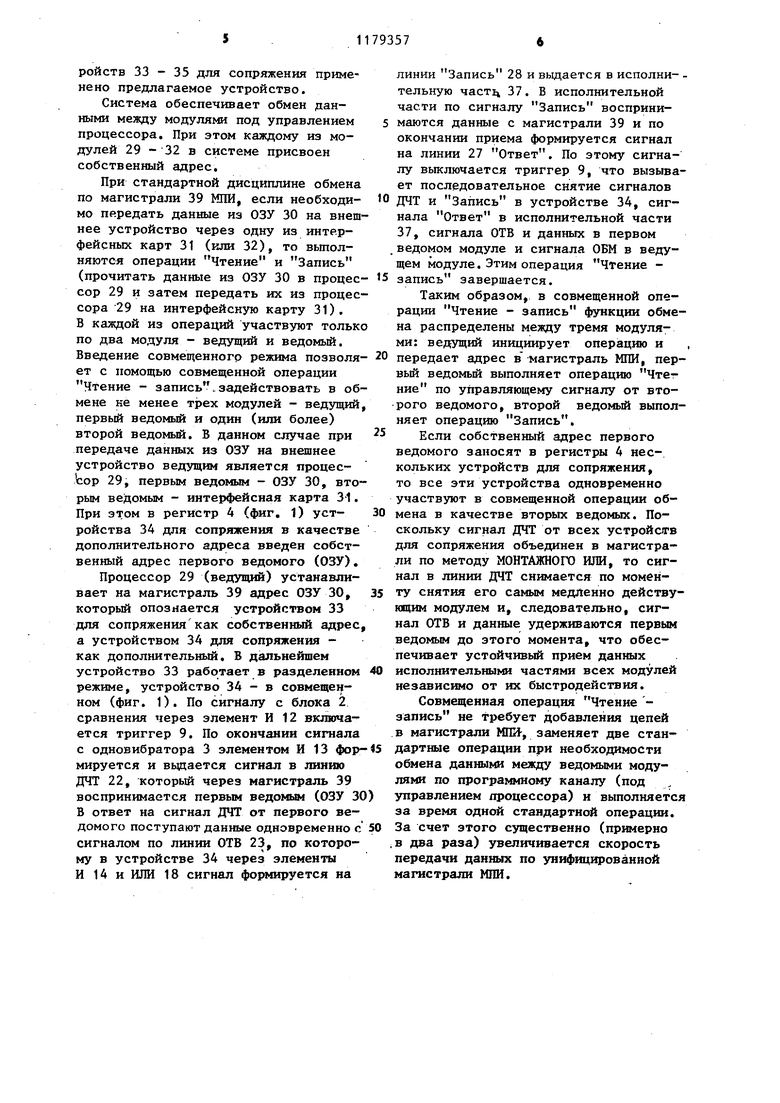

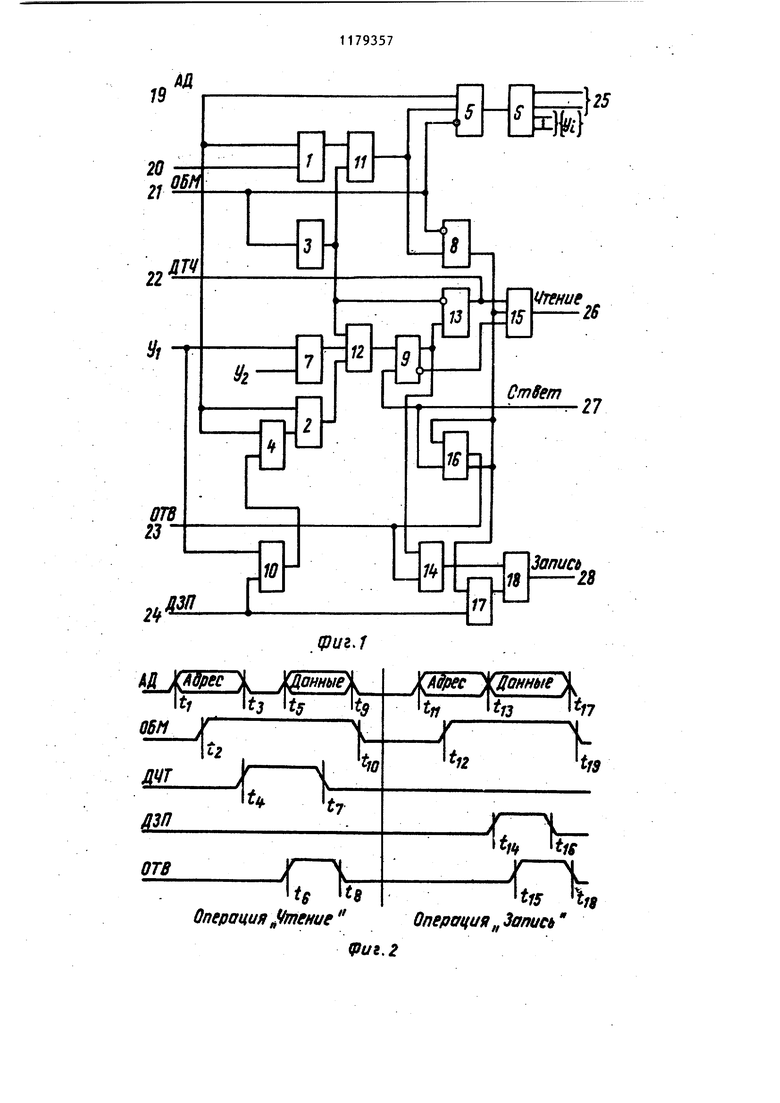

На фиг. 1 представлена структурная схема устройства; на фиг. 2 временная диаграмма сигналов магистрали интерфейса МПИ (ОСТ 11 305.903-80) на фиг. 3 -. структурная схема систе-г мы с использованием предлагаемого устройства.

Устройство содержит блики 1 и 2 сравнения, одновибратор 3, регистры 4 и 5, деншфратор 6, триггеру 7-9, элементы И 10-17 элемент ИЛИ 18, шийу АД 19, вход 20 задания адреса, линия ОБМ (Обмен) 21, ДЧТ (Чтение данных) 22, ОТВ (Ответ) 23 и ДЗП (Запись данных) 24 магистрали интерфейса МПИ, линии управляязщих сигналов 25, Чтение 26, Ответ, 27 и Запись 28 исполнительного устройства.

Устройство в целом обеспечивает сопряжение произвольного модуля с магистралью МПИ и формирование управляющих сигналов для исполнительной части модуля в соответствии с командой, принятой из магистрали.

Обмен инфо1 ацией между двумя модулями, подключенными к магистрали, строится по принципу: ведуший модуль (ведущий) ведомый модуль (ведомый),

Шина адресов и данных АД является двунаправленной и используется ведушим как адресная для выбора ведомого и как линия данных при обмене информацией между модулями, подключенными к магистрали.

Передача адресов и данных производится асинхронным способом с использованием управляющих сигналов ОБМ, ДЧТ, ДЗП и ОТВ. Интерфейс пре:дусматривает адресный обмен посредством операций Чтение и Запись,

Адресньй о,0мен начинается с общей для всех операцийпередачи адреса, выполняемой в следующей последовательности (фиг. 2);

-ведущий устанавливает на линиях АД адрес, определяющий ведомого (моменты t, и t,,), и сигнал ОБМ (моменты tj и tfg);

-модули, подключенные к магистрали, опознают адрес методом сравнейия определенных полей АД с собственш 1м адресом и при сравнении запоминают по переднему фронту сигнала ОБМ необходимые поля АД. Модуль, опознавший адрес, становится ведомым

-ведущий через фиксированное время после переднего фронта сигнала ОБМ снимает адрес с линий АД (моменты tj и t,,);

-ведущий выполняет-одну из операций Чтение или Запись.

В операции Чтение устанавливается следукицая последовательность (фиг. 2):

-ведуший устанавливает сигнал. ДЧ (момент t);

-ведомый в ответ на сигнад ДЧТ устанавливает данные на линиях АД (момент t ) и с некоторой задержкой сигнал ОТВ (момент tg);

-ведущий принимает данные с линий АД и снимает сигнал ДЧТ (момент

);

-ведомый после снятия сигнала ДЧТ снимает сигнал ОТВ (момент tg) и данные (момент ta);

-ведущий снимает сигнал ОБМ (момент t,j).

311

в операции Запись устанавливается следующая последовательность, (фиг. 2):

-ведущий устанавливает данные на линиях АД (момент tj) и сигнал ДЗП (момент Цд);

-ведомый принимает информацию с линий АД и устанавливает сигнал

ОТВ (момент tjy);

- ведущий снимает сигнал ДЗП

(момент t 1) и данные (момент tf) ;

-ведомый снимает- сигнал ОТВ (момент t|j);

-ведущий снимает сигнал ОБМ (моент t,p.

Устройство работает в двух режиах; разделенном и совмещенном,

В разделенном режиме в каждом икле обмена выполняется одна из операций Чтение или Запись, задаваемая ведущим. В совмещенном режие вьшолняется одна из операций разеленного режима (Чтение или Заись) или совмещенная операция Чтение - запись.

В разделенном режиме по шине Д 19 от ведущего модуля (процессора) передается адрес выбираемого модуля одновременно с сигналом по линии ОБМ 21. По переднему фронту сигнала ОБМ одновибратором 3 формируется одиночный импульс, длительность которого должна быть равной установленному дисциплиной обмена по магистрали МПИ времени передачи адреса. При сравнении адреса, нахо дящегося на щине АД 19, с собственным адресом, находящимся, на входе задания адреса 20 устройства, по сигналу с выхода блока 1 сравнения и сформированному одновибратором 3 одиночному импульсу через элемент И 11 устанавливается триггер 8, Сигнал с выхода этого триггера разрешает прохождение сигнала с линии ДЧТ 22 через элемент И 15 на линию 26 Чтение для исполнительного устройства в операции Чтение, сигнала с линии ДЗП 24 через И 17 и элемент ИЛИ 18 на линию 28,Запись в операции Запись и сигнала с линии 27 Ответ от исполнительного устройства через элемент И 16 на линию 23 ОТВ магистрали в обеих операциях. По переднему фронту сигнала ОБМ при сравнении адреса через элемент И 11 записываются с шины АД 19 в регистр необходимые поля, содержа574

щие информацию д.г1я управления, В соответствии с принятым содержимым регистра 5 дещифратор 6 формирует управляющие сигналы, часть из которых используется в устройстве, а часть выдается в исполнительное устройство по линиям 25,

По сигналу с первого выхода дешифратора 6 включается триггер 7, задающий совмещенный режим, через элемент И 10 разрешается ввод с шины АД 19 во время операции Запись дополните.пьного адреса в регистр 4, По сигналу с второго выхода триггер 7 выключается, запрещая совмещенный режим.

Таким образом,в разделенном режиме устройство участвует в обмене в качестве ведомого и только в цик-

лах, в которых опознается собственный адрес на шине АД магистрали МПИ, При этом транслируются управляющие сигналы ДЧТ, ДЗП и ОТВ междз магистралью и исполнительным устройством, принимается управ.г1яющая информация с шины АД, по которой фо1 мируется множество управляющих сигналов по линиям 7.5 для исполнительного устройства и задается режим работы (разделенный шш совмещенный) для следующих циклов обмена информгцией.

В совмещенном режиме (включен триггер 7) при опознании блок-ом 1

сравнения собственного адреса на шине АД устройство выполняет операцию разделенного режима (как описано вьш1е), а при опознании блоком 2 сравнения дополнительного адреса вьтолняет совмещенную операцию,

Вьтолнение совмещенной операции представлено на фиг. 3.

Система содержит модули процессора 29, оперативного запоминающего

устройства 30 (ОЗУ) и интерфейсных карт 31 и 32. Модули 30-32 состоят из устройств 33 - 35 для сопряжения, накопителей 36 и исполнительных частей 37 и 38, Все модули объединены

единой магистралью 39 МПИ, а исполнительные части содержат линии 40 и 41 внешних интерфейсов.

Процессор обрабатьшает данные и управляет обменом, ОЗУ служит для

хранения данных и команд, интерфейсные карты используются для преобразова {ия интерфейса МПИ в интерфейсы внешних устройств. В качестве устройств 33 - 35 для сопряжения применено предлагаемое устройство.

Система обеспечивает обмен данными между модулями под управлением процессора. При этом каждому из модулей 29 - 32 в системе присвоен собственный адрес.

При стандартной дисциплине обмена по магистрали 39 МПИ, если необходиМО передать данные из ОЗУ 30 на внешнее устройство через одну из интерфейсных карт 31 (или 32), то вьтолняются операции Чтение и Запись (прочитать данньш из ОЗУ 30 в процессор 29 и затем передать их из процессора 29 на интерфейсную карту 31). В каждой из операций участвуют только по два модуля - ведущий и ведомый. Введение совмещенного режима позволяет с помощью совмещенной операции Чтение - запись.задействовать в обмене не менее трех модулей - ведзга(ий, первый ведомый и один (или более) второй ведомый. В данном случае при передаче данных из ОЗУ на внешнее устройство ведущим является процесtop 29, первым ведомым - ОЗУ 30, вторым ведомым - интерфейсная карта 3-1. При этом в регистр 4 (фиг. 1) устройства 34 для сопряжения в качестве дополнительного адреса введен собственный адрес первого ведомого (ОЗУ).

Процессор 29 (ведущий) устанавливает на магистраль 39 адрес ОЗУ 30, который опознается устройством 33 для сопряжения как собственный адрес, а устройством 34 для сопряжения - как дополнительный. В дальнейшем устройство 33 работает в разделенном режиме, устройство 34 - в совмещенном (фиг. 1). По сигналу с блока 2 сравнения через элемент И 12 включается триггер 9. По окончании сигнала с одновибратора 3 элементом И 13 фор мируется и вьщается сигнал в линию ДЧТ 22, который через магистраль 39 воспринимается первым ведомым (ОЗУ 30 В ответ на сигнал ДЧТ от первого ведомого поступают данные одновременно с сигналом по линии ОТВ 23, по которому в устройстве 34 через элементы И 14 и ИЛИ 18 сигнал формируется на

линии Запись 28 и вьщается в исполнительную частц 37. В исполнительной части по сигналу Запись воспринимаются данные с магистрали 39 и по окончании приема формируется сигнал на линии 27 Ответ. По этому сигналу выключается триггер 9, что вызьшает последовательное снятие сигналов ДЧТ и Запись в устройстве 34, сигнала Ответ в исполнительной части 37, сигнала ОТВ и данных в первом ведомом модуле и сигнала ОБМ в ведущем модуле. Этим операция Чтение запись завершается.

Таким образом, в совмещенной операции Чтение - запись функции обмена распределены между тремя модулями: ведущий инициирует операцию и передает адрес в магистраль МПИ, первый ведомый выполняет операцию Чтение по управляющему сигналу от второго ведомого, второй ведомый выполняет операцию Запись.

Если собственный адрес первого ведомого заносят в регистры 4 нескольких устройств для сопряжения, то все эти устройства одновременно участвуют в совмещенной операции обмена в качестве вторых ведомых. Поскольку сигнал ДЧТ от всех устройств для сопряжения объединен в магистрали по методу МОНТАЖНОГО ИЛИ, то сигнал в линии ДЧТ снимается по моменту снятия его самым медленно действующим модулем и, следовательно, сигнал ОТВ и данные удерживаются первым ведомым до этого момента, что обеспечивает устойчивый прием данных исполнительными частями всех модулей независимо от их быстродействия.

Совмещенная операция Чтение запись не требует добавления цепей в магистрали МПИ-, заменяет две стандартные операции при необходимости обмена данными между ведомыми модулями по программному каналу (под управлением процессора) и выполняетс за время одной стандартной операции. За счет этого существенно (примерно .в два раза) увеличивается скорость передачи данных по унифицированной магистрали МШ.

Операция J/mewe Операция,, Запись

иг.2

зг г

Г

33

9

зе

L..

J

ГТ. I

J7

iL

/7

Ф

(риг.З

| Способ автоматического управления процессом получения сосисочной оболочки | 1980 |

|

SU941963A2 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Интерфейсный блок для управляющей системы | 1981 |

|

SU1001075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-03-30—Подача