Изобретение относится к области пычислительной техники и может быть использовано в специализированных вычислительных машинах, 6 навигационных информационно-вычислительных и упр авляющих си с т емах.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности вычисления функций у arcsinx, у arctgx.

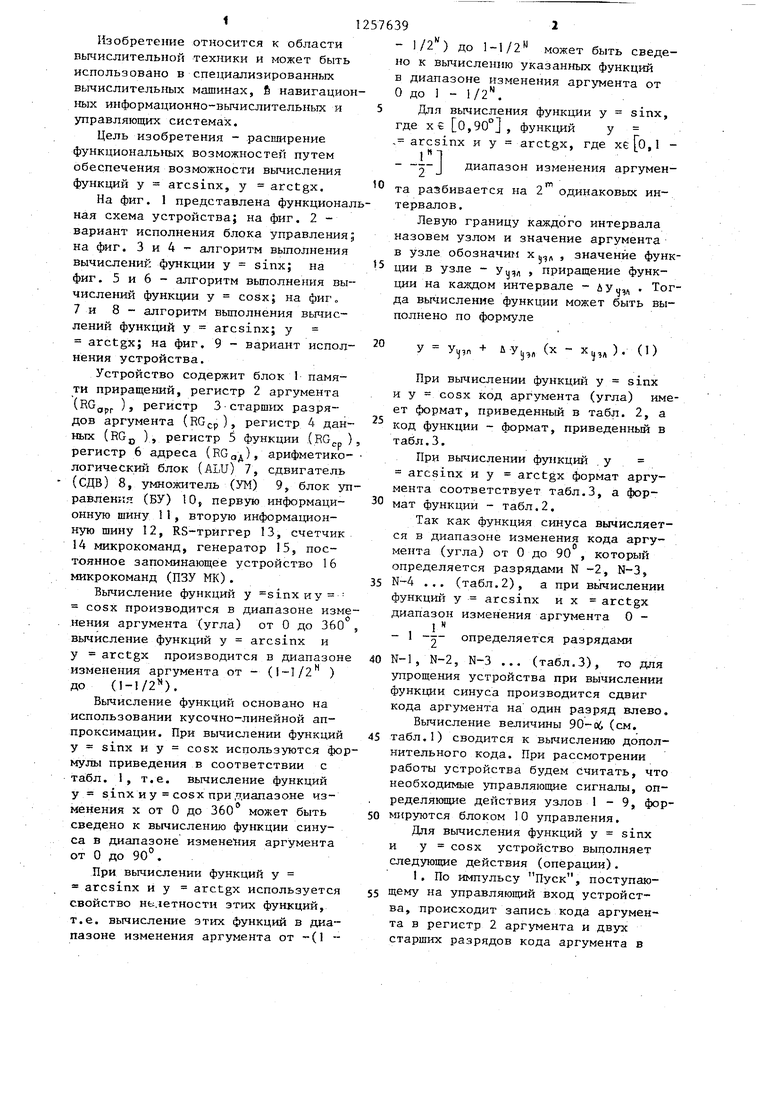

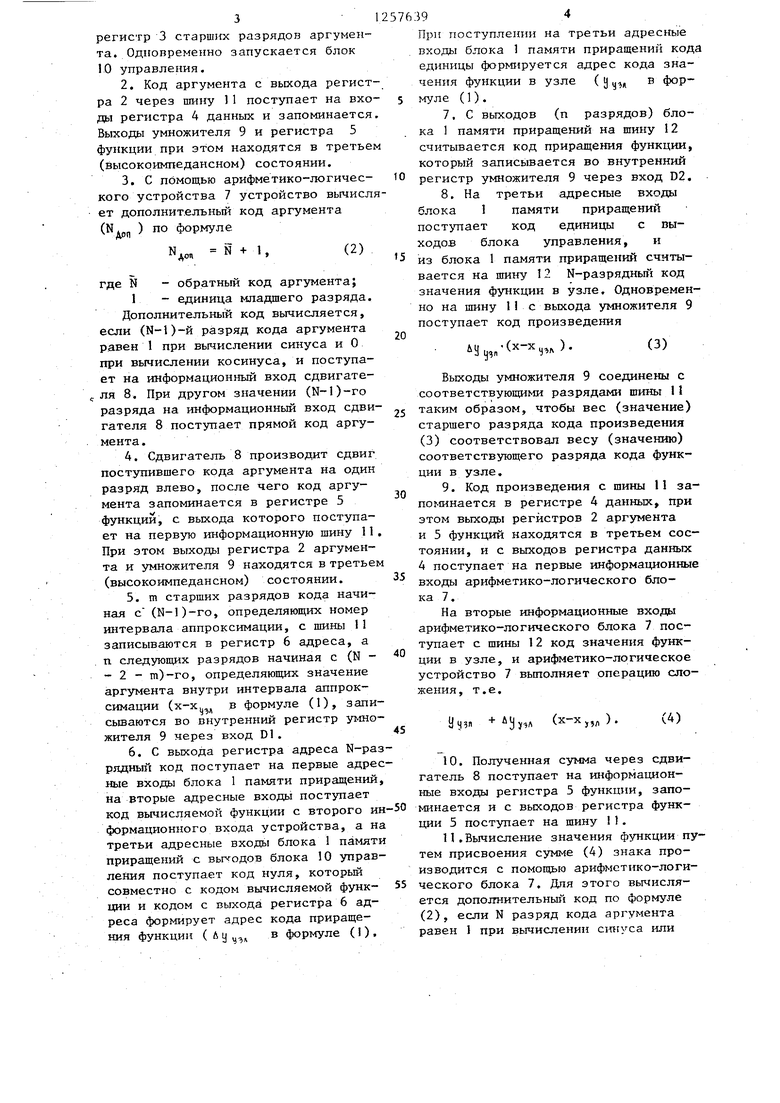

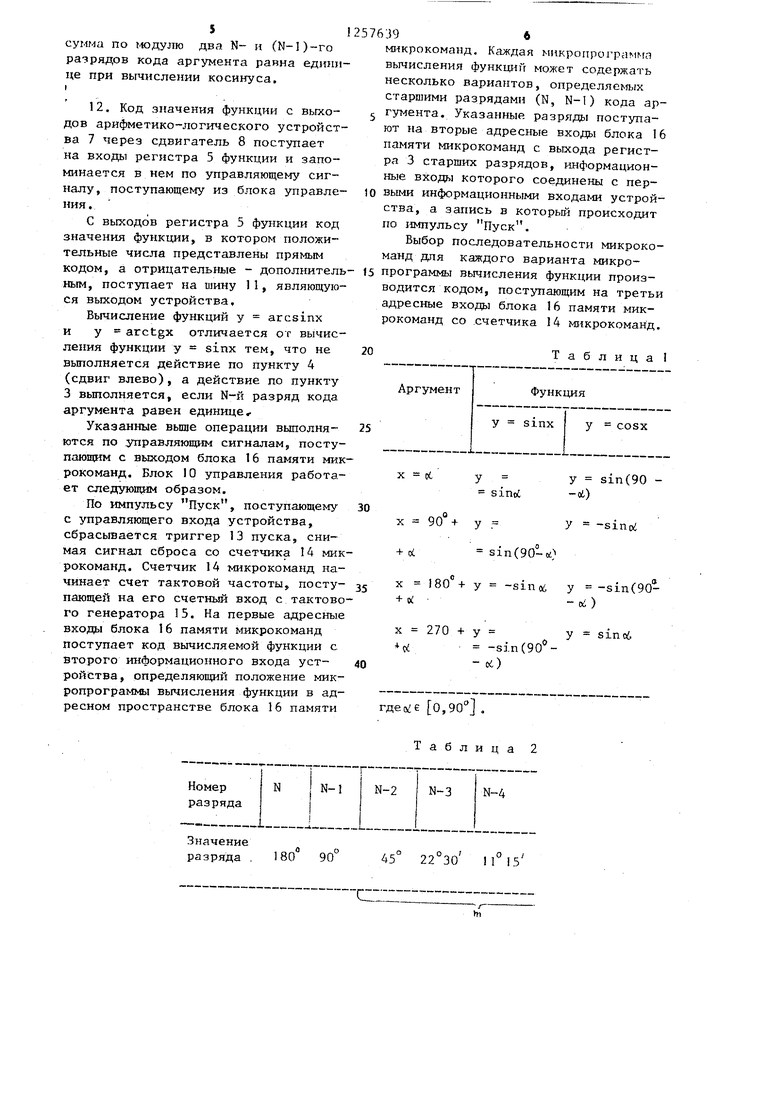

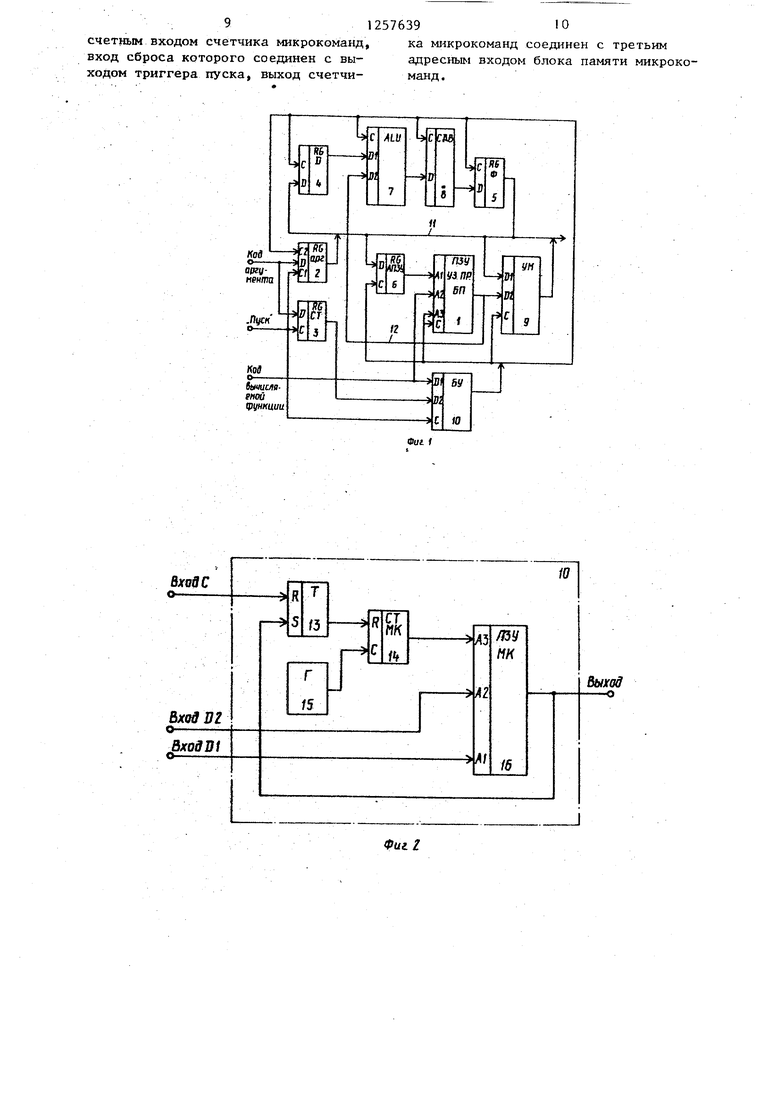

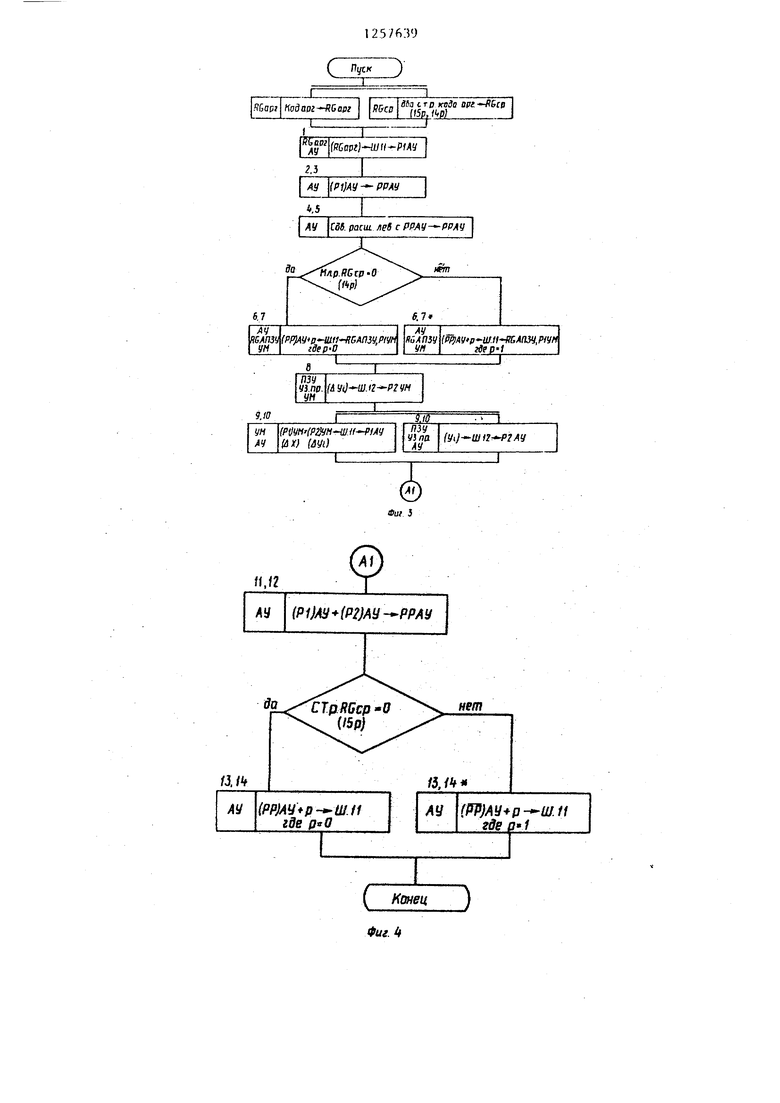

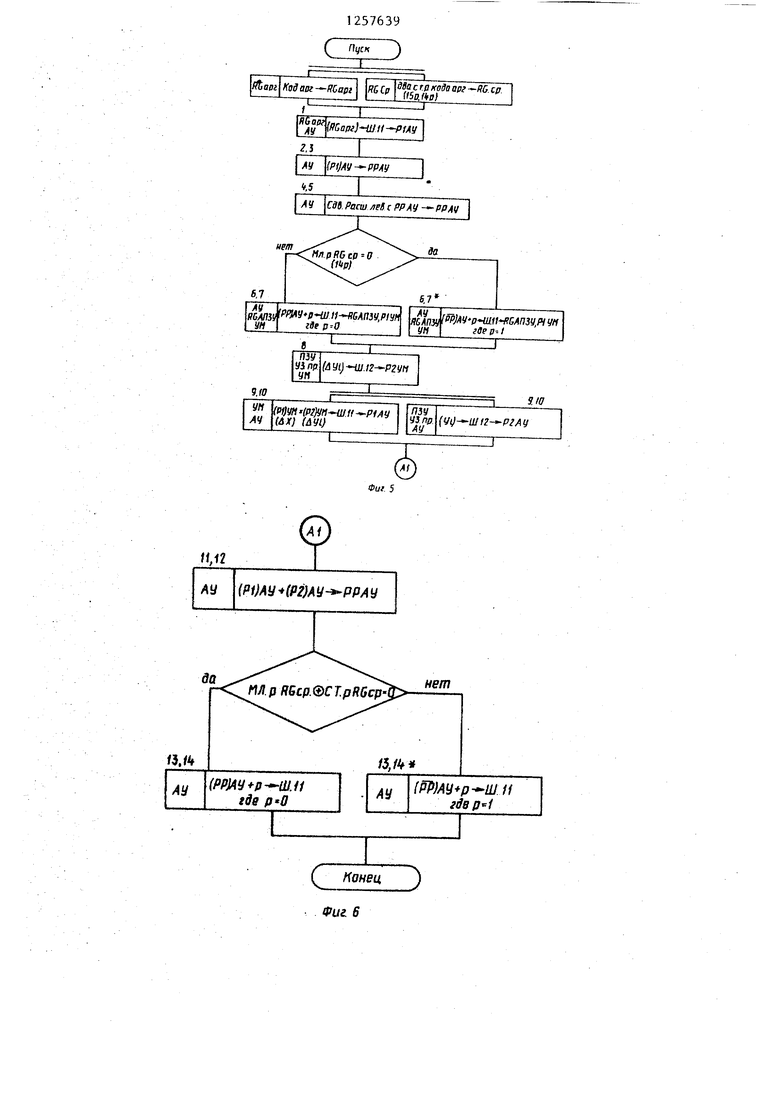

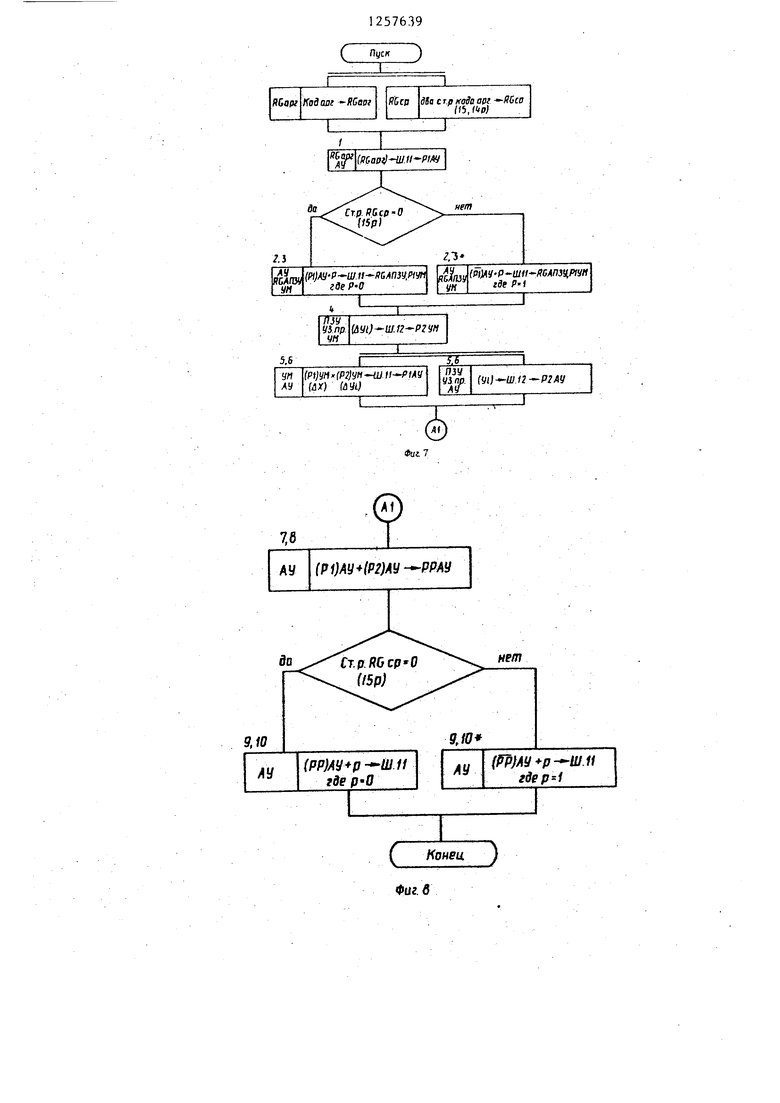

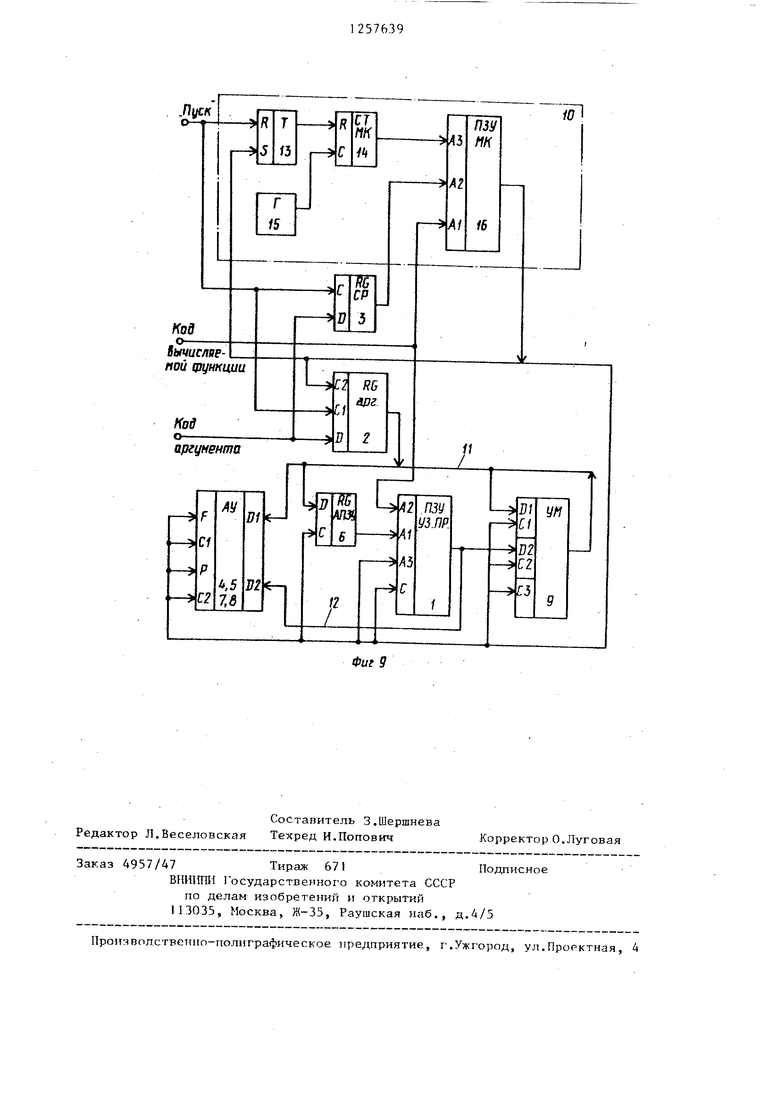

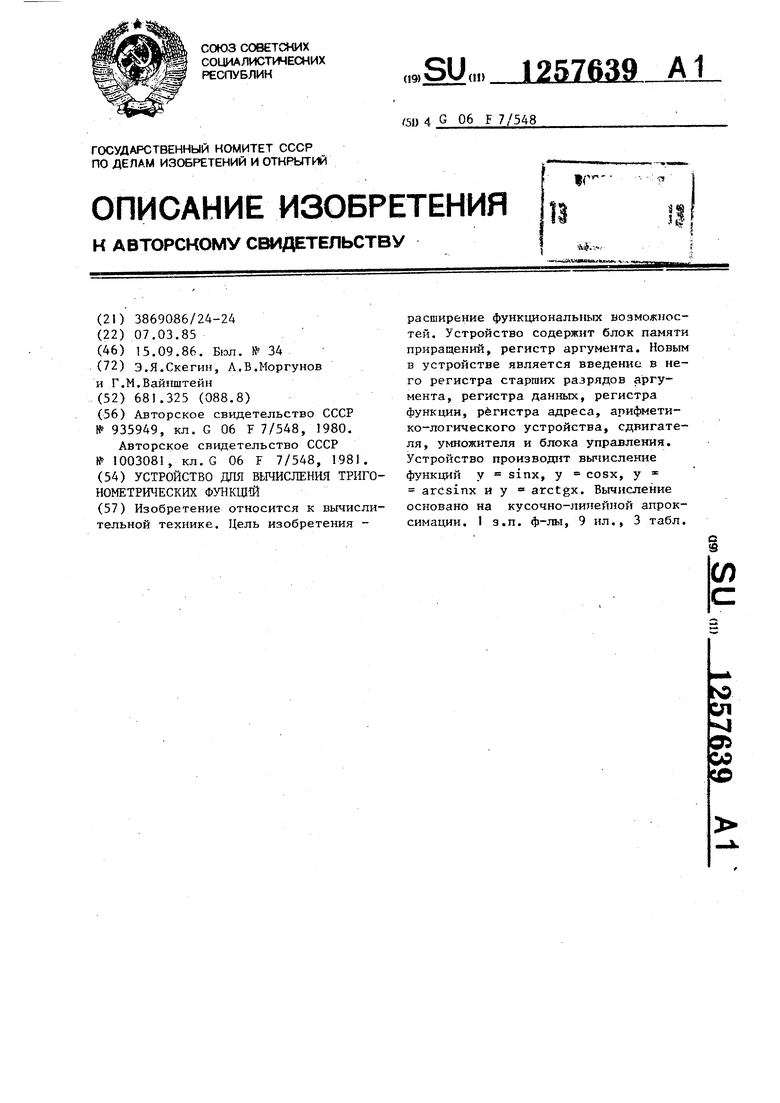

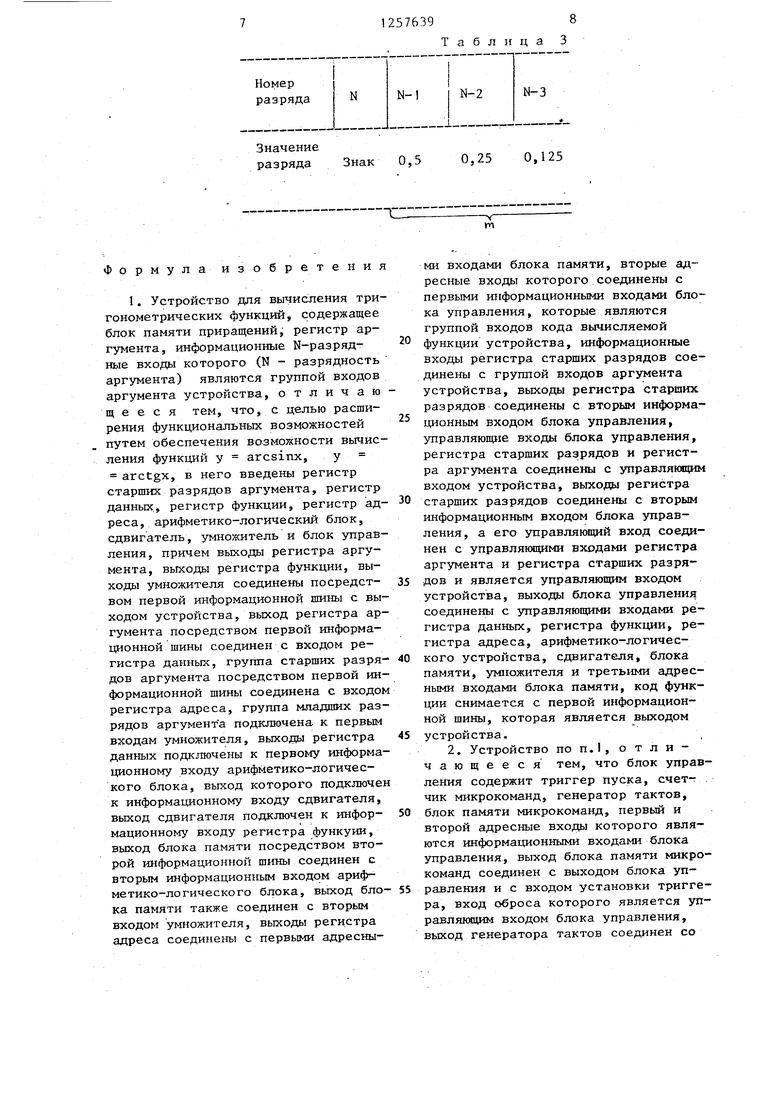

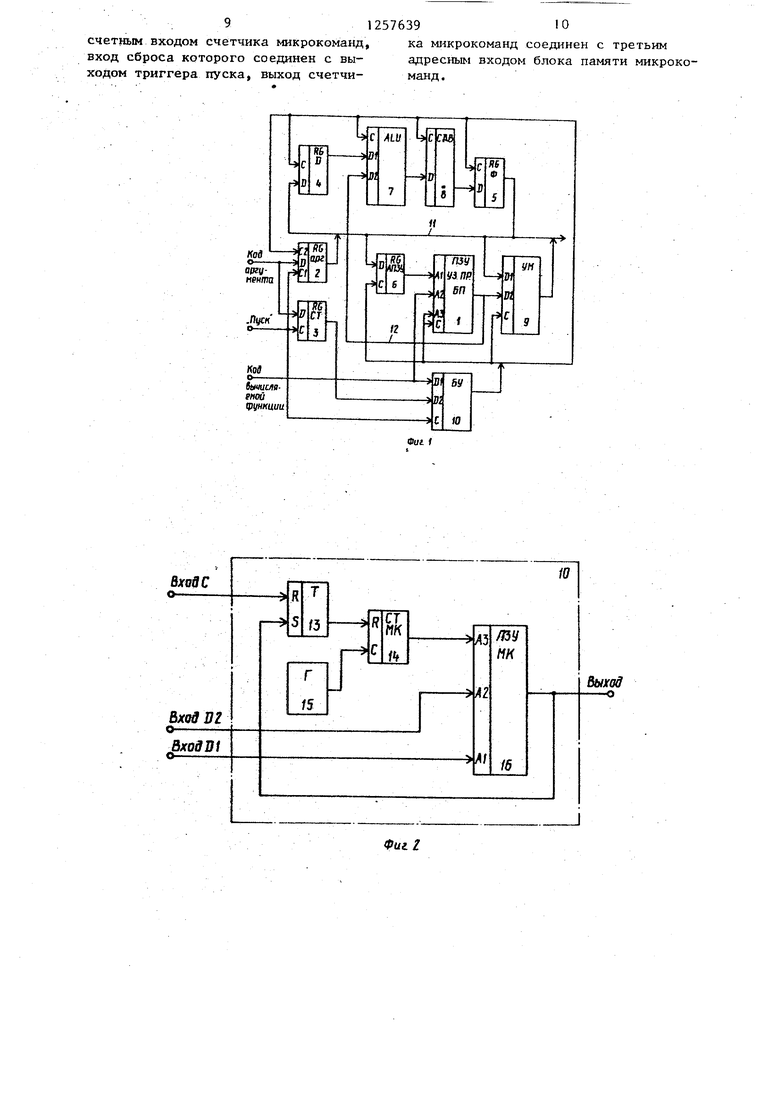

На фиг. 1 представлена функционалная схема устройства; на фиг. 2 - вариант исполнения блока управления 5 на фиг. 3 и 4 - алгоритм выполнения вычислений функции у sinx; на фиг. 5 и 6 - алгоритм выполнения вычислений функции у cosx; на фиг„ 7 и 8 - алгоритм вьшолнения вычислений функций у arcsinx; у arctgx; на фиг. 9 - вариант исполнения устройства.

Устройство содержит блок 1 памяти приращений, регистр 2 аргумента (RGg ), регистр 3-старших разрядов аргумента (RGj-p), регистр 4 данных (RGjj ),, регистр 5 функции .(RG ) регистр 6 адреса (RGa), арифметико- логический блок (ALU) 7, сдвигатель (СДВ) 8, умножитель (УМ) 9, блок управления (БУ) 10, первую информационную шину 1I, вторую информационную шину 12, RS-трИггер 13, счетчик 14 микрокоманд, генератор 15, постоянное запоминающее устройство 16 микрокоманд (ПЗУ МК).

Вычисление функций у з1пхиу - COSX производится в диапазоне нения аргумента (угла) от О до вычисление функций у arcsinx и у arctgx производится в диапазоне изменения аргумента от - (1-1/2 ) до (-1/2«).

Вычисление функций основано на использовании кусочно-линейной аппроксимации. При вычислении функций у sinx и у cosx используются формулы приведения в соответствии с

изме 360

табл. У

1, т.е. вычисление функций

sinx иу COSX при диапазоне изменения X от О до 360 может быть сведено к вычислению функции синуса в диапазоне изменения аргумента от О до 90.

При вычислении функций у arcsinx и у arctgx используется свойство Hfci.ieTHocTH этих функций, т.е. вычисление этих функций в диапазоне изменения аргумента от (1

5

1/2 ) до 1-1/2 может быть сведено к вычислению указанных функций в диапазоне изменения от О до 1 - 1/2

Для вычисления функции у sinx, где х€ о,90°, функций У

, arcsinx и у arctgx, где ,1 - ,«-

- -J диапазон изменения аргумента разбивается на 2 одинаковых интервалов.

Левую границу каждого интервала назовем узлом и значение аргумента в узле обозначим х , значение функции в узле - , приращение функции на каждом интервале - i у

УЭЛ

Тогда вычисление функции может быть выполнено по формуле

у у.

ду

|)ЭЛ

(х )ЭЛ )

(1)

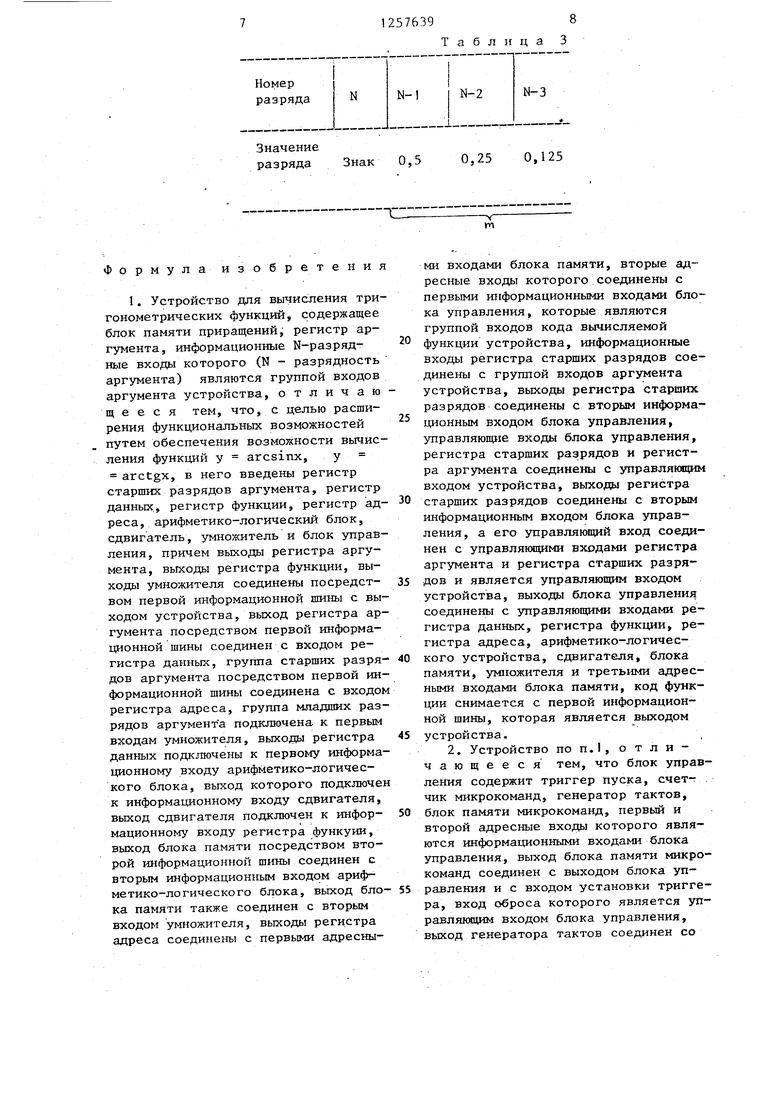

При вычислении функций у sinx и у COSX код аргумента (угла) имеет формат, приведенный в табл. 2, а код функции - формат, приведенный в табл.3.

При вычислении функций .у arcsinx и у arctgx формат аргумента соответствует табл.3, а формат функции - табл.2.

Так как функция синуса вычисляется в диапазоне изменения кода аргумента (угла) от О до 90 , который определяется разрядами N -2, N-3, N-4 ... (табл.2), а при вычислении функций у arcsinx и х arctgx диапазон изменения аргумента О .

определяется разрядами

N-1, N-2, N-3 ... (табл.3), то для упрощения устройства при вычислении функции синуса производится сдвиг кода аргумента на один разряд влево, Вычисление величины 90-oi (см,

табл.1) сводится к вычислению дополнительного кода. При рассмотрении работы устройства будем считать, что необходимые управляющие сигналы, определяющие действия узлов 1 - 9, формируются блоком 10 управления.

Для вычисления функций у sinx и У - COSX устройство выполняет следующие действия (операции).

I, По импульсу Пуск, поступающему на управляющий вход устройства, происходит запись кода аргумента в регистр 2 аргумента и двух старших разрядов кода аргумента в

регистр 3 старших разрядов аргумента. Одновременно запускается блок 10 управления.

2.Код аргумента с выхода регистра 2 через шину 11 поступает на входы регистра 4 данных и запоминается. Выходы умножителя 9 и регистра 5 функции при этом находятся в третьем (высокоимпедансном) состоянии.

3,С помощью арифметико-логического устройства 7 устройство вычисля ет дополнительный код аргумента (Ыдд ) по формуле

N

ДСП

N + 1,

где N - обратный код аргумента;

1 - единица мпадшего разряда. Дополнительный код вычисляется, если (Ы-1)-й разряд кода аргумента равен 1 при вычислении синуса и О при вычислении косинуса, и поступает на информационный вход сдвигате- ля 8. При другом значении (N-l)-ro разряда на информационный вход сдви- гателя 8 поступает прямой код аргумента.

4.Сдвигатель 8 производит сдвиг поступившего кода аргумента на один разряд влево, после чего код аргумента запоминается в регистре 5 функций, с выхода которого поступает на первую информационную шину 11, При этом выходы регистра 2 аргумента и умножителя 9 находятся в третьем (высокоимпедансном) состоянии.

5.m старших разрядов кода начиная с (N-l)-ro, определяющих номер интервала аппроксимации, с шины 11 записываются в регистр 6 адреса, а п следующих разрядов начиная с (N - - 2 - т)-го, определяющих значение аргумента внутри интервала аппроксимации (х-Хц, в формуле (1), записываются во внутренний регистр умножителя 9 через вход D1.

6.С выхода регистра адреса N-pas рядный код поступает на первые адресные входы блока 1 памяти приращений, на вторые адресные входы поступает код вычисляемой функции с второго информационного входа устройства, а на третьи адресные входы блока 1 памяти приращений с выводов блока 10 управления поступает код нуля, который совместно с кодом вычисляемой функции и кодом с выхода регистра 6 адреса формирует адрес кода приращения функции ( л у

ч

в формуле ().

576394

При поступлении на третьи адресные входы блока 1 памяти приращений кода единицы формируется адрес кода значения функции в узле ( ) у-), в фор- 5 муле (1).

7,С выходов (п разрядов) бло- . ка 1 памяти приращений на шину 12

считывается код приращения функции, который записывается во внутренний О регистр умножителя 9 через вход D2,

8.На третьи адрес1ше входы блока 1 памяти приращений поступает код единицы с вы

ходов блока управления,

и

из блока 1 памяти приращений считывается на шину 12 Ы-разрядньп1 код значения функции в узле. Одновременно на шину П с выхода умножителя 9 поступает код произведения

20

Ну,л )

(3)

Выходы умножителя 9 соединены с соответствующими разрядами шины I1

таким образом, чтобы вес (значение) старшего разряда кода произведения (3) соответствовал весу (значению) соответствующего разряда кода функции в узле.

9. Код произведения с шины 11 запоминается в регистре 4 данных, при этом выходы регистров 2 аргумента и 5 функций находятся в третьем состоянии, и с выходов регистра данных 4 поступает на первые информационные входы арифметико-логического блока 7.

На вторые информационные входы арифметико-логического блока 7 поступает с шины 12 код значения функции в узле, и арифметико-логическое устройство 7 выполняет операцию сложения, т.е.

Учзл

+ ijj

5Л

(х-х... ).

)л

(4)

10. Полученная сумма через сдви- гатель 8 поступает на информационные входы регистра 5 функции, запо- минается и с выходов регистра функции 5 поступает на шину 11.

П.Вычисление значения функции путем присвоения сумме (4) знака производится с помощью арифмстико-логи- ческого блока 7. Дня этого вычисляется допохгнительный код по формуле (2), если N разряд кода аргумента равен 1 при вычислении cmiyca или

разрядов кода аргумента равна единице при вычислении косинуса. I

12. Код значения функции с выходов арифметико-логического устройства 7 через сдвигатель 8 поступает на входы регистра 5 функции и запо- ьшнается в нем по управляющему сиг-налу, поступающему из блока управления ,

С выходов регистра 5 функции код значения функции, в котором положительные числа представлены прямым

кодом, а отрицательные - дополнитель- fs программы вычисления функции произным, поступает на шину 11, являющуюся выходом устройства.

Вычисление функций у arcsinx и У arctgx отличается от вычисления функции у sinx тем, что не 20 выполняется действие по пункту 4 (сдвиг влево), а действие по пункту 3 выполняется, если N-й разряд кода аргумента равен единице.

Указанные выше операции выполня- 25 ются по .управляю1191М сигналам, поступающим с выходом блока 16 памяти микрокоманд. Блок 10 управления работает следующим образом.

По импульсу Пуск, поступающему 30 с управляющего входа устройства, сбрасьгоается триггер 13 пуска, снимая сигнал сброса со счетчика 14 микрокоманд. Счетчик 14 микрокоманд начинает счет тактовой частоты, посту- 35 пающей на его счетный вход с тактового генератора 15. На первые адресные входы блока 16 памяти микрокоманд поступает код вычисляемой функции с второго информационного входа уст- 40 ройства, определяющий положение микропрограммы вычисления функции в адресном пространстве блока 16 памяти

водится кодом, поступающим на третьи адресные входы блока 16 памяти микрокоманд со счетчика 14 микрокоманд.

Таблица

X

+ оС

90 +

У .

У -sinoi

sin(90-oi}

X 180 + у -sinc ; + «:

X 270 + у :i

у -sin(90-ос;)

у sinai

-sin ( -ci)

0,90.

Значение

разряда . 180° 90°

вычисления функций может содержать несколько вариантов, определяемых старшими разрядами (N, N-I) кода ар5 гумента. Указанные разряды поступают на вторые адресные входы блока 16 памяти микрокоманд с выхода регистра 3 старших разрядов, информационные входы которого соединены с пер10 выми информационными входами устройства, а запись в который происходит по 11млульсу Пуск.

Выбор последовательности микрокоманд для каждого варианта микроводится кодом, поступающим на третьи адресные входы блока 16 памяти микрокоманд со счетчика 14 микрокоманд.

Таблица I

X

90 +

У .

У -sinoi

+ оС

sin(90-oi}

180 + у -sinc ;

270 + у

у -sin(90-ос;)

у sinai

-sin ( -ci)

0,90.

Таблица 2

45° 22°30 и 15

Формула изобретения

1. Устройство для вычисления тригонометрических функций, содержащее блок памяти приращений, регистр аргумента, информационные N-разряд- ные входы которого (N - разрядность аргумента) являются группой входов аргумента устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения возмо7лности вычисления функций у arcsinx.

У

arctgx, в него введены регистр старших разрядов аргумента, регистр данных, регистр функции, регистр адреса, арифметико-логический блок, сдвигателъ, умножитель и блок управления, причем выходы регистра аргумента, выходы регистра функции, выходы умножителя соединены посредством первой информационной шины с выходом устройства, выход регистра аргумента посредством первой информационной шины соединен с входом регистра данных, группа старших разрядов аргумента посредством первой информационной шины соединена с входом регистра адреса, группа младших разрядов аргумент а подключена к первым входам умножителя, выходы регистра данных подключены к первому информационному входу арифметико-логического блока, выход которого подключен к информационному входу сдвигателя, выход сдвигателя подключен к информационному входу регистра функуии, выход блока памяти посредством второй информационной шины соединен с вторым информационным входам арифметико-логического блока, выход бло- ка памяти также соединен с вторым входом умножителя, выходы регистра адреса соединены с первыми адресны

20

5

0

5

0

5

5

0

ми входами блока памяти, вторые адресные входы которого соединены с первыми информационными входами блока управления, которые являются группой входов кода вычисляемой функции устройства, информационные входы регистра старших разрядов соединены с группой входов аргумента устройства, выхода регистра старших разрядов соединены с вторым информационным входом блока управления, управляющие входы блока управления, регистра старших разрядов и регистра аргумента соединены с управляющим входом устройства, выходы регистра старших разрядов соединены с вторым информационным входом блока управления, а его управляющий вход соединен с управляющими входами регистра аргумента и регистра старших разрядов и является управляющим входом устройства, выходы блока управления соединены с управляюпщми входами регистра данных, регистра функхщи, регистра адреса, арифметико-логического устройства, сдвигателя, блока памяти, умножителя и третьими адресными входами блока памяти, код функции снимается с первой информационной шины, которая является выходом устройства.

2, Устройство по п.1, отличающееся тем, что блок управления содержит триггер пуска, счетчик микрокоманд, генератор тактов, блок памяти микрокоманд, первый и второй адресные входы которого являются информационными входами блока управления, выход блока памяти микрокоманд соединен с выходом блока управления и с входом установки триггера, вход оброса которого является управляющим входом блока управления, выход генератора тактов соединен со

91257639 О

счетным входом счетчика микрокоманд, ка микрокоманд соединен с третьим вход сброса которого соединен с вы- адресным входом блока памяти микроко- хоДом триггера пуска, выход счетчи- манд.

tawuieгтш

функции

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298740A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1322272A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

Изобретение относится к вычислительной технике. Цель изобретения расширение функциональных возможностей. Устройство содержит блок памяти приращений, регистр аргумента. Новым в устройстве является введение в него регистра старших разрядов аргумента, регистра данных, регистра функции, регистра адреса, арифметико-логического устройства, сдвигате- ля, умножителя и блока управления. Устройство производит вы шсление функций у sinx, у COSX, у arcsinx и у arctgx. Вычисление основано на кусочно-линейной апрок- симации. 1 з.п. ф-лы, 9 ил., 3 табл.

( %« )

АУ {Р1)

сев. (мгшлей с РРАд- РРАУ

.RGtp-О

(АС

Лаг S

п,п

АУ

(РР}АУ р- Ш.11 где р«0

АУ

fffP}AУ p- Ш.t1 где

f

( Ктец Фиг. it

1257639

ffiaoi

KaSast- RCapi

I

|/7ьод

X

)Ш11-Ч 1АУ

AV

(PtjAV- PPAy

ffc cpra w

нет

V J-fl/ 1)-Ч 6АПЗУ,Р1УН гйе p-0

КАПЗ УН

ly p- II GAnStJ.n т гве p-1

n,l2

° ПЯрМср.ФСТ.рКбср-

1Я6арг -Ш.

()

7,3

ffCA/I fWj/W P-U/.(,Pf«H

tf«

гве P O

ТГЗУ

Wnp

УЯ

w

M

(PtjyH (Р2)УН-HI/

Mr)

RCtoi/ iW

(Р)АУ Р Ш11 / ОАПЩР1УН где P i

L

т

{&Ш)Ш.

X

DL

IT

1

ШУ

«та

(Г

(.

Т

«в/п

Составитель З.Шершнева Редактор Л.Веселовская Техред И,Попович

Заказ 4957/47Тираж 671Подписное

ВРШНГИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Проияволстветпю-полиграфическое предприятие, г.Ужгород, ул.ПроРктная, А

Корректор О.Луговая

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003081A1 |

Авторы

Даты

1986-09-15—Публикация

1985-03-07—Подача