(54) ТРИГГЕР НА ВЗАИМОДОПОЛНЯЮЩИХ МДП-ТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220123A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Аналоговый ключ | 1980 |

|

SU928645A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| Триггер на МДП-транзисторах | 1985 |

|

SU1330655A1 |

| Логический элемент | 1984 |

|

SU1228261A1 |

Изобретение относится к автоматике и вычислительной технике и пред.назначено для построения многовходовых тактируемых RC-триггеров, D-триг геров и параллельных регистров, обес печивающих при входных однополярных управляющих сигналах формирование двухполярных выходных напряжений. Известны триггеры на взаимодопёлняюших МДП-транзисторах, имекмцие два противофазных выхода, которые управляются одним -или двумя противофазным управляющими тактовьили cигнaJIaми Ш Недостаток этих устройств заключается в том, что на их выходах не.возможно получить двуполярных напря жений . Известен также триггер на взаимодополняющих МДП-транзисторах, сод жащий первый и второй двухвходовые логические элементы И-НЕ, каждый из которых состоит из двух пар транзисторов Противоположного типапроводимости, затворы которых образуют соответственно, первый и второй вхо ды логических элементов И-НЕ,первый вход первого логического элемента И-НЕ подключен к выходу второго логического элемейта И-НЕ, а первый вход второго логического элемента И-НЕ К ВЫХОДУ первого логического элемента И-НЕ f2 . Недостаток известного триггера заключается в том, что он также не обеспечивает формирования на противофазных выходах, двуполярных выходных напряжений при однополярных входных информационных сигналах. Цель изобретения - расширение функциональных возможностей, заключающихся в обеспечении формирования двуполярных выходных напряжений, при однополярных входных инфОЕЯлационных сигналах. Поставленная цель достигается тем, что в триггере на взаимодополняющих МДП-транзисторах, содержащем два двухвходовых логических элемента И-НЕ с перекрестными связями между выходами и первьийи входами и шины прямого и инверсного тактовых сигнешов в каждый логический элемент И-НЕ введены четыре дополнительных р-канальных транзистора, причем первый и второй дополнительные р-канальные транзисгторы включены между плюсовой шиной питания и, соответственно, вторым входом и истоком р-канального транзистора элемента И-НЕ, затвор которого подключен к первому вхолу элемента,

затворы первого и второго дополнительных р-канальных транзисторов подключен к шине инверсных тактовых сигналов,третий дополнительныйР-канальный тран истор включен между вторым входом элемента И-НЕ и соответствующей входной шиной триггера, а его затвор подключен к шине прямых тактовых сигналов четвертый дополнительный р-канальный транзистор включен между минусовой шиной питания и первым входом элемента И-НЕ, а его затвор подключен ко второму входу элемента И-НЕ

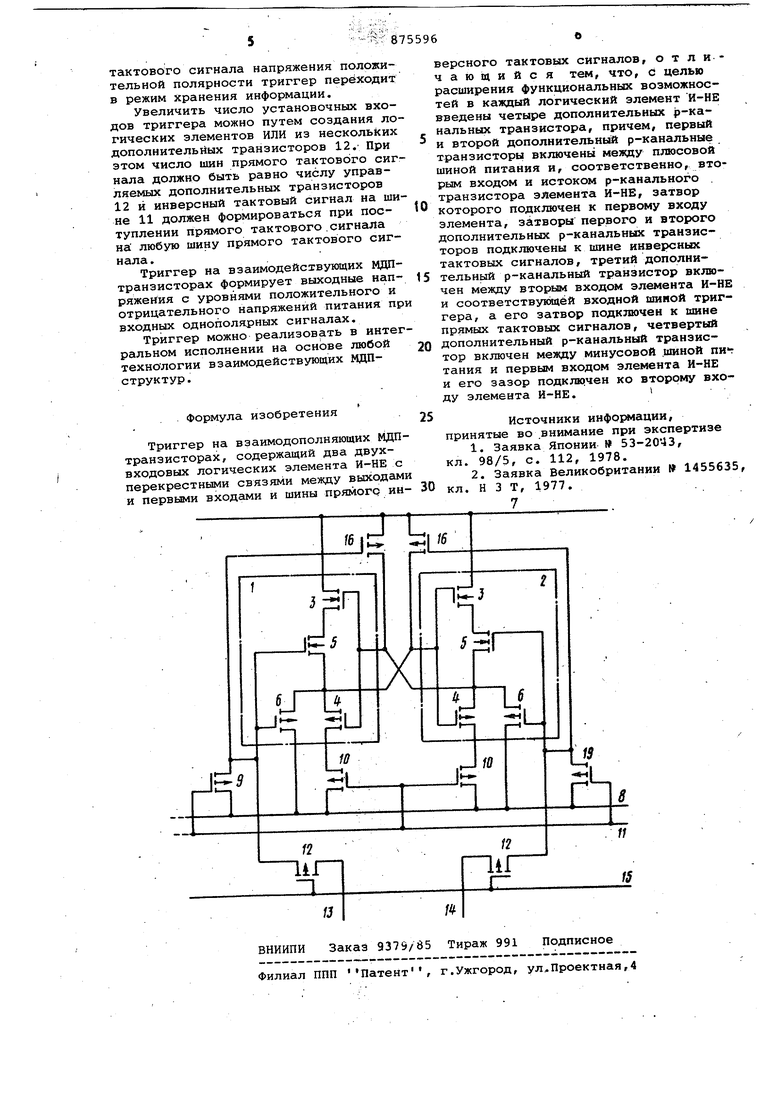

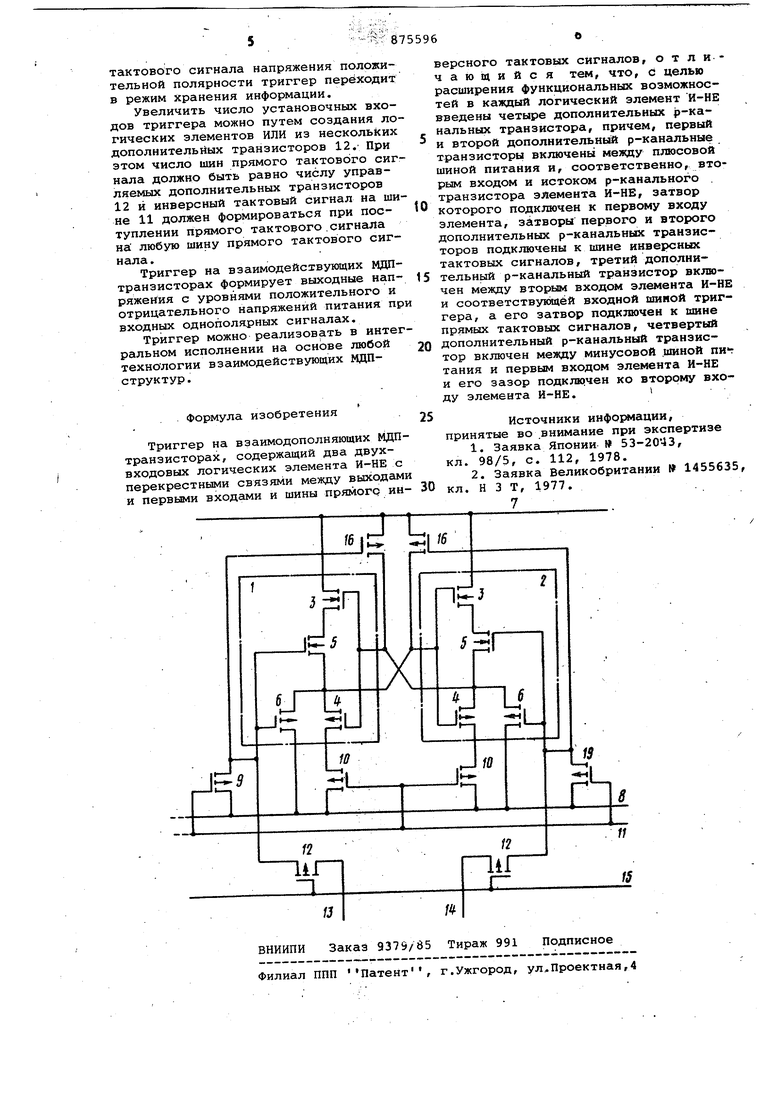

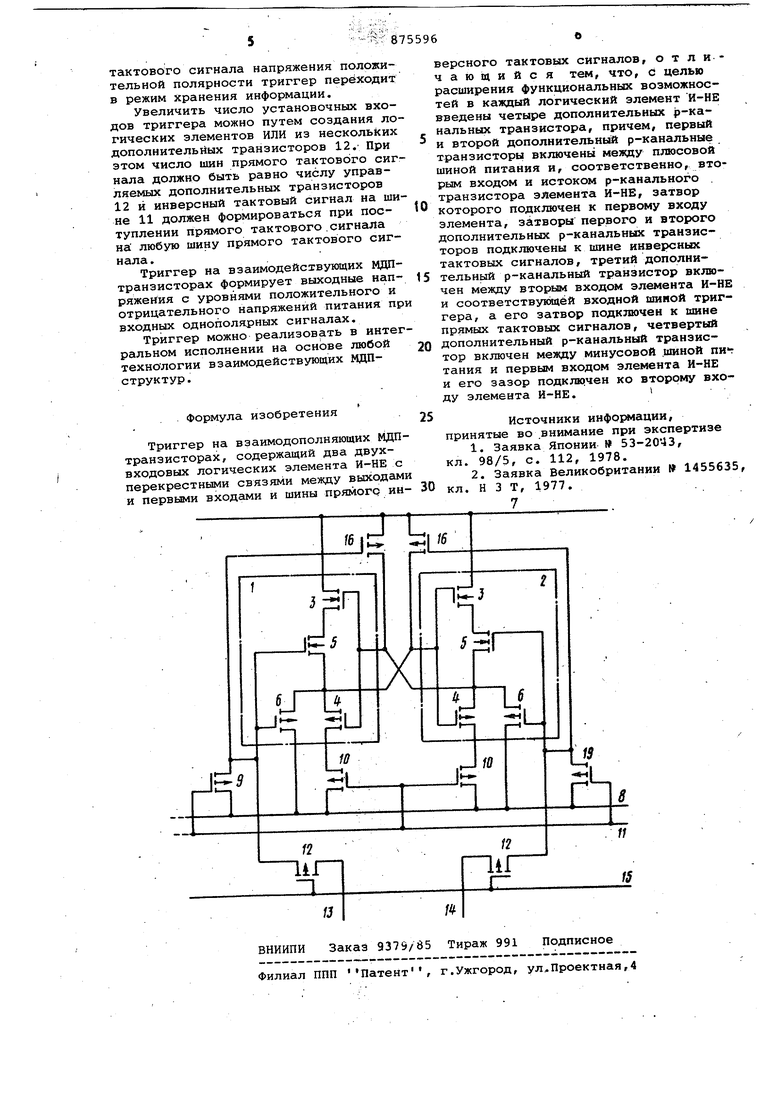

На чертеже представлена электрическая принципиальная схема предлагаемого триггера с индуцированными каналами.

Триггер содержит пе1рвый и второй двухвходовые логические элементы 1 и 2 И-НЕ, каждый из которых состоит из первой пары транзисторов 3 и 4 и второй пары транзисторов 5 и 6. Затворы транзисторов каждой пары являются, соответственно, первым и вторым в:}содом элемента. Транзисторы 3 и 5 с каналом п-типа включены последовательно между выходом элемента и минусовой шиной 7, а р-канальный транзистор 6 включен между выходом элемента и плюсовой шиной 8. Первые входы элементов 1 и 2 перекрестно подключены к их выходам. Первые и вторые дополнительные р-канальные транзисторы 9 и. 10 включены между шиной 8, и соответственно, вторым входом элементов 1 и 2 и истоком транзисторов 4, затворы транзисторов 9 и 10 подключены к шине 11 инверсных тактовых сигналов. Тр.етьи дополнительные р-канальные транзисторы 12 включены между вторым входом элементов 1 и 2 и соответствующей входной шиной 13 и 14 триггера, и их затворы подключены к шине 15 прямых тактовых сигналов.

Четвертые дополнительные р-канальные транзисторы 16 включены между шиной 7 и первым входом элементов 1 и 2 а их затворы подключены соответственно, ко второму входу элементов 1 и 2.

Устройство работает следующим образом.

На входные шины 13 и 14 при записи информации поступают противофазны управлякяцие сигналы с уровнем логического нуля, соответствующем нулевому уровню напряжения и уровнем логической единицы, соответствующем уровню, близкому к уровню напряжения питания положительной полярности.

на шины 15 и 11 поступают противофазные двуполярные сигналы с уровнями, близкими по величине напряжениям питания положительной и отрицательной полярности.

В режиме хранения информации на шину 10 поступае отрицательное нап. ряжение, а на шину 15 поступает напряжение положительной полярности. Пр этом транзисторы 10 открыты и обеспечивают поступление напряжения положительной полярности на р-канальны транзистор 4 первой пары транзисторо у логических элементов И-НЕ 1 и 2. Третьи дополнительные транзисторы 12 отключают вторые входы логических элементов 1 и 2 И-НЕ (затворы транзисторов 5 и 6) от шин 13 и 14. Дополнительные транзисторы 9 открыты и обеспечивают поступление напряжения положительной полярности на вторые входы логических элементов 1-2, что в свою очередь обеспечивает поддержание р-канальных транзисторов 6 и 16 в закрытом состоянии, а п-канальных транзисторов 5 в открытом состоянии у обоих логических элементов 1 и .2 И-НЕ.

..: Таким образом, в режиме xpaHeHtyi триггер с перекрестными связями образуется транзисторами 3 - 5 и первого и второго логических элементов 1 и 2 И-НЕ и дополнительными транзисторами 10. В режиме записи информации на шину инверсного тактового сигнала 11 поступает положител.ьное напряжение, а на шину 15 прямого тактового сигнала поступает напряжение отрицательной полярности.

При этом дополнительные транзисторы 10 закрываются и отключают истоки Р -канальных транзисторов 4 от шины 8 питания напряжения положительной полярности. Дополнитель ные транзисторы 9 также закрываются. Третьи дополнительные транзисторы 12 открываются и подключают вторые входы логических элементов 1 и 2 И-НБ к соответствующим входным шинам 13 и 14. В логическом элементе И-НЕ на второй вход которого поступает сигнал с нулевым уровнем напряжения р-канальный транзистор 6 открывается, а п-канальный транзистор 5 увеличивает свое сопротивление. Подключенный к этому второму входу затвором четвертый дополнительный транзистор 16 при исходном положительнс напряжении на истоке открывается и обеспечивает дополнительный ток, ускоряющий формировани начального участка отрицательного напряжения на выходе другого логического элемента И-НЕ, в котором положительное напряжение на вторсм входе обеспечивает закрытое состояние р-канальн6го транзистора 6 и открытое состояние п-канального транзистора 5.

В зависимости .от исходного состояния и от противофазных логических уровней напряжений, присутствукнцих на шинах 13 и 14, состояние триггера изменяется, либо подтверждается предьдущее.

При поступлении на шину 11 инверсного тактового сигнала отрицательного напряжения, а на шину 15 прямого тактового сигнала напряжения положительной полярности триггер переходит в режим хранения информации. Увеличить число установочных входов триггера можно путем создания ло гических элементов ИЛИ из нескольких дополнительных транзисторов 12. При этом число шин прямого тактового сиг нала должно быть равно числу управляемых дополнительных транзисторов 12 и инверсный тактовый сигнал на ши не 11 должен формироваться при поступлении прямого тактового .сигнала ни любую шину прямого тактового сигнала . Триггер на взаимодействующих МДПтранзисторах формирует выходные напряжения с уровнями положительного и отрицательного напряжений питания пр входных однополярных сигналах. Триггер можно реализовать в интег ральном исполнении на основе любой технологии взаимодействующих МДПструктур. . Формула изобретения Триггер на взаимодополняющих МДПтранзисторах, содержащий два двухвходовых логических элемента И-НЕ с перекрестными связями между выходами и первыми входами и шины прямогр инвареного тактовых сигналов, отличающийся тем, что, с целью расширения функциональных возможностей в каждый логический элемент И-НЕ введены четыре дополнительных р-канальных транзистора, причем, первый и второй дополнительный р-канальные транзисторы включены между плюсовой шиной питания и, соответственно, вторым входом и истоком р-канального транзистора элемента И-НЕ, затвор которого подключен к первому входу элемента, затворы первого и второго дополнительных р-канальных транзисторов подключены к шине инверсных тактовых сигналов, третий дополнительный р-канальный транзистор включен между вторым входом элемента И-НЕ и соответствующей входной шиной триггера, а его затвор подключен к шине прямых тактовых сигналов, четвертый дополнительный р-канальный транзистор включен между минусовой .шиной пи тания и первым входом элемента И-НЕ и его зазор подключен ко второму входу элемента И-НЕ. Источники информации, принятые во .внимание при экспертизе 1.Заявка Японии 53-20 43, кл. 98/5, с. 112, 1978. 2.Заявка Великобритании 1455635, кл. И 3 Т, 1977.

Авторы

Даты

1981-10-23—Публикация

1980-02-29—Подача