Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки узлов цифровых вычислительных машин, например микросх.ем.

Известно устройство для контроля цифровых узлов, содержащее генератор импульсов, двоичный счетчик, элемент И, эталонную микросхему, индикаторы, блок сравнения, ключ установки в исходное состояние

Недостатком этого устройства является то, что на входы проверяемой и эталонной микросхем подаются кодовые комбинации, определяемые всеми состояниями двоичного счетчика, хотя среди них имеются запрещенные состояния.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля цифровых узлов , содержащее генератор импульсов, двоичный счетчик, элемент И, эташонную микросхему, индикаторы, блок сравнения, ключ установки в исходное состояние, генератор одиночного импульса, ключ одиночного шага, блок исключения запрещенных состояний, два элемента ИЛИ С2.

Однако в данном устройстве на вход проверяемой и эталонной микросхем также подаются кодовые комбинации двоичного счетчика, среди которых имеются и запрещенные. Если в проверяемой микросхеме имеются RS-триггеры, то после подачи на входы R и S запрещенных комбинаций триггеры переходят в нерднозначные состояния, оп10ределяемые только асимметрией их схем. Это может привести к тему, что в результата подачи запр денных входных сигналов, -триггеры проверяемой и эталонной микросхем устанавливаются в

15 различные состояния, после чего дальнейшая проверка микросхем становится недостоверной. В известном устройстве блок исключения запргацеиных состояний только маскирует сигнал с блока

20 сравнения при подаче на входы проверяемой и эталонной микросхем запрещенных ксжбинаций, т.е. данное устройство не позволяет осуществлять достоверный контроль схем с RS -триг25герс1ми.

Цель изобретения - повьшение достоверности контроля.

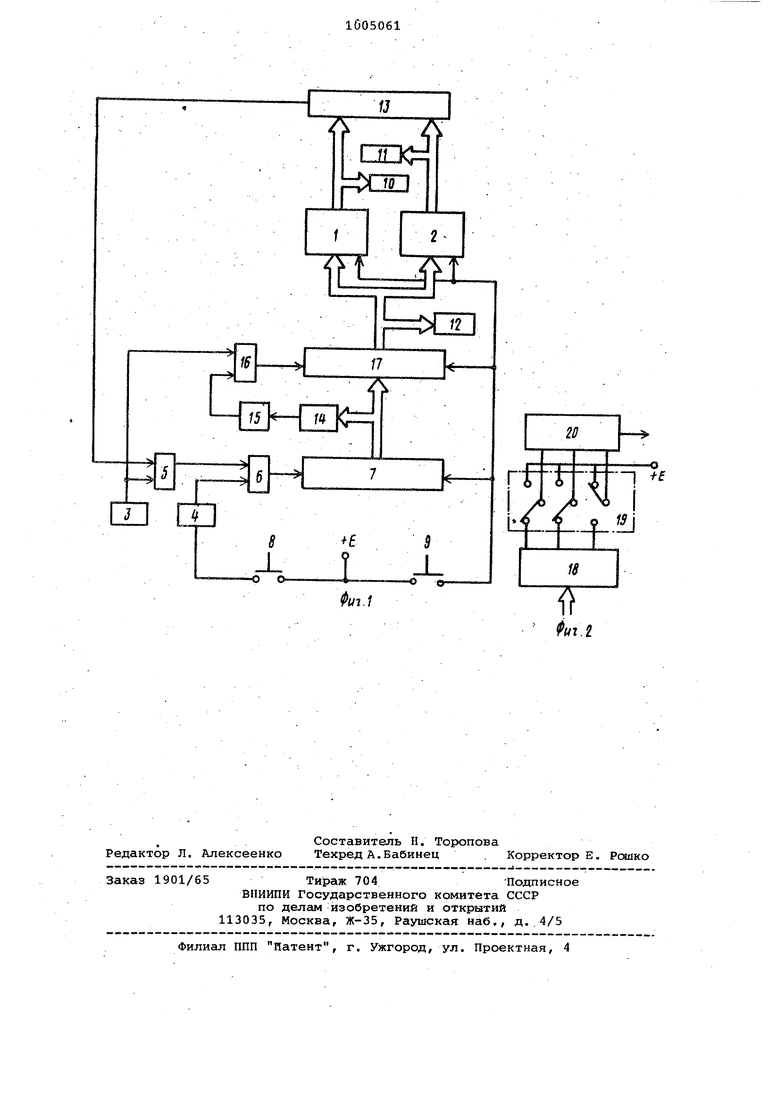

Поставленная цель достигается тем, что в устройство для контроля цифро30вых узлов, содержащее счетчик, эталонный узел, генератор импульсов, генератор одиночного импульса, .первы элемент И, элемент ИЛИ, пёреключ теля, три блока индикации,, блок срав .нения запрещенных состояний, причем выходы счетчика соединены соответственно с входами блока исключения запрещенных состояний вход генератора одиночного импульса через первый переключатель соединен с шиной положительн го потенциала, выход генератора одиноч ного импульса соединен с пе.рвым входом элементаИЛИ,второй вход которогосоед нен с выходом первого элемента И,выход Элемента ИЛИ связан со счетным входо счетчика, установочные входы счетчика, этало нного узла и проверяемого узла подключены через второй переключатель к шине положительного поте цила, выходы проверяемого узла соеди нены с первой группой входов блока сравнения и с входами первого блока индикации, выходы эталонного узла со единены с второй группой входов блока сравнения и с входами второго блока индикации,.выход блока сравнения подключен -к первому входу первого элемента И, второй вход котот рого соединен с выходом генератора импульсов, введены регистр, элемент НЕ, второй элемент И, выход которого соединен с управляющим входом регист ра, установочный вход которого соединен с установочным входом счетчика а информационные входы регистра соединены с выходами счетчика, выходы регистра соединены соответственно с входами проверяемого узла, с входами эталонного узла, с входами третьего блока индикации, выход блока исключения запрещенных состояний соединен со входом элемента НЕ, выход которого соединен с первым вхо дом второго элемента. И, второй вход которого соединен с выходом генератора импульсов. На фиг, 1 представлена схема устройства на фиг. 2 - схема блока искдючения запрещенных состояний. Устройство содержит проверяемый 1 и эталонный 2 цифровые узлы, генератор 3 импульсов, генератор 4 одиночного импульса, элемент И 5, элемент ИЛИ б, счетчик 7, первый переключатель 8 , второй переключатель 9 блоки 10, 11 и 12 индикации, блок 13 сразвнения, блок 14 исключения запрещенных состояний, элемент НЕ 15, элемент И 16, регистр 17. Блок исключения запрещенных состо яний (фиг. 2) состоит из дешифратора 18, переключателей 19 и элемента ИЛИ 20. Проверка цифрового узла начинаетс с включения переключателя 9. При этом происходит сброс счетчика 7, регистра 17, проведя -ого 1 и эталон ного 2 узлов в начальное состояние. Блок 10 индикации п.оказывает нулевое состояние, соответствукицее комбинации логических уровней, поданных на входы узлов 1 и 2. Если при этом .на входах узлов 1 и 2 одинаковые комбинации логических уровней, то блоки 12 и 11 индикации показывают одинаковые числа, а блок 13 сравнения вьщает на вход элемента И 5 разрешающий сигнал и очередной импульс с генератора 3 проходит через элемент ИЛИ 6 на вход счетчика 7. По переднемз фронту этого импульса счетчик 7 изменяет свое состояние на единицу. Новое состояние счетчика 7 поступает на входы регистра 17 и блока 14 исключения запрещенных состояний.. Переключатель 19 блока 14 исключения запрещенных состояний, соответствующий запрещенным состояниям, устанавливается в положение, при котором выходы дешифратора 18 соединены с входами элемента ИЛИ 20. При появлении на выходе счетчика 7 разрешенной комбинации -блок 14 формирует на своем выходе нулевой потенциал, который через элемент НЕ поступает на вход элемента И 16. Благодаря этому импульс от генератора 3 поступает на управляющий вход регистра 17. По заднему фронту этого импуль са состояние счетчика 7 записывается в регистр 17 и поступает на входы проверяемого 1 и эталонного 2 узлов. При появлении на выходе счетчика 7 комбинации логических уровней, представляющей запрещенное состояние, на одном из выходов дешифратора 18 возникает единичный потенциал, которалй через соответствующий переключатель 19, элемент ИЛИ 20 и элемент НЕ 15 поступает Ка вход элемента И 16. Вследствие этого, импульс от генератора 3 не проходит на управляющий вход регистра 17. Таким образом, запрещенная комбинация не записывается в регистр 17 и не поcTynaei; на входы цифровых узлов 1 и 2-. Если при подаче логической комбинации на входы узлов 1 и 2 на их выходах формируются различные состояния, с блока 13 сравнения поступает на вход элемента И 5 запрещакиций потенциал и импульс с выхода генератора 3 не поступает на вход счетчика 7. По показаниям блоков 10, 11 и 12 индикации можно заре- : гистрировать логические уровни на ; входах и выходах узлов 1 и 2. Для продолжения проверки в этом случае необходимо включить переключатель 8. Генератор 4 вьвдает один импульс,который изменяет состояние счетчика на единицу, далее процесс повторяется. Введение в устройство регистра 17, элемента И 16 и элемента НЕ 15 позволяет исключить запрещенные комбина;ции из числа наборов логических уровней, поступающих на входы проверяемого и этгшонного цифровых узлов, -r&t Ссшым увеличить достоверность контро- ля, обеспечить контроль элементов паг мяти с запрещенными входными воздейСТВИЯМЙ.

Формула изобретения

Устройство для контроля цифровых 10 узлов,.содержащее счетчик, эталонный узел, генератор импульсов, генератор одиночного импульса, первый элемент И, элемент ИЛИ, два переключателя, три блока индикации,блок сравнения, блок исключения запрещенных состояний, причем выходы счетчик|1 соединены соответственно с входгши блока исключения запрещенных состояний, вход генератора одиночного импульса через 20 первый переключатель соединен с шиной положительного потенциала, выход генератора одиночного импульса соединен с первым входсж элемента ИЛИ, второй вход которого соединен с 25 выходом первого элемента И, выход элемента ИЛИ связан со счетным входом счетчика, установочные входы счетчика, эталонного узла и проверяемого узла подключены через второй ЗО переключатель к шине положительного потенциала, выхрды проверяемого узла соединены с первой группой входов блока сравнения и с входами первого блока индикации, выходы этало1гного узла соединены с второй группой входов блока сравнения и с входами ; второго блока индикации, выход блока сравнения подключен к первому входу первого элемента И, второй гход которого соединен с выходом генератора импульсов, от. личaющee с я тем, что, с целью повьшения достоверности контроля, в устройство введены регистр, элемент НЕ, второй элемент И, выход которого соединен с управляющим входом регистра, устано-f точный вход котЬрого соединен с установочным входом счетчика, а информа ционные входы регистра соедине1Ш. с выходгши счетчика,. выходы регистра соединены соответственно с входг1ми проверяемого узла, с входами эталонного узла, с входами третьего блока индикации, выход блока исключения запрещенных состояний соединен с входом элемента НЕ, выход которого соединен с nejiBim входом второго зле- . мента И, второй вход которого соединен с выходом генератора импульсов.

Источники информации, принятые во внимание при экспертизе

1.Универсальный логический тестор для проверки микросхем в производстве. - Электроника М., Мир,. /, 1974, 8, с. 65-67.

2.Авторское свидетельство СССР №648981, кл. G 06 F 11/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микросхем | 1977 |

|

SU648981A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1383370A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-28—Подача