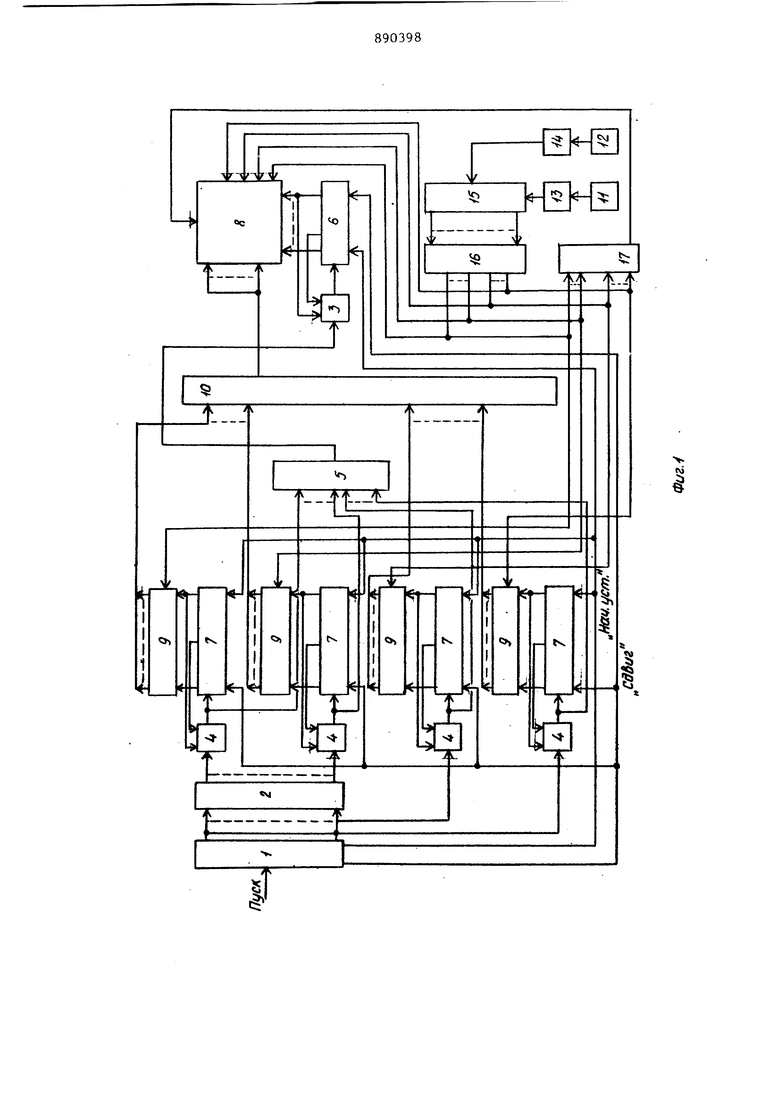

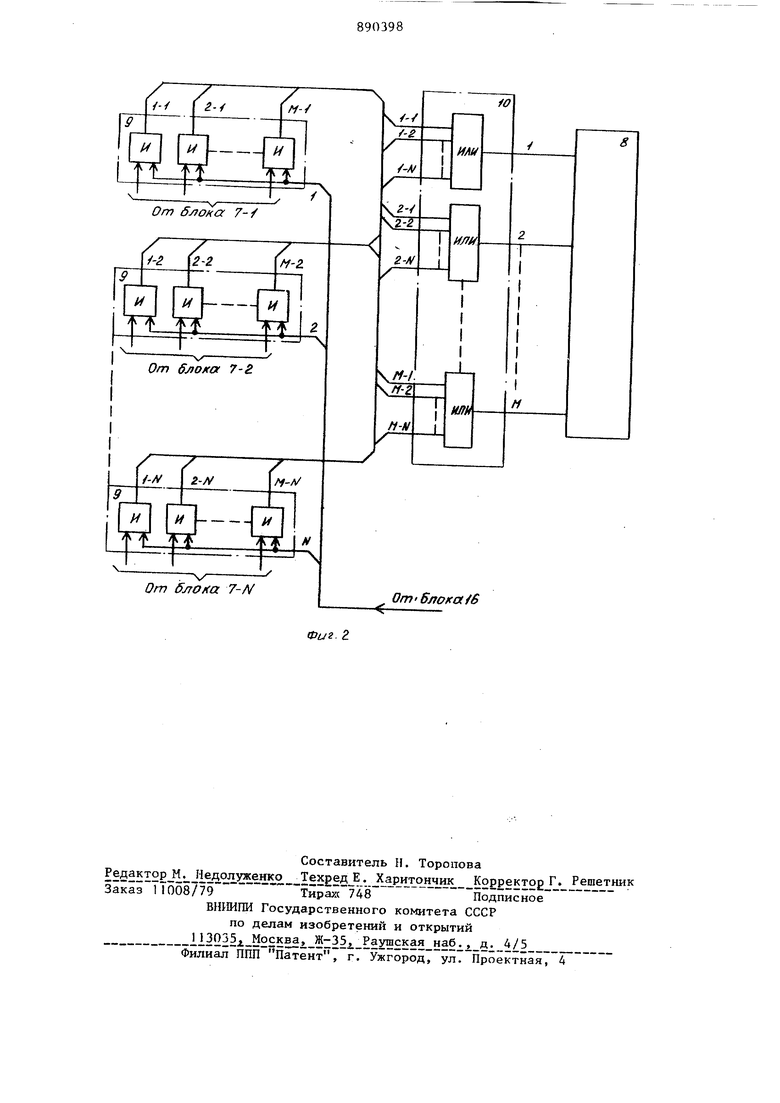

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля цифровых уз лов автоматики и вычислительной техники. Известно устройство для контроля цифровых узлов, содержащее генератор тестов, последовательно соединенные блок свертки по модулю два и сумматор по модулю два, выход которого подключен ко входу регистра сдвига, а группа информациошшх входов - к группе информационных выходов регистра сдвига, подключенных к группе входов индикатора, управляющий и установочный выходы генератора тестов подключены к соответствующим входам регистра сдвига l. Недостатком устройства является не чувствительность к ощибкам четной кратности. Наиболее близким по технической сущности к предлагаемому является устройство для контроля многовыходных цифровых узлов, содержащее генератор тестов, последовательно соединенные блок свертки по модулю два и первый сумматор по модулю два, выход которого подключен ко входу первого регистра сдвига, а группа информационных входов - к группе информационных выходов первого регистра сдвига, подключенных к группе входов индикатора,управляющий и установочный выходы генератора тестов подключены к соответствующим входам первого регистра сдвига, группу регистров сдвига и группу сумматоров по модулю два, первые информационные входы которых являются группой информационных входов устройства, выходы подключены к группе входов блока свертки по модулю два и к информационным входам вторых регистров группы, выходами подключенных ко вторым информационным входам сумматоров по модулю два группы, а установочными и управлякхцими входами - к управляющему 38 и установочному выходу генератора тестов соответственно ГзД.. Недостатком устройства является малая глубина контроля в виду того, что ycTpoiicTBO фиксирует лишь результат Годен или Брак и отсутствует диагностическая информация о месте неисправности. Цель изобретения - увеличение глубины контроля. Поставленная цель достигается тем что в устройство для контроля логических узлов, содержащее еенератор тестов, две группы сумматоров, по модулю два, две группы регистров сдвига, узел свертки по модулю два, выходной сумматор по модулю два, выходной регистр сдвига, узел индикации Причем группа выходов генератора тестов соединена соответственно с первыми входами сумматоров по модулю два первой группы и со входами проверяемого логического узла, выходы которого соединены соответственно с первыми входами сумматоров по модулю два второй группы, выходы которых соединены соответственно с информационными входами регистров сдвига второй группы и с первой группой входов узла свертки по модулю два, выходы сумматоров по модулю два первой группы соединены соответственно с информационными входами регистров сдвига первой группы и со второй группой входов узла свертки по модулю два, выходь регистров сдвига первой группы соединены соответственно со входами сумматоров по модулю два первой группы, выходы регистров сдвига второй группы соединены соответственно со входами сумматоров по модулю два второй группы, выход узла свертки соединен с первым информационным входом выходного сумматора по модулю два, выход которого соединен с информационным входом выходного регистра сдвига, группа выходов которого соединена с группой информационных входов выходного сумматора и с первой группой информационных входов блока, индикации, вход начальной установки регистров сдвига первой и второй группы и выходного регистра сдвига соединен с установочным выходом генератора тестов синхро низируюощй выход которого соединен с синхровходами регистров сдвига первой и второй группы и выходного регистра, управляющий вход генератора тестов является управляющим входом устройства, введены дешифратор, счетчик, первы11 переключатель, второй переключатель, два формирователя одиночных импульсов, две группы коммутаторов, блок селекторов, элемент Ш1И, причем выход первого переключателя соединен со входом первого формирователя одиночных импульсов, выход которого соединен с информационным входом счетчика, вход начальной установки которого соединен с выходом второго формирователя одиночных импульсов, вход которого соединен с выходом второго переключателя, группа счетчика соединена с группой входов дешифратора, выходы которого соединены соответственно с управляющими входами коммутаторов первой и второй группы, с управляющими входами блока индикации и со входами элемента ИЛИ, выход которого соединен с первым управляющим входом блока индикации, вторая группа информационных входов которого соединена соответственно с группой выходов блока селекторов, входы которого соединены соответственно с выходами коммутаторов первой и второй групп, информационные входы коммутаторов первой группы соединены соответственно с выходами регистров сдвига первой группы, информационные входы коммутаторов второй группы соединены соответственно с выходами регистров сдвига второй группы. На фиг. 1 показана схема устройства; на фиг. 2 - схема коммутаторов и схема блока селекторов. Устройство содержит генератор тестов 1, проверяемый блок 2, выходной сумматор 3 по модулю два, группы сумматоров 4 по модулю два, блок 5 свертки по модулю два, выходной регистр 6 и группу регистров 7 сдвига, блок 8 индикации, коммутаторы 9, блок 10 селекторов, переключатели 11 и 12, формирователи одиночных импульсов 13 и 14, счетчик 15, дешифратор 16, элемент ИЛИ 17, Работа устройства начинается с подачи сигнала начальной установки Исх, генератором тестов 1, по которому регистры 6 и 7 устанавливаются в начальное состояние. По нажатию переключателя 12 формирователь одиночных импульсов 14 вырабатывает импульс, который устанавливает счетчик 15 в состояние, при котором на всех выходах дешифратора 16 нулевая информация и блок индикации 8 58 по нулевому сигналу элемента ИЛИ 17 под(отовлен к отображению информации с регистра 6. При этом все коммутаторы 9 закрыты по управляющим входам с дешифратора 16, и информация с блока селекторов 10 не поступает на блок индикации В. По сигналу Пуск генератор вьщает первый тест, который поступает на входы проверяемого узла 2, Информация с каждого вывода проверяемого узла 2 поступает на вход сумматора 4, а с его выхода на вход регистра 7 и один из входов блока 5. Ре зультат с выхода блока 5 поступает на сумматор 3, а с его выхода - на ход регистра 6. Запись результата первого теста производится по сигналу Конец теста с генератора 1. Информация поканально записывается в первые разряды регистров 7, а общий результат в первый разряд регистра 6, Затем генератор реализует второй тест. По сигналу Конец теста второй знак информации с выводов проверяемого устройства записывается в первйе разряды регистров 7, а предыдущее зна чение информации, записанное в первых разрядах сдвигается во второй разряд. ОдпОБремепно осуществляется свертка по модулю два второго знака информации на блоке 5 и запись его в первый разряд регистра 6, а также значения первого знака информации во второй разряд и т.д.

В результате реализации всех тестов в каждом канале проверяемого узла осуществляется сжатие последовательности сигналов на сумматорах 4 и регистрах 7. Блок 5 производит преобразование последовательностей сигналов с выводов изделия в одну последовательность, которая сжимается на сигнатурном анализаторе (регистр 6 с сумматором по модулю два в цепи обратной связи. Результат контроля в виде сигнатуры индицируется на блоке индикации В.

Измеренное таким образом значение сигнатуры сравнивается теперь с эталонным значением, зафиксированным в технической документации на данный узел. Узел признается годным в случае совпадения значений измеренной и эталонной сигнатуры. В противном случае, изделие бракуется и переходит ко второму этапу контроля - определению места неисправности.

Формула изобретения

Устройство для контроля логических узлов, содержащее генератор тестов, две группы сумматоров по модулю два, две группы регистров сдвига, узел свертки по модулю два, выходной сумматор по модулю два, выходной регистр сдвига, узел индикации, причем группа выходов генератора тестов соединена соответственно с первьоми входами сумматоров по модулю два первой группы и со входами проверяемого логического узла, выходы которого соединены соответственно с первыми входами сумматоров по модулю два второй группы, выходы которых соединены соответственно с информационными входами регистров сдвига второй группы и с первой группой входов узла свертки по модулю два, выходы сумматоров по модулю два первой группы соединены соответствен8Для этого нажимают переключатель 11. Формирователь 13 вырабатывает одиночный импульс, который поступает на счетный вход счетчика 15. На одном из выходов дешифратора возникает сигнал логической единицы, который открывает один из коммутаторов 9. При этом информация с одного из регистров 7 через открытьй коммутатор 9 поступает на блок индикации 8, на который с элемента ИЛИ I7 подается логическая единица, которая запрещает индикацию на нем информации с регистра 6 и разрешает индикацию информации с выбранного регистра 7. Для просмотра сигнатуры с другого регистра 7 необходимо последовательным нажатием переключателя 11 установить на счетчике 15 двоичное число, соответствующее номеру проверяемого вывода. При этом номер контролируемого вывода проверяемого узла индицируется на том же блоке индикации 8. Затем снятые сигнатуры сравниваются с эталонными значениями. Таким образом, увеличение глубины контроля в устройстве достигается за счет снятия сигнатур с выходов контродируемого изделия и получения дополнительной информации о месте неисправности с точностью до внешнего вывода. Устройство просто в эксплуатации и не требует привлечения высококвалифицированного персонала.

но с информационными входами регистров сдвига первой группы и со второй группой входов узла свертки по модулю два, выходы регистров сдвига первой группы соединены соответственно со входами сумматоров по модулю два первой группы, выходы регистров сдвига . второй группы соединены соответственно со входами сумматоров по модулю два второй группы, выход узла свертки соединен с первым информационным входом выходного сумматора по модулю два, выход которого соединен с информационным .входом выходного регистра сдвига, группа выходов которого соединена с группой информационных входов выходного сумматора и с первой группой информационных входов блока индикации,вход начальной установки регистров сдвига первой и второй группы и выходного регистра сдвига соединен с установочным выходом генера -ора тестов, синхронизирующий выход которого соединен с синхровходами регистров сдвига первой и второй группы и выходного регистра, управляющий вход генератора тестов является управляющим входом устройства, отличающееся тем, что с целью увеличения глубины контроля, в устройство введены дешифратор, счетчик, первый переключатель, второй переключатель, дна формирователя одиночных импульсов, две группы коммутаторов блок селекторов, элемент ИЛИ, причем выход Первого переключателя соединен

|СО входом первого формирователя одиночных импульсов, выход которого соединен с информационным входом счетчика, вход начальной установки которого соединен с выходом второго формирователя одиночных импульсов, вход которого соединен с выходом второго переключателя, группа выходов счетчика соединена с группой входов дешифратора, выходы которого соединены соответственно с управляющими входами коммутаторов первой и второй группы, с управляющими входами блока индикации и со входами элемента ИЛИ, выход itoToporo соединен с первым управляющим входом блока индикации, вторая группа информационных входов которого соединена соответственно с группой выходов блока селекторов, входы которого соединены соответственно с выходами коммутаторов первой и второй групп, информационные входы коммутаторов первой группы соединены соответственно с выходами регистров сдвига первой группы, информационные входы коммутаторов второй группы соединены соответственно с выхоДами регистра сдвига второй группы.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 706849, кл. Q 06F П/04, 1979.

2.Заявка СССР 2769899/18-24, кл. Gi 06 Р 11/04, 1979 (прототип.

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля многовы-ХОдНыХ цифРОВыХ узлОВ | 1979 |

|

SU817721A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

Авторы

Даты

1981-12-15—Публикация

1980-02-07—Подача