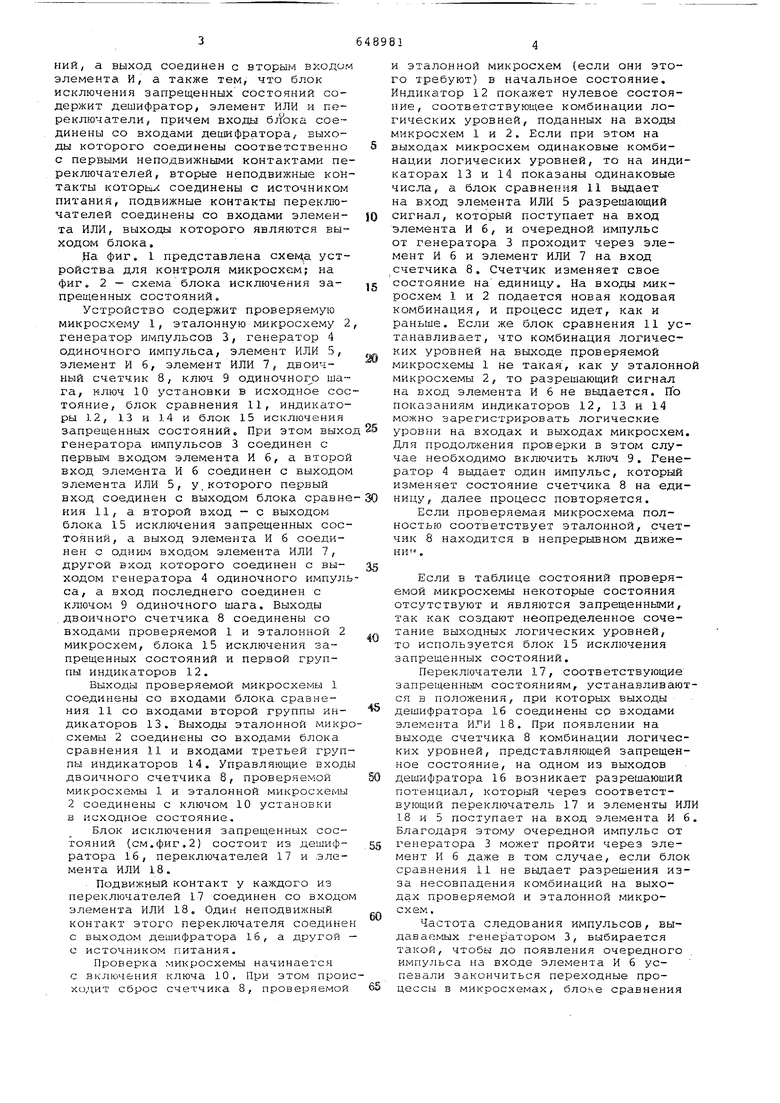

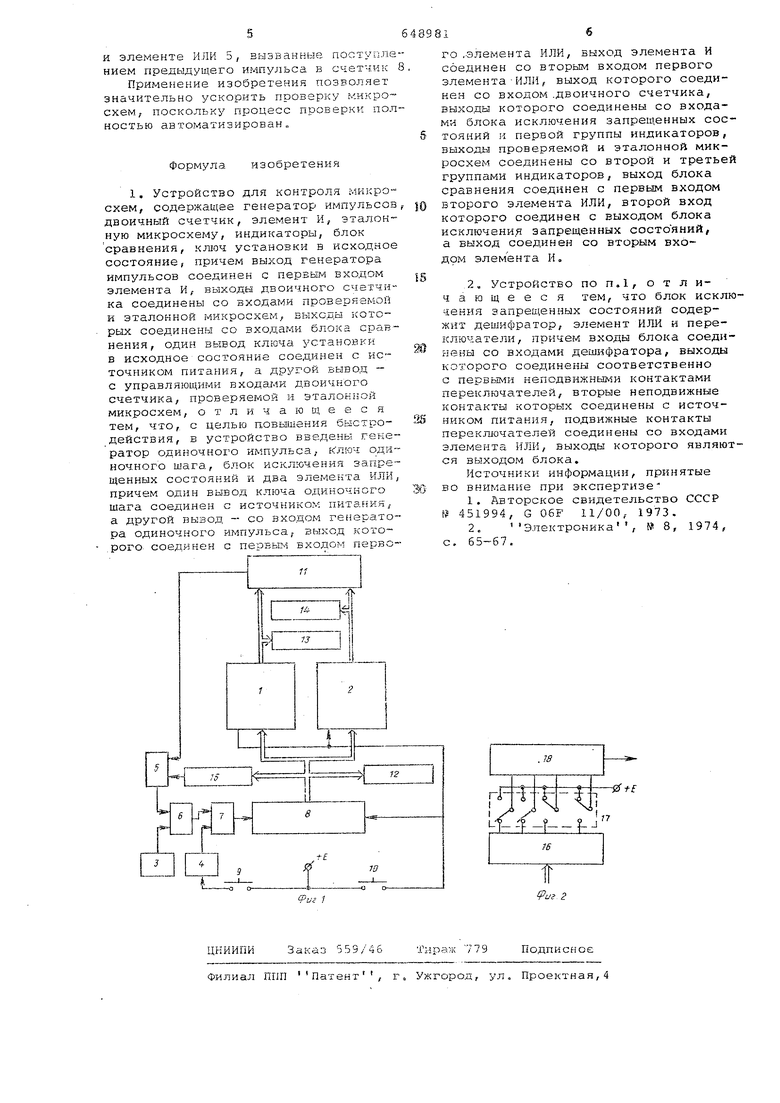

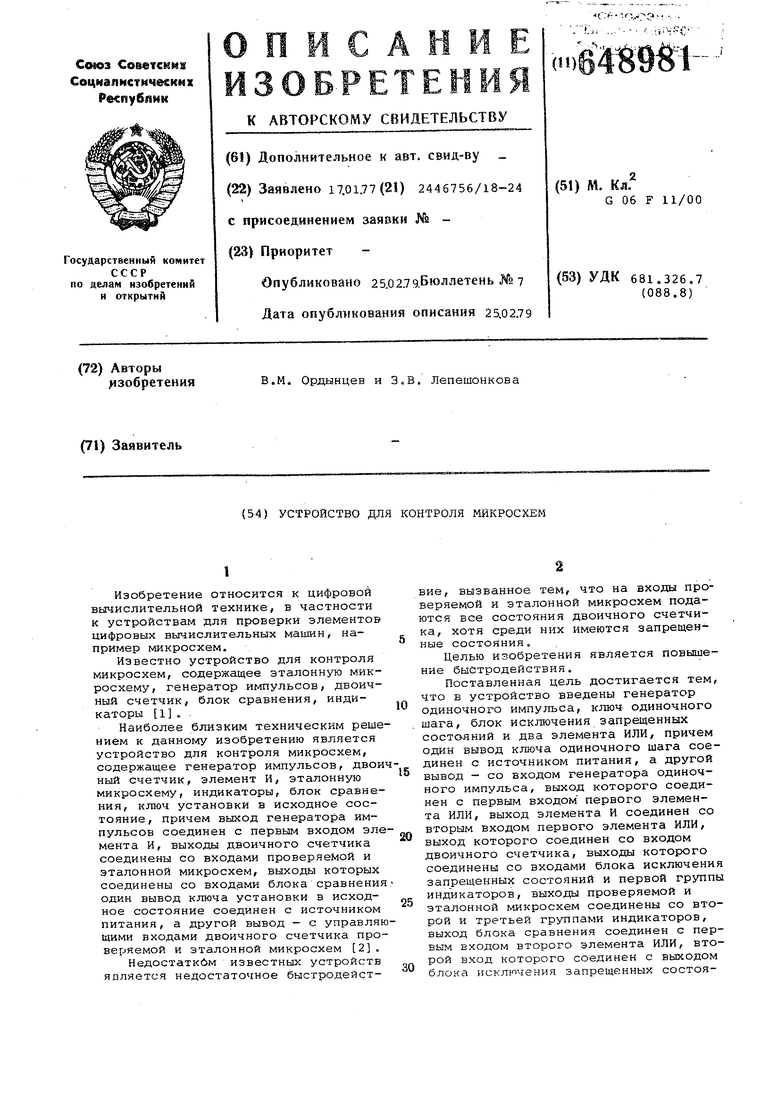

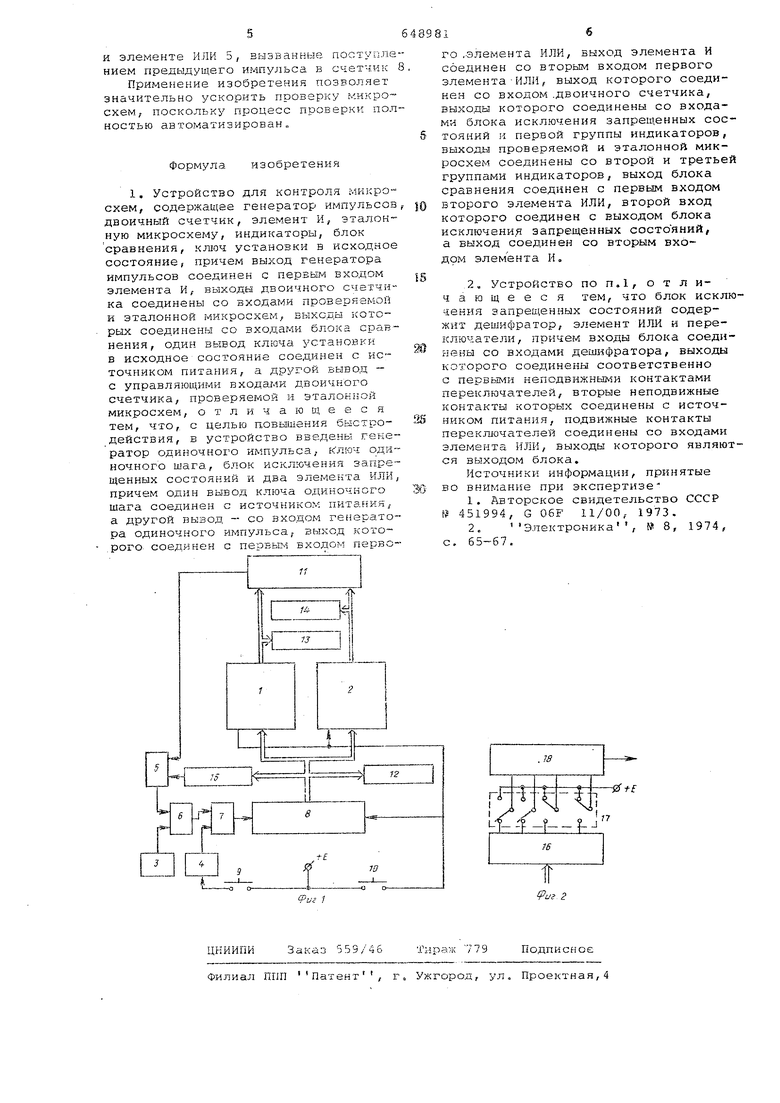

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки элементов цифровых вычислительных Машин, например микросхем. Известно устройство для контроля микросхем, содержащее эталонную микросхему, генератор и шульсов, двоичный счетчик, блок сравнения, индикаторы 1 . . Наиболее близким техническим реше нием к данному изобретению является устройство для контроля микросхем, содержащее генератор импульсов, двои ный счетчик, элемент И, эталонную микросхему, индикаторы, блок сравнения, ключ установки в исходное состояние, причем выход генератора импульсов соединен с первым входом эле мента И, выходы двоичного счетчика соединены со входами проверяемой и эталонной микросхем, выходы которых соединены со входами блока сравнения один вывод ключа установки в исходное состояние соединен с источником питания, а другой вывод - с управляю щими входами двоичного счетчика про веряемой и эталонной микросхем 2. Недостатком известных устройств является недостаточное быстродействие, вызванное тем, что на входы проверяемой и эталонной микросхем подаются все состояния двоичного счетчика, хотя среди них имеются запрещенные состояния. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство введены генератор одиночного импульса, ключ- одиночного шага, блок исключения запрещенных состояний и два элемента ИЛИ, причем один вывод ключа одиночного шага соединен с источником питания, а другой вывод - со входом генератора одиночного импульса, выход которого соединен с первым входом первого элемента ИЛИ, выход элемента И соединен со вторым входом первого элемента ИЛИ, выход которого соединен со входом двоичного счетчика, выходы которого соединены со входами блока исключения запрещенных состояний и первой группы индикаторов, выходы проверяемой и эталонной микросхем соединены со второй и третьей группами индикаторов, выход блока сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом блока исключения запрещенных состояПИЙ, а выход соединен с вторым входом элемента И, а также тем, что блок исключения запрещенных состояний содержит дешифратор, элемент ИЛИ и переключатели, причем входы блЪка соединены со входами дешифра.тора,- выходы которого соединены соответственно с первыми неподвижными контактами пе реключателей, вторые неподвижные ком такты KOTOpbix соединены с источником питания, подвижные контакты переключателей соединены со входами элемента ИЛИ, выходы которого являются выходом блока. На фиг. 1 представлена схеца устройства для контроля микросхем; на фиг 2 - схема блока исключения запрещенных состояний. Устройство содержит проверяемую микросхему 1, эталонную микросхему 2 генератор импульсов 3, генератор 4 одиночного импульса, элемент ИЛИ 5, элемент И 6, элемент ИЛИ 7, двоичный счетчик 8, ключ 9 одиночног,о шага, ключ 10 sCTaHOBKH в исходное сос тояние, блок сравнения 11, индикаторы 12, 13 и 14 и блок 15 исключения запрещенных состояний. При этом выхо генератора шмпульсов 3 соединен с первым входом элемента И б, а второ вход элемента И б соединен с выходом элемента ИЛИ 5, у,которого первый вход соединен с выходом блока сравн ния 11, а второй вход - с выходом блока 15 исключения запрещенных сос тояний, а выход элемента И б соединен с одним входом элемента ИЛИ 7, другой вход которого соединен с выходом генератора 4 одиночного импул са, а вход последнего соединен с ключом 9 одиночного шага. Выходы двоичного счетчика 8 соединены со входами проверяемой 1 и эталонной 2 микросхем, блока 15 исключения запрещенных состояний и первой группы индикаторов 12. Выходы проверяемой микросхемы 1 соединены со входами блока сравнения 11 со входами второй группы индикаторов 13. Выходы эталонной микр схемы 2 соединены со входами блока сравнения 11 и входами третьей груп пы индикаторов 14, Управляющие вход двоичного счетчика 8, проверяемой микросхемы 1 и эталонной микросхемы 2 соединены с ключом 10 установки в исходное состояние. Блок исключения запрещенных состояний (см.фиг.2) состоит из дешифратора 16, переключателей 17 и .элемента ИЛИ 18. Подвижный контакт у каждого из переключателей 17 соединен со входо элемента ИЛИ 18, Один неподвижный контакт этого переключателя соедине с выходом дешифратора 16, а другой с источником питания. Проверка микросхемы начинается с включения ключа 10. При этом ПЕЗОИ ходит сброс счетчика 8, проверяемой и эталонной микросхем {если они этого требуют) в начальное состояние. Индикатор 12 покажет нулевое состояние, соответствующее комбинации логических уровней, поданных на входы микросхем 1 и 2. Если при этом на выходах микросхем одинаковые комбинации логических уровней, то на индикаторах 13 и 14 показаны одинаковые числа, а блок сравнения 11 вьщает на вход элемента ИЛИ 5 разрешающий сигнал, который поступает на вход элемента И б, и очередной импульс от генератора 3 проходит через элемент И 6 и элемент ИЛИ 7 на вход счетчика 8, Счетчик изменяет свое состояние на единицу. На входы микросхем 1 и 2 подается новая кодовая комбинация, и процесс идет, как и раньше. Если же блок сравнения 11 устанавливает, что комбинация логических уровней на выходе проверяемой микросхемы 1 не такая, как у эталонной микросхемы 2, то разрешающий сигнал на вход элемента И 6 не выдается. По показаниям индикаторов 12, 13 и 14 можно зарегистрировать логические уровни на входах и выходах микросхем, Для продолжения проверки в этом случае необходимо включить ключ 9, Генератор 4 выдает один импульс, который изменяет состояние счетчика 8 на единицу, далее процесс повторяется, Если проверяемая микросхема полностью соответствует эталонной, счетчик 8 находится в непрерывном движеЕсли в таблице состояний проверяемой микросхемы некоторые состояния отсутствуют и являются запрещенными, так как создают неопределенное сочетание выходных логических уровней, то используется блок 15 исключения запрещенных состояний. Переключатели 17, соответствующие запрещеннЕлм состояниям, устанавливаются в положения, при которых выходы дешифратора 16 соединены ср входами элемента ИТИ 18. При появлении на выходе счетчика 8 комбинации логических уровней, представляющей запрещенное состояние, на одном из выходов дешифратора 16 возникает разрешающий потенциал, который через соответствующий переключатель 17 и элементы ИЛИ 18 и 5 поступает на вход элемента И 6. Благодаря этому очередной импульс от генератора 3 может пройти через элемент И 6 даже в том случае, если блок сравнения 11 не выдает разрешения изза несовпадения комбинаций на выходах проверяемой и эталонной микросхем. Частота следования импульсов, выдав ае, генератором 3, выбирается такой, чтобы до появления очередного импульса на входе элемента И 6 успевали закончиться переходные процессы в микросхемах, блоке сравнения

и элементе ИЛИ 5, вызванные поступлением предыдущего импульса в счетчик 8.

Применение изобретения позволяет значительно ускорить проверку микросхем, поскольку процесс проверки полностью автоматизирован„

Формула изобретения

1, Устройство для контроля микросхем, содержащее генератор импульсов двоичный счетчик, элемент И, эталонную микросхему, инди1саторы, блок сравнения, ключ установки в исходное состояние, причем выход генератора импульсов соединен с первым входом элемента И, выходы двоичного счетчика соединены со входа 1И проверяемой и эталонной микросхем; выходы которых соединены со входами блока сравнения, один вывод ключа установки в исходное состояние соединен с источником питания, а другой вывод -с управляющими входами двоичного счетчика, проверяемой и эталонной микросхем, о т л и чающееся

с целью повышения быстротем, что, в устройство введеньз генедействия,

ратор одиночного импульса, ключ одиночного шага, блок исключения запрещенных состояний и два элемента ИЛИ, причем один вывод ключа одиночного шага соединен с источником питанияj а другой вывод - со входом генератора одиночного импульса, выход которого- соединен с первым входом первого .элемента ИЛИ, выход элемента И соединен со вторым входом первого элемента-ИЛИ, выход которого соединен со входом .двоичного счетчика, выходы которого соединены со входами блока исключения запрещенных состояний и первой группы индикаторов, выходы проверяемой и эталонной микросхем соединены со второй и третьей группами индикаторов, выход блока сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом блока исключения запрещенных состояний, а выход соединен со вторым входом элемента И„

S

2, Устройство по п.1, отличающееся тем, что блок исклю-leHHH запрещенных состояний содержит дешифратор, элемент ИЛИ и переключатели, причем входы блока соединены со входами дешифратора, выходы которого соединены соответственно с первыми неподвижными контактами переключателей, вторые неподвижные контакты которых соединены с источнике ом питания, подвижные контакты переключателей соединены со входами элемента ИЛИ, выходы которого являются выходом блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 451994, G Обр 11/00,- 1973.

№ 8, 1974,

Электроника

2, с. 65-67.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU1005061A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕЖИМАМИ СТРЕЛЬБЫ ЭЛЕКТРОИНИЦИИРУЕМЫХ ЗАРЯДОВ | 1993 |

|

RU2072072C1 |

| Устройство для проверки логических микросхем | 1988 |

|

SU1596291A1 |

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

Авторы

Даты

1979-02-25—Публикация

1977-01-17—Подача