1

Изобретение относится к вычислительной технике, электронике и, в частности, может быть использовано при разработке БИС на дополнительных МДП транзисторах.

Известен многофункциональный логический элетлент, существенным признаком которого является исполЕ)30вание ступенчатого включения логических элементов на дополняющих МДП транзисторах Ctj.ю

Недостатками этого элемента являются быстродействие и искажение логаческих уровней при большом числе логических элементов со ступенчатым включением.,5

Известен многофункциональный коньюнктивно-инверсный логический элемент, содержащий многовходовые элементы, вьгаолняющие i произвольные заданные логические функции, первый из которых вклю- га чен между шиной. питания и общей шиной, а каждый последующий одним вьшодом. подключен к шнне питания, а другим - к выходу предыдущего многовходового логического элемента, и управляемые элементы восстановления уровня напряжения логической единицы, у которых один вывод подключен к шине питания, второйк выходу соответствующего многовходового логического элемента, нач1гааи со второго, а вывод управления через инвертор - к выходу предыдущего многовходового логического элемй1та 2),

Недостатком устройства является низкое быстродействие из-за перезаряда выходных Оулкостей через большое число последовательно включенных -МДП транзисторов п -типа между выходом каждого многовходового логического элемента и общей шиной.

Целью изобретения является повыщение быстродействия.

Для достижения поставленной цели в многофункциональный логический элемент, содержащий многовходовые логические элементы, выполняющие произвольные заданные, логические функции, пфвый из которых включен между шиной

питания и обшей шиной, а кожльгЯ nocjtonyiomjtu одним выводом подключен к шине питания, и управляемые элемйггы восставовления уровня напряйсения логияеской единицы, у которых

один вывод подключен к шине питания, а второй - к выходу соответствующего многовходового логического элемента, начиная со второго, введены разделительные инверторы, у каждого из которых

выход подключен ко второму выводу COOT

ветствующего многовходового логического элемента, начиная со второго, а вход к выходу предыдущего многовходового логического элемента и к выводу управления элемента восстановления уровня напряже1шя логической еди.ницы последующего многовходового логического Улемента.

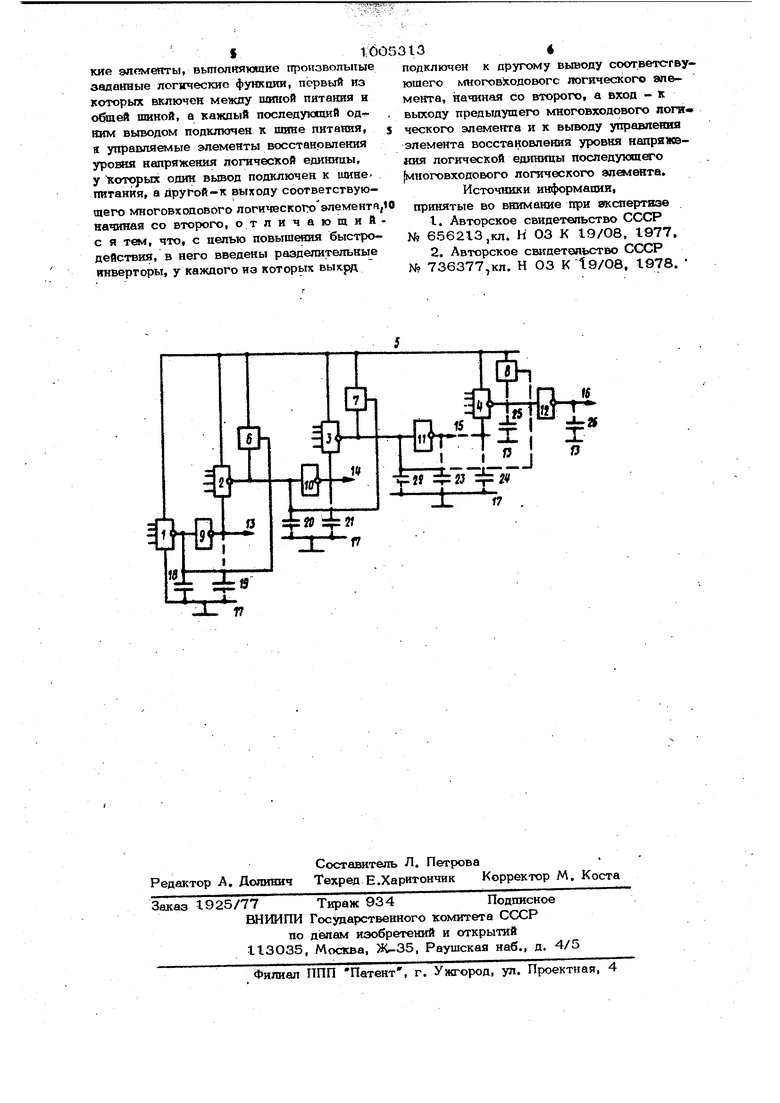

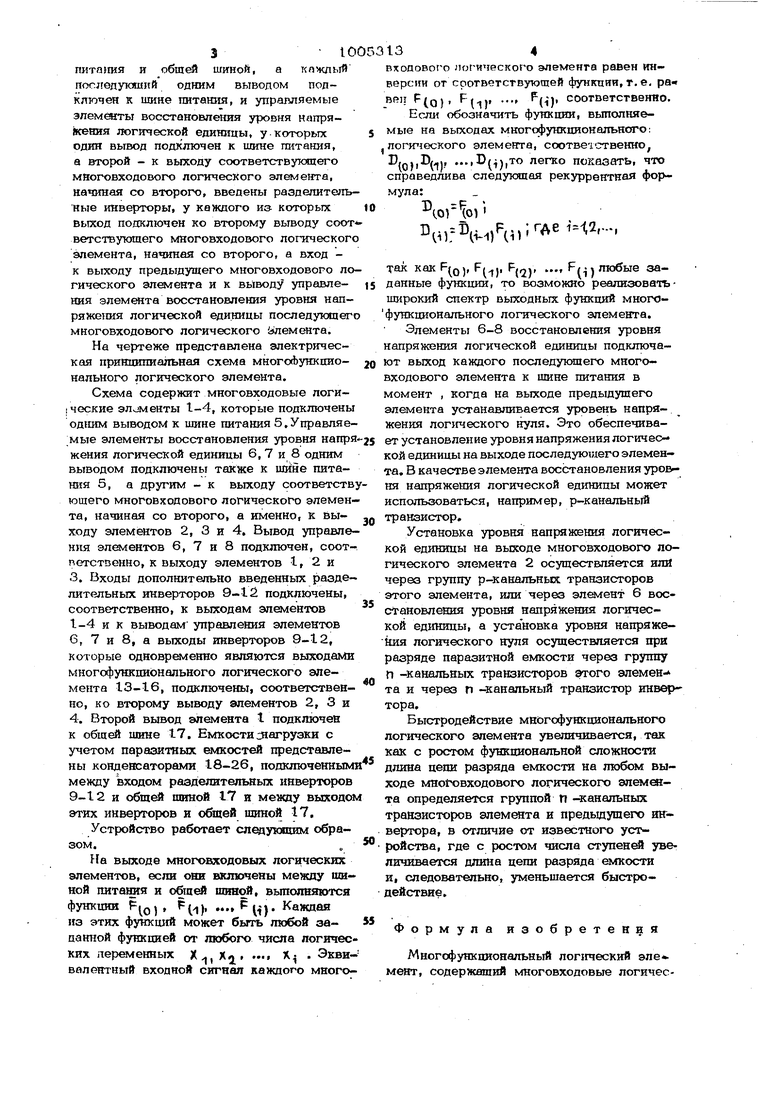

На чертеже представлена электрическая приншгаиальная схема многоАункпионального логического элемента.

Схема содержит многовходовые логи1ческие элементы 1-4, которые подключены ОД1ШМ выводом к шине питания 5.Управляемые элементы восстановления уровня напря жения логической единицы 6, 7 и 8 одним выводом подключены также к шине питания 5, а другим - к выходу соответствющего многовходового логического элемента, начиная со второго, а именно, к выходу элементов 2, 3 и 4, Вывод управления элетлентов 6, 7 н 8 подключен, соответственно, к выходу элементов I, 2 и

3.Входы дополнительно введенных разде лительных инверторов 9-12 подключены, соответственно, к выходам элементов 1-4 и к выводам управления элементов

6, 7 и 8, а выходы инверторов 9-12, которые одновретленно являются выходами многофункциональаого логического элемента 13-16, подключены, соответственно, ко второму выводу элементов 2, 3 и

4.Второй вывод элемента I подключен к общей шине 17. Емкости з агруаки с учетом паразитных емкостей представлены конденсаторами 18-26, подключенными между входом разделительных инверторов 9-12 и общей шиной 17 и между выходом этих инверторов и общей шиной 17,

Устройство работает следующим образом.„

На выходе многовходовых логических элементов, если они включены между шиной пнташия и общей пшной, вьтолшпотся функшш ), (/1), .... . Каждая из этих функций может быть любой запанной функцией от любого числа логических переменных Х, квивалентный входной сигнал кажаого многовходового логического элемента равен инверсии от соответствующей функаяи, г, е. ра ВВП F(Q), F(-) (i) соответственно.

ЕСЛИ обозначить функшш, выполняемые на выходах многофункционального: логи еского элемента, соответственно,

(0)(1) (i) легко показать, что спроведтшва следующая рекуррентная формула:

orlo) °OrVi) (iP так как f(Q, , Fj)- .t F) любые заданные функции, то возможно реализоватьширокий спектр выходных функций много функционального логического элемента.

Элементы 6-8 восстановления уровня напряжения логической единицы подключают выход каждого последукгаего многовходового элемента к шине питания в момент , когда на выходе предыдущего элемента устанавливается уровень напряжения логического нуля. Это обеспечивает установление уровня напряжения логической единицы на выходе последуюихего элемента, В качестве элемента восстановления уро&ня нaпpяжe шя логической единицы может использоваться, например, р-канальньгй транзистор.

Установка уровня напряжения логической единицы на выходе многовходового логического элемента 2 осуществляется или через группу р-к анальных транзисторов этого элемента, или через элемент 6 восстановления уровня напряжения логической единицы, а установка уровня напряжения логического нуля осуществляется при разряде паразитной емкости через группу П -канальных транзисторов этого элемен- та и через п -канальный транзистор инвертора.

Быстродействие многофункционального логического элемента увеличивается, так как с ростом функциональной сложности длина цепи разряда емкости на любом выходе мно1х входового логического элемента определяется группой п -канальных транзисторов элемента и предьщушего ин вертора, в отличие от известного устройства, где с ростом числа ступеней увеличивается длина цепи разряда емкости и, следовательно, уменьшается быстродействие.

Формула изобретения

Многофункциональный логический эле, мент, содержащий многовходовые логичесi1:0кие эпемеяты, вьшолняющие произвольные заданные логические функции, первый из которых включен между шиной питания и обшей шиной, а кажпый последующий выводом подключен к шине питания, я управляемые элементы восстановления уровня напряжения логической единицы, у которых один вывод подключен к шине питания, а другой-к выходу соответствующего многовходового логического элементн начиная со второго, отличаюший с я тем, что, с цепью повышения быстродействия, в него введены разделительные инверторы, у каждого на которьге выхрд 13« подключен к другому выводу соответствуюшего moгoвxoдoвoгc логического элемента, начиная со второго, а вход - к выходу предыдушего многовходового логи ческого элемента и к выводу управления элемента восстановления уровня напрямения логической ешпотаы последующего Многовходового логического элемента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 656213 ,кл. Н ОЗ К 19/08, 1977. 2.Авторское свидетельство СССР N9 736377,кл. Н 03 К t9/O8, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный коньюктивно- инверсный логический элемент | 1978 |

|

SU736377A1 |

| Логический элемент | 1977 |

|

SU627594A1 |

| Логический элемент | 1977 |

|

SU680173A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Сумматор | 1983 |

|

SU1101816A1 |

| ЛОГИЧЕСКОЕ (МНОГОФУНКЦИОНАЛЬНОЕ) УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2081509C1 |

| Логический элемент | 1977 |

|

SU627593A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

13

17

Авторы

Даты

1983-03-15—Публикация

1981-08-10—Подача