1 111. 11 jf i

70

00

о

4н

L.

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обра.ботки информации для реализации функций суммы и переноса трех двузначных слагаемйх.

Известен сумматор, содержащий зле менты И-ИЛИ-НЕ, И-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, четыре повторителя и два элемента ИЛИ-НЕ, входы первого элемента ИЛИ-НЕ и элемента И-НЕ подключены, соответственно, к первой и второй входным IjHHaM устройства, выход первого элемента ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и к первому входу элемента И-ИЛИ-ЧЕ, ВЫХОД которого через первый повторитель с инверсным входом подключен к выходу перенос устройства, а второй, третий к четвертый входы соответственно - к первой, второй и третьей входным шинам выход элемента И-НЕ через второй повторитель с инверсным входом подключен к второму входу второго элемента ИЛИ-НЕ, выход которого подключен к первому входу элемента ИСКЛЮЧАЮМЕЕ ИЛИ, второй вход которого подключен через инвертор и третий повторитель с инверсным входом к третьей входной шине, а выход через четвертый повторитель с инверсным входом - к выходу сумма устройства 1.

Недостатком известного устройства является его сложность, а также низкое быстродействие из-за большого числа последовательно включенных элементов.

Целью изобретения является упрот щение и повышение быстродействия устройства.

Для достижения поставленной цели :э сумматоре на МДП-транзисторах, содержащем элемент ИЛИ-НЕ, первый, второй и третий входы которого подключены к соответствующим входным шинам устройства, два повторителя, инвертор и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-НЕ, выход элемента ИЛИ-НЕ подключен к входам первого и второго повторителей, выход первого повторителя подключен к входу инвертора, а выход второго - к второму входу элемента И-ИЛИ-НЕ, третий вход которого подключен к выходу инвертора, являющегося,выходом перенос устройства, выход элемента И-ИЛИ-НЕ является выходом сумма устройства.

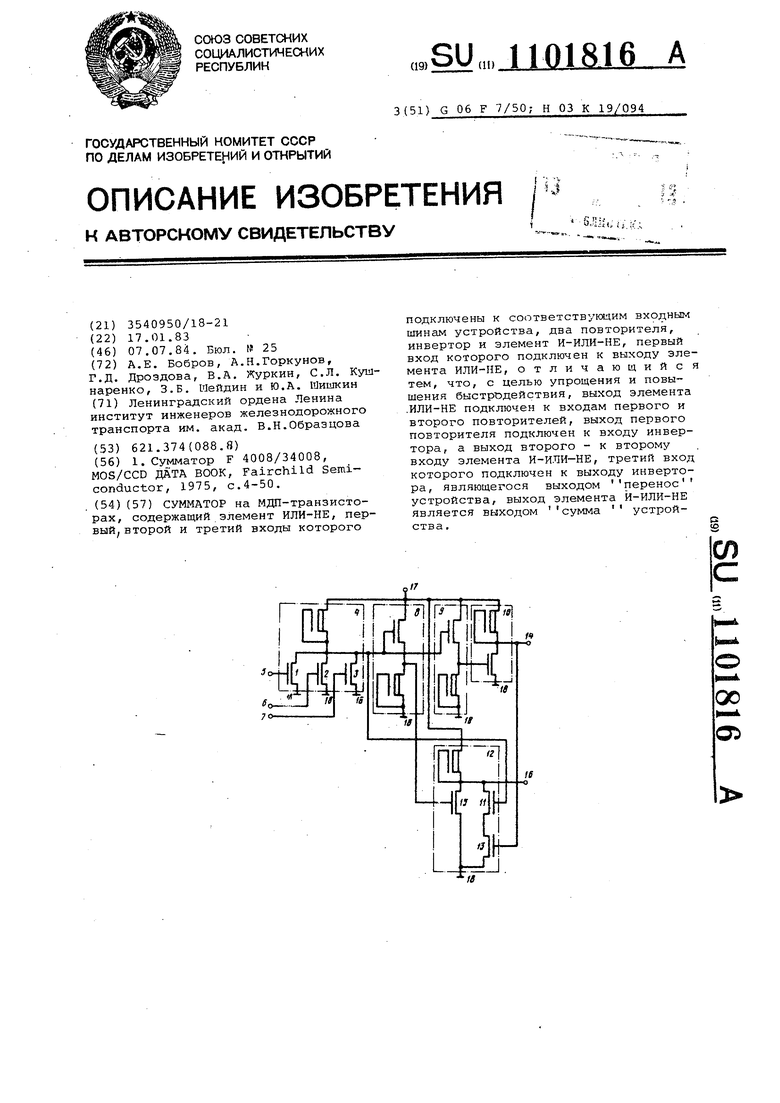

На чертеже представлена электрическая принципиальная схема сугиматора на М Щ-транзисторах.

Затворы ключевых МДП-транзисторов 1-3, элемента ИЛИ-НЕ 4 с многозначным выходом подключены соответственно к первой 5, второй 6-и третьей 7 входным шинам устройства, выход элемента ИЛИ-НЕ 4 подключен последова-. тельно к выходам первого 8 и второго 9 повторителей (выход второго повторителя 9 подключен к входу инвертора 10) и к затвору ключевого МДПтранзистора 11 (первый вход элемента И-ИЛИ-НЕ 12). Последовательно с ключевым МДП-транзистором 11 вклкрчен МДП-транзистор 13, затвор которого Является вторым входом элемента И-ИЛИ-НЕ 12 и подключен к выходу инвертора 10, выход которого является одновременно выходом 14 перенос устройства.

Параллельно МДП-транзисторам 11 и 13 включен ключевой МДП-транзистор 15, затвор которого, являющийся третьим входом элемента И-ИЛИ-НЕ 12, подключен к выходу повторителя 8 . Выход элемента И-ИЛИ-НЕ 12 является выходом 16 сумма устройства. Выводи питания всех элементов устройства подключены соответственно к к шине 17 питания и к общей шине 18.

Устройство работает следующим образом.

В зависимости от числа открытых ключевых МДП-транзисторов 1-3 элемента 4 (если устройство выполнено на п-канальных транзисторах, то в зависимости от числа единиц на вход-ных шинах 5-7) напряжение на выходе элемента 4 принимает одно из четырех значений (значность структурного алфавита равнй четырем). Размеры МДПтранзисторов 1-3 оди;;аковы и выбраны так, что если число единиц на входе N 0,1,2,3 , то напряжение на .

2 Ul

ходе принимает значения

По и, U2 П ;

и.-, , При этом

о УПОР

з, где - пороговое

напряжение МДП-транзистора с индуцированным каналом; Е - напряжение питания .

Соотношение г 1ежду размерами нагрузочных и ключевых .транзисторов повторителей 8 и 9 выбрано так, что напряжение на выходе повторителя 8

с/ Uo, Uo,

принимает значения iЦ

а на выходе повторителя У U

Uj , Ug, где U - напряжение, величина которого больше, чем .

При этом на выходе инвертора 10 и соответственно на выходе 14 устройства реализуется функция переноса Uo, и о, П J, U.j в соответствии с количеством единиц на входе N 0,1,2,3: . Уровень UQ соответствует уровню напряжения логического нуля, а уровень Uj - уровню напряжения логической единицы.

Размеры нагрузочного и ключевых МДП-транзисторов элемента И-ИЛИ-НЕ 12 выбраны таким образом, что когда открыт МДП-транзистор 15 или МДПтранзисторы 11 и 13, напряжение на выходе 16 равно и,. При этом на выходе 16 реализуется функция сум, 3 И01816

мы ;.Uo , Uj , UQ , Uj в соответствииет задержку формирования переноса

с количеством единиц на входепри построении многоразрядных 0,1,2,3 .маторов на 2т, где С-среднее время

Для уменьшения потребляемой мощ-перезаряда нагрузочной емкости чености и расширения диапазона преде-рез МДП-транзистор, при этом колитавления многозначного сигнала нагру- 5 -чесуво МДП-транзисторов в ка5кдом

зочные транзисторы элементов устрой-разряде устройства уменьшается на

ства являются МДП-транзисторами со ,пять.

встроенным каналом, а ключевые тран-Таким образом, технико-экономичесзисторы - МДП-транзисторами с ин-кий эффект изобретения заключается в

дуцированным каналом. Сумматор имеет10 упрощении и повышении быстродействия

один выход перенос,что сокраща-;устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор | 1983 |

|

SU1101863A1 |

| Мультивибратор | 1978 |

|

SU738107A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Аналоговое множительное устройство | 1979 |

|

SU932506A1 |

| Одноразрядный двоичный сумматор | 1980 |

|

SU943712A1 |

| Одноразрядный сумматор | 1983 |

|

SU1117634A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

СУММАТОР на МДП-транзисторах, содержащий элемент ИЛИ-НЕ, первый, второй и третий входы которого подключены к соответствукядим входным шинам устройства, два повторителя, инвертор и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-НЕ, отличающийс я тем, что, с целью упрощения и повышения быстродействия, выход элемента .ИЛИ-НЕ подключен к входам первого и второго повторителей, выход первого повторителя подключен к входу инвертора, а выход второго - к второму входу элемента И-ИЛИ-НЕ, третий вход которого подключен к выходу инвертора, являющегося выходом перенос устройства, выход элемента Й-ИЛИ-НЕ является выходом сумма устройо to ства ,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дальномер-построитель | 1925 |

|

SU4008A1 |

Авторы

Даты

1984-07-07—Публикация

1983-01-17—Подача