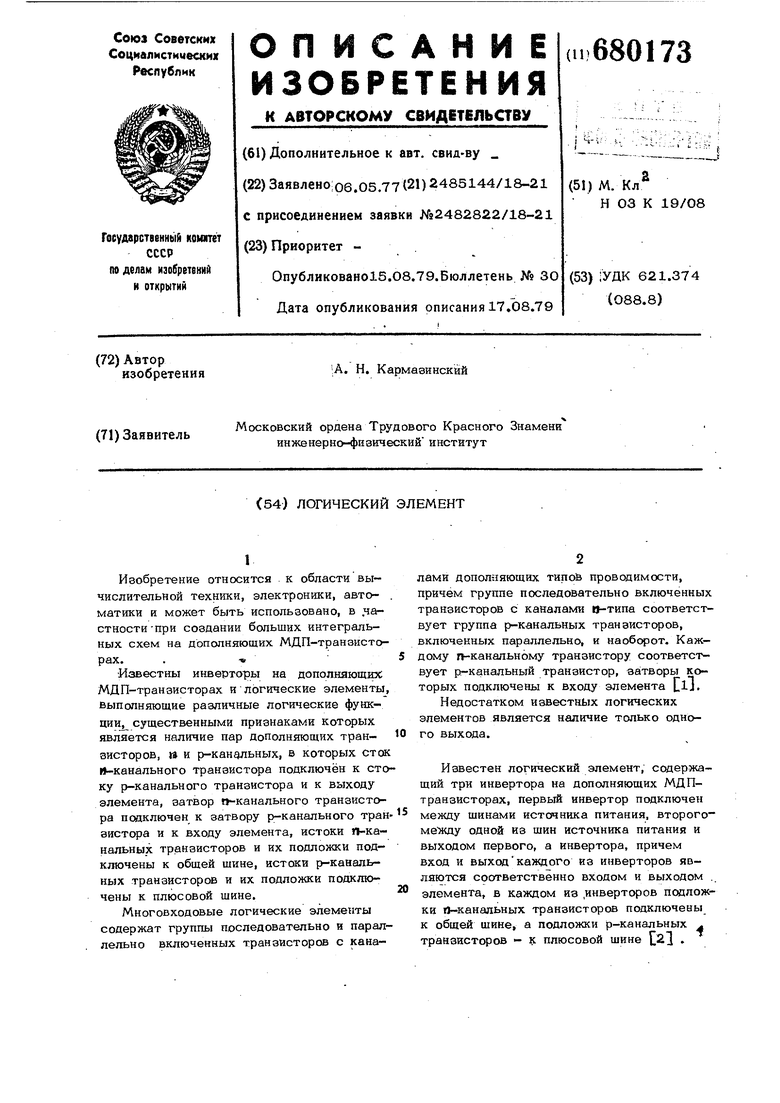

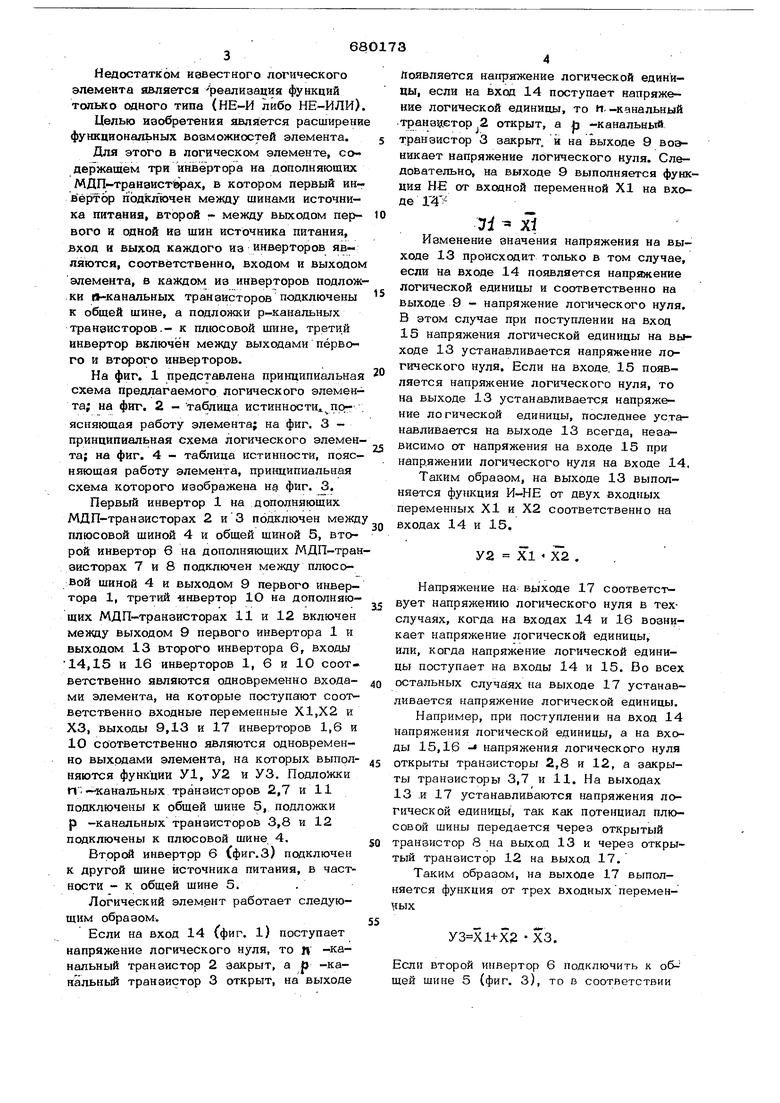

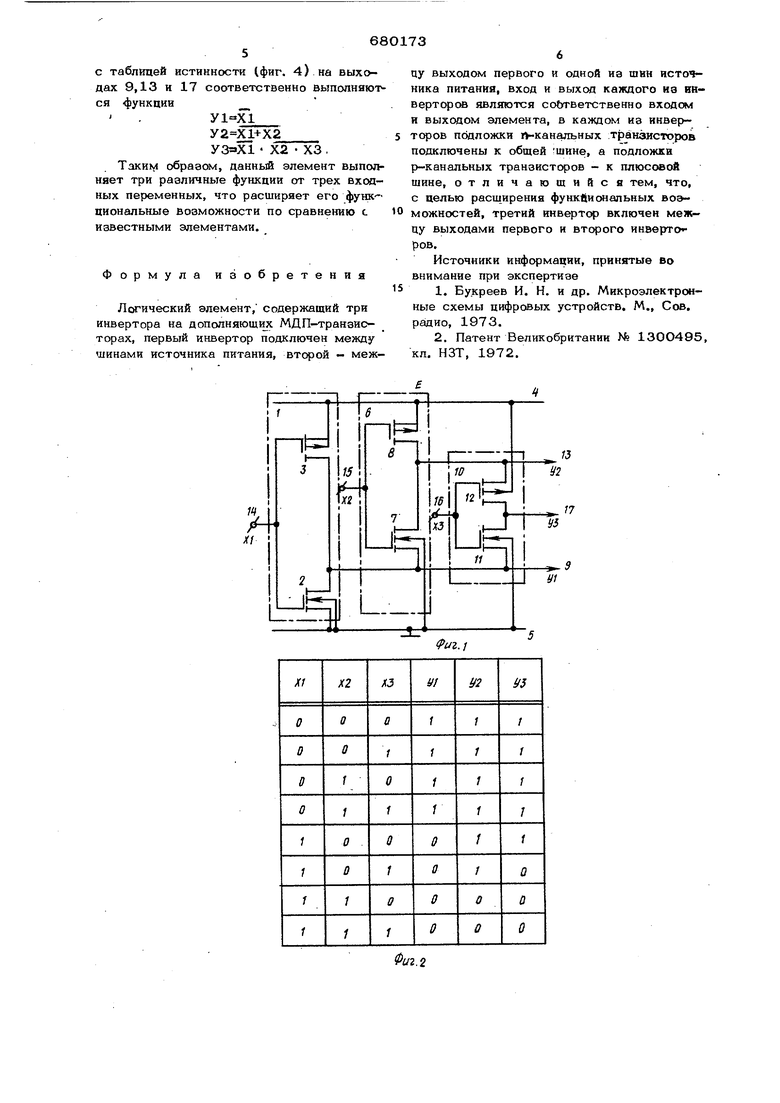

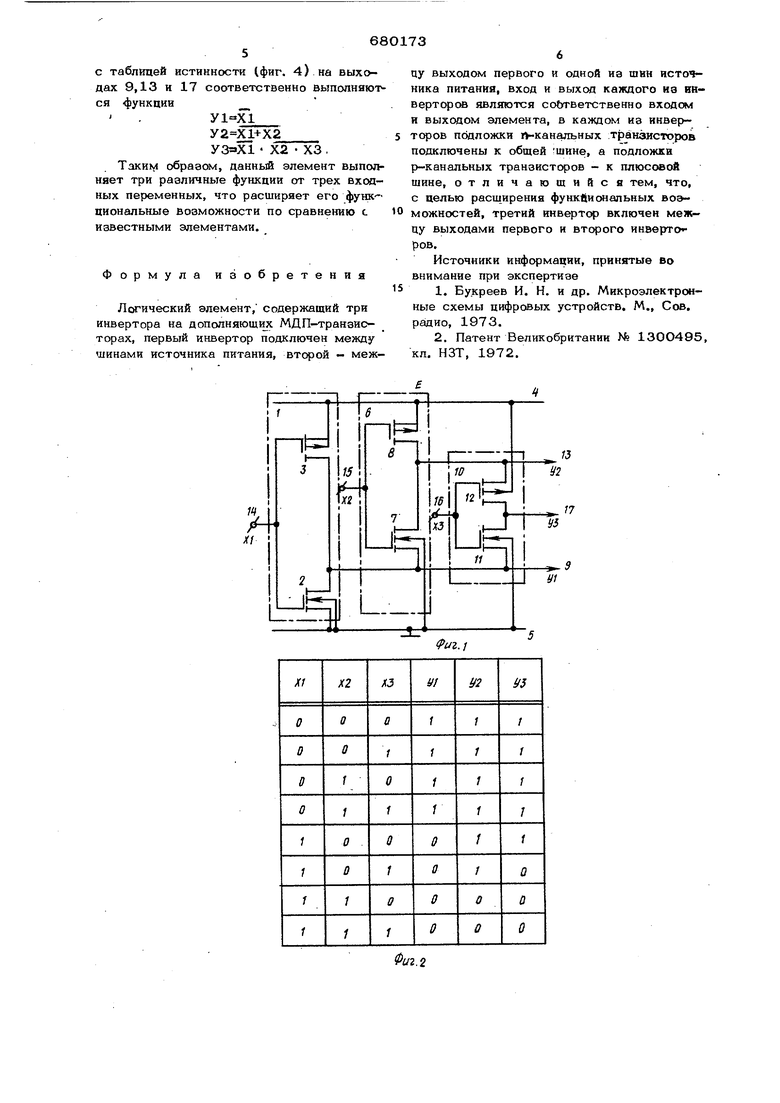

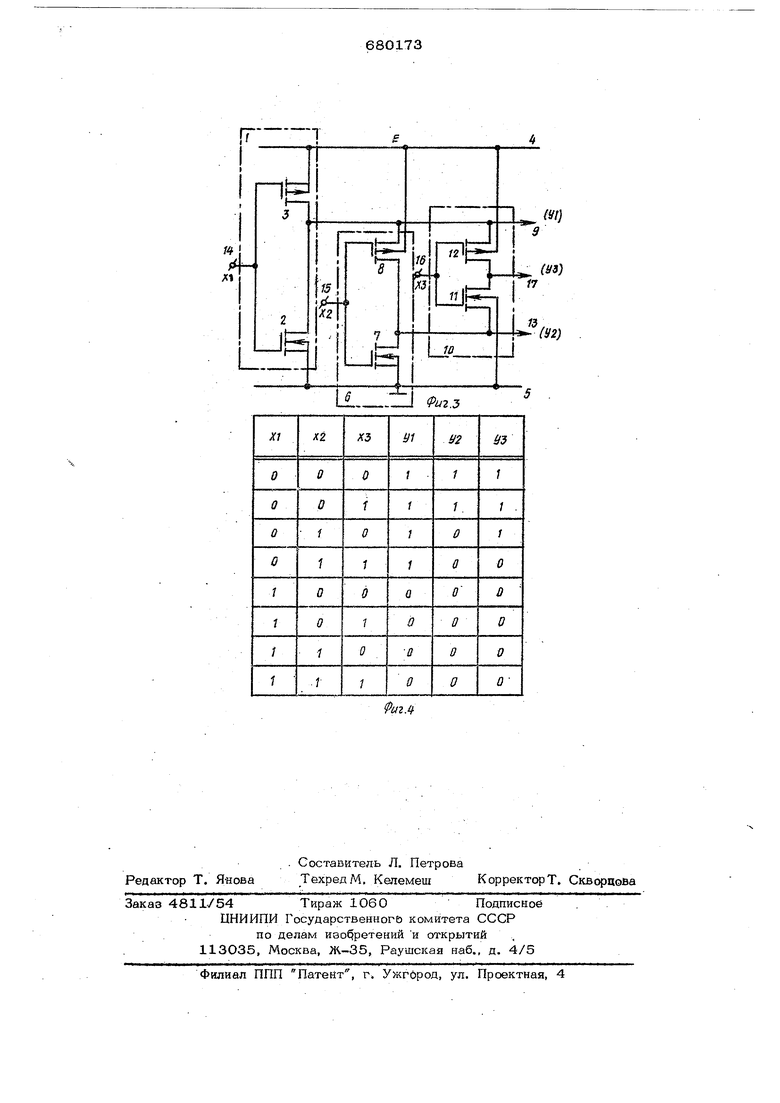

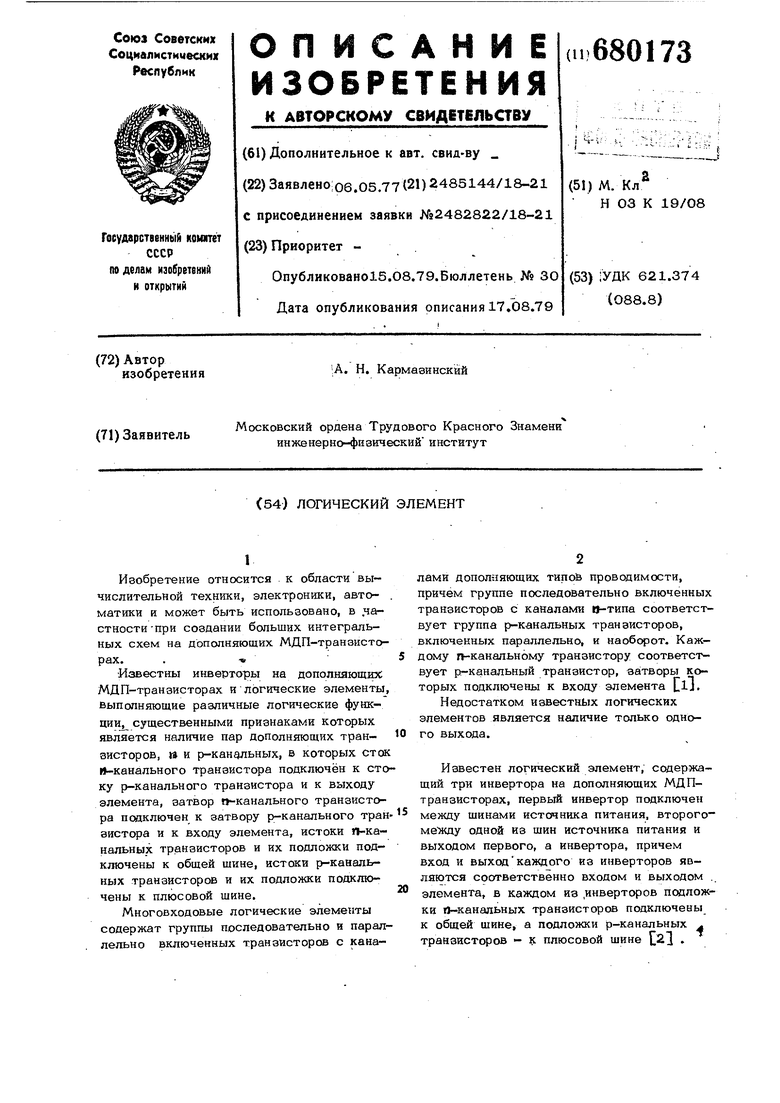

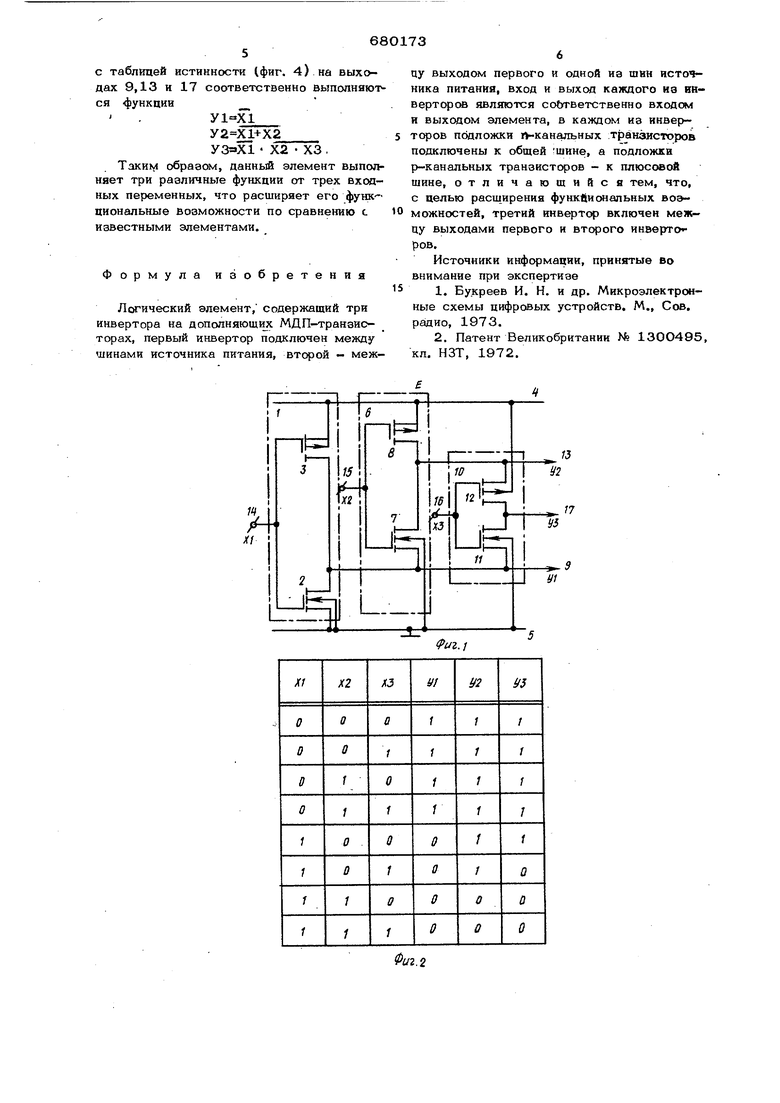

Изобретение относится к области вычислительной техники, электроники, автоматики и может быть использовано, в .частности-при создании больших интегральных схем на дополняющих МДП-транзисторах..- Известны инверторы на дополняющ1Е С МДП-транзисторах и логические элементы выполняющие различные логические функции, существенными признаками которых является наличие пар дополняющих транзисторов, 14 и р-канальных, в которых сток И-канального транзистора подключён к сто ку р-канального транзистора и к выходу элемента, затвор -канального транзистора подключен к затвору р-канального траН вистора и к входу элемента, истоки il-канальных транзисторов и их подложки подключены к общей шине, истоки р-канальных транзисторов и их подложки подключены к плюсовой шине. Многовходовые логические элементы содержат группы последовательно и парал лельно включенных транзисторов с каналами дополняющих типоЬ проводимости, причем группе последовательно включенных транзисторов с каналами о-типа соответствует группа р-канальных транзисторов, включенных параллельно, и наоборот. Каждому п-канальному транзистору соответствует р-канальный транзистор, затворы которых подключены к входу элемента .i, Недостатком известных логических элементов является наличие только одного выхода. Известен логический элемент, содержащий трк инвертора на дополняющих МДПтранзисторах, первый инвертор подключен между щинами источника питания, второгомежду одной из щин источника питания и выходом первого, а инвертора, причем вход и выходкаждого из инверторов являются соответственно входом и выходом . элемента, в каждом из инверторов подложки п-канальных транзисторов подключены к общей шине, а подложки р-канальных . транзисторов - к плюсовой щине . Недостатком иввестного логического элемента является реализация функций только одного типа (НЕ-И либо НЕ-ИЛИ) Целью изобретения является расширени функциональных возможностей элемента. Для этого в логическом элементе, содержащем три инвёртора на дополняющих МДП-транаист ах, в котором первый инвёртор подключен между шинами источника питания, второй - между выходом первого и одной ив шин источника питания, вход и выход каждого из инверторов являются, соответственно, входом и выходом элемента, в каждом ив инверторов подлож ки инканальных транзисторов подключены к общей шине, а подложки р-канальных транзисторов.- к плюсовой шине, трети.й инвертор включён между выходами первого и второго инверторов. На фиг. 1 представлена принципиальная схема предлагаемого логического элемента; на фиг. 2 - таблица истинности поясняющая работу элемента; на фиг. 3 принципиальная схема логического элемен та; на фиг. 4 - таблица истинности, поясняющая работу элемента, принципиальная схема которого изображена Hg фиг. 3. Первый инвертор 1 на дополняющих МДП-транзисторах 2 иЗ подключен межд плюсовой шиной 4 и общей шиной 5, второй инвертор 6 на дополняющих МДП-тран зисторах 7 и 8 подключен между плюсовой щиной 4 и выходом 9 первого инвертора 1, третий «нвертор 1О на дополняющих МДП-транзксторах 11 и 12 включен между выходом 9 первого инвертора 1 и выходом 13 второго инвертора 6, входы 14,15 и 16 инверторов 1, 6 и 1О соот« ветственно являются одновременно входами элемента, на которые поступают соответственно входные переменные Х1,Х2 и ХЗ, выходы 9,13 и 17 инверторов 1,6 и 10 соответственно являются одновременно выходами элемента, на которых выполняются функции У1, У2 и УЗ. Подложки П -нканальных транзисторов 2,7 и 11 подключены к общей шине 5, подложки р -канальных транзисторов 3,8 и 12 подключены к плюсовой шине 4. Второй инвертор 6 (фиг.З) подключен к другой шине источника питания, в частности - к общей шине 5. Логический элемент работает следующим образом, Если на вход 14 (фиг. 1) поступает напряжение логического нуля, то к -канальный транзистор 2 закрыт, а р -канальный транзистор 3 открыт, на выходе йоявляется наггряжение логической единицы, если на вход 14 поступает напряжение логической единицы, то Н--канальный транзистор 2 открыт, а и -канальньтй транзистор 3 закрыт, и на выходе 9 возникает напряжение логического нуля. Следовательно, на выходе 9 выполняется функция НЕ от входной переменной XI на входе 14 l/i-Xl Изменение значения напряжения на выходе 13 происходит только в том случае, если на входе 14 появляется напряжение логической единицы и соответственно на выходе 9 - напряжение логического нуля, В этом случае при поступлении на вход 15 напряжения логической единицы на выходе 13 устанавливается напряжение логического нуля. Если на входе. 15 появляется напряжение логического нуля, то на выходе 13 устанавливается напряжение ло гической единицы, последнее устанавливается на выходе 13 всегда, независимо от напряжения на входе 15 при напряжении логического нуля на входе 14, Таккм образом, на выходе 13 выполняется функция И-НЕ от двух входных переменных XI и Х2 соответственно на входах 14 и 15. У2 Х Х2 . Напряжение на- выходе 17 соответствует напряжению логического нуля в техслучаях, когда на входах 14 и 16 возникает напряжение логической единицы, или, когда напряжение логической единицы поступает на входы 14 и 15. Во всех остальных случаях на выходе 17 устанавливается напряжение логической единицы. Например, при поступлении на вход 14 напряжения логической единицы, а на вхоы 15,16 - напряжения логического нуля открыты транзисторы 2,8 и 12, а закрыы транзисторы 3,7 и 11. На выходах 13 .и 17 устанавливаются напряжения лоической единицы, так как потенциал плюовой шины передается через открытый ранзистор 8 на выход 13 и через открыый транзистор 12 на выход 17, Таким образом, на выходе 17 выполяется функция от трех входныхпеременУЗ Х1+Х2 ХЗ. сли второй инвертор 6 подключить к обей шине 5 (фиг. З), то в соответствии с таблицей истиннсх:ти (фиг. 4) на выходах 9,13 и 17 соответственно выполняют ея функции У1°Х1 У Х1+Х2 Х2 ХЗ . . Таким обравом, данный элемент выполняет три различные функции от трех входных переменных, что расщиряет его функциональные возможности по сравнению с известными элементами. Формула изобретения Логический элемент, содержащий три инвертора на дополняющих МДП-транаиоторах, первый инвертор подключен между шинами источника питания, второй - межГ

iH

цу выходом первого и одной иа швн источкика питания, вход и выход каждого иа инверторсж явл5потся соЬтветственно входом и выходом элемента, в каждом из инверторов подложки п-канальных т|эанаисторов подключены к общей ;шине, а подложки р-канальных транзисторов - к плюсовой шине, отличающийся тем, что, с целью расширения функйиовальных воэможностей, третий инвертер) включен межцу выходами первого и второго инверторов, Источники информации, принятые во внимание при экспертизе 1. Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., Сов, радио, 1973. 2. Патент Великобритании № 130О495, кл. НЗТ, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1977 |

|

SU627593A1 |

| Логический элемент | 1977 |

|

SU627594A1 |

| Логический элемент или-не | 1977 |

|

SU656214A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Согласующее устройство на мдптранзисторах | 1976 |

|

SU708512A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Логический элемент и-не | 1977 |

|

SU656213A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

XI

Г7

F

т

Авторы

Даты

1979-08-15—Публикация

1977-05-06—Подача