Изобретение относится к автоматике и вычислительной технике, в частное- , ти к устройствам формирования тестов, и может .быть использовано для контроля функционирования средств вычислительной техники.

Цель изобретения - повьшение функциональной надежности устройства за счет снижения вероятности ложной выдачи сообщения на объекто

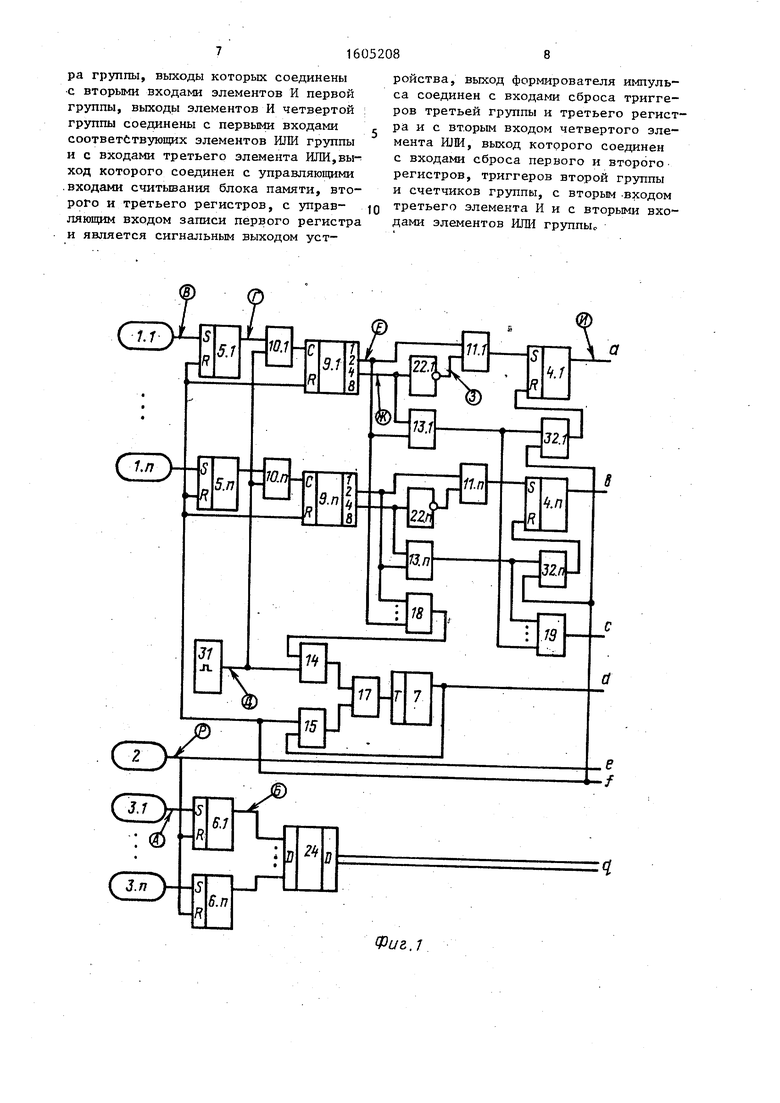

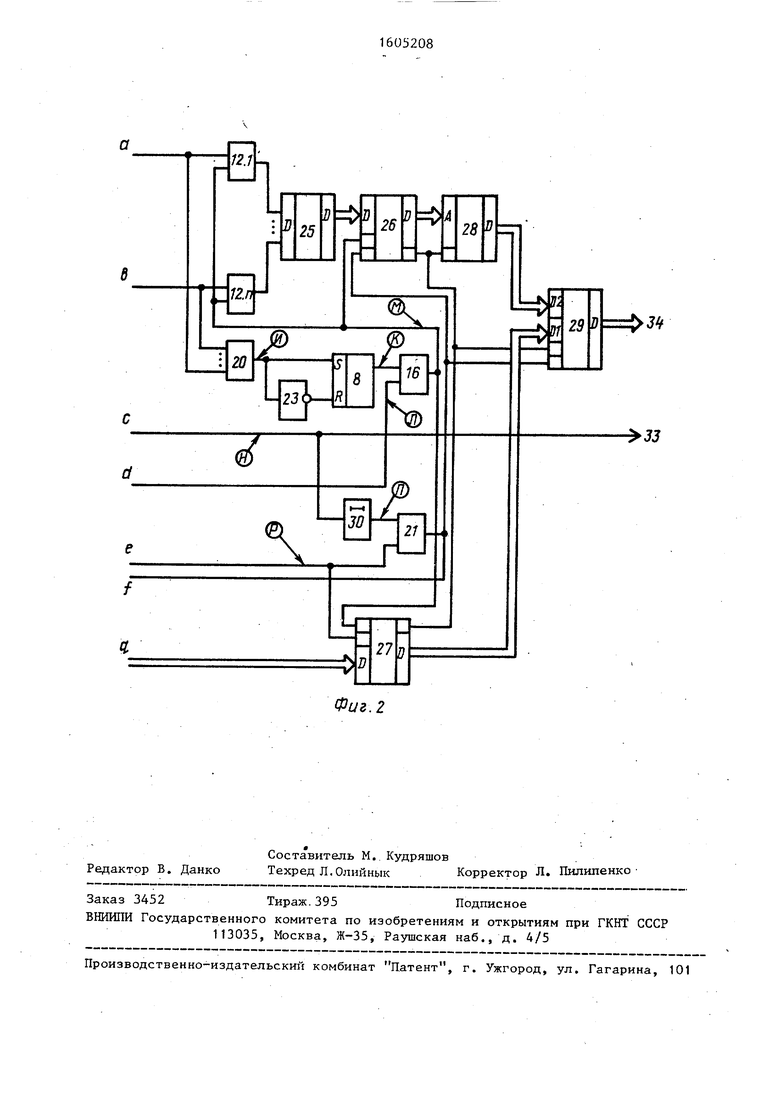

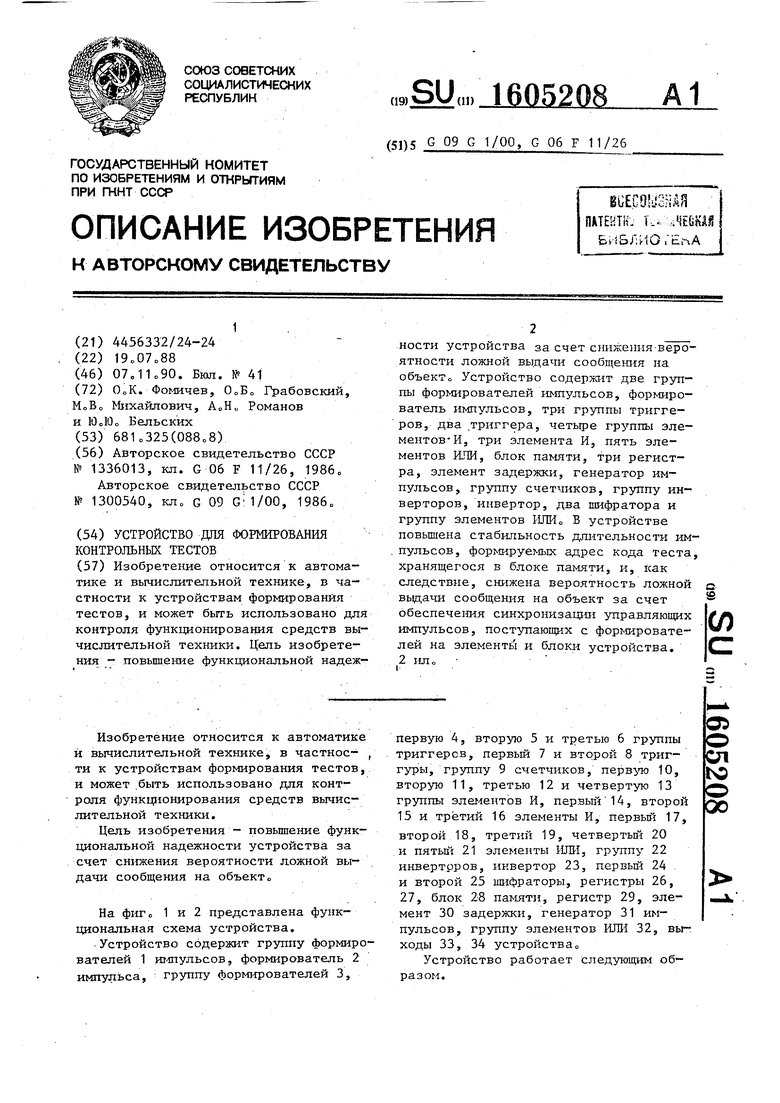

На фиг о 1 и 2 представлена функциональная схема устройства.

Устройство содержит грзшпу формирователей 1 ш-шульсов, формирователь 2 импульса, группу формирователей 3,

первую 4, вторую 5 и третью 6 группы триггеров, первый 7 и второй 8 триг- гуры, группу 9 счетчиков, 10, вторую 11, третью 12 и четвертую 13 группы элементов И, первый 14, второй 15 и третий 16 элементы И, первьп 17, второй 18, третий 19, четвертьй 20 и пятьпЧ 21 элементы ИЛИ, группу 22 инвертрров, инвертор 23, первый 24 и второй 25 шифраторы, регистры 26, 27, блок 28 памяти, регистр 29, элемент 30 задержки, генератор 31 импульсов, группу элементов ИЛИ 32, выходы 33, 34 устройства

Устройство работает следующим образом.

05

О

СП

ю

о

00

После включения устройства оно устанавливается в исходное состояние формирователем 2, который устанавливает в нулевое состояние триггеры 6 обнуляет регистр 27, через элемент ИЛИ 21 обнуляет регистры 26 и 29, триггеры 5, счетчики 9 группы и через элементы ИЛИ 32 - триггеры 4„

В исходном состоянии на прямом вы ходе триггера 7 устанавливается низкий потенциал (логический О).Если по каким-либо причинам после включения устройства на выходе триггера 7 будет высокий потенциал (логическая 1), то импульс Сброс, пройдя через открытьш элемент И 15 и элемент ИЛИ 17, поступит на счетный вход тригера 7 и установит его в исходное сос тояниео.

Весь цикл формирования устройство тестового сообщения можно условно раделить на два этапа: первьш - форми- |рование кода адреса теста, записанно го в блоке 28 памяти, и кода адреса контролируемого объекта; второй - выборка из блока 28 памяти кода теста, запись в регистр 29 кода теста |И кода адреса объекта, вьщача тесто- I вого.сообщения.

Устройство может работать в двух режимах: первьй - тестирование одного объекта; второй - тестирование объектов в любой последовательности. В первом режиме оператор нажимает клавишу соответствующего формирователя 3, а затем в необходимой последовательности клавиши формирователей 1 о Второй режим аналогичен первог, тол

ко при переходе к работе с новым объектом необходимо осуществлять сброс триггеров 6 группы нажатием клавиши формирователя 2.

В процессе работы, при необходимости вьщачи на объект тестового сообщения, оператор нажимает клавишу соответствующего формирователя 3 и клавишу соответствующего формирователя 1.Импульс с выхода соответствующег формирователя 3 поступает на устано- вочньш --вход соответствующего триггера 6, устанавливая его в состояние, при котором на его прямом выходе появится высокий потенциал. Шифратор преобразует код, поступаюшлй на его входы с выходов триггеров 6, в код адреса контролируемого объекта, который поступает на информационные вход регистра 27.

15

..,.,

5

0

5

0

5

0

5

Импульс с выхода соответствующего формирователя 1 поступает на устано- вочньп вход триггера 5, устанавливая его в состояние, при котором на его прямом выходе появится высокий потенциал, которым открывается соответствующий элемент И 10.

Тактовые импульсы с выхода генератора 31 импульсов поступают через соответствующий элемент И 10 на счетный вход соответствующего счетчика 9. В момент поступления второго тактового импульса на счетный вход счетчика 9 на его выходе 2 появится импульс, I который через элемент И 11.1 поступает :на установочный вход триггера 4.1, устанавливая его в единичное состояние. Элемент И 11.1 открыт высоким потенциалом, поступающим на него с выхода инвертора 22.1, на вход которого подается низкий потенциал с выхода 4 счетчика 9., 1.

Импульс с выхода триггера 4.1 через элемент ИШ 20 устанавливает в единичное состояние триггер 8, который открывает по одному входу элемент И 16, на другой вход которого поступают импульсы с выхода триггера 7.

Первый импульс с выхода триггера 7, провдя элемент И 16, поступает на входы элементов И 12, но проходит только через открытый элемент И 12„I и поступает на первый вход шифратора 25, на остальных входах шифратора 25 логические О. На выходах шифратора 25 формируется код адреса теста, записанного в блоке 28 памяти. Кроме того, по импульсу с выхода элемента И 16 осуществляется запись кода адреса теста и кода адреса контролируемого объекта с выхода шифраторов 25 и 24 в соответ- ствуюир е регистры 26 и 27.

При поступлении четвертого тактового импульса на счетный вход счетчика 9.1 с генератора 31 на выходе 4 счетчика 9.1 формируется импульс, по которому закрьшается элемент И 11.1 и открывается по одному входу элемент И 13.1.

С поступлением шестого тактового импульса на счетньй вход счетчика 9.1 на его выходе 2 появляется второй импульс, которым сбрасывается через элемент И 13.1 и элемент ИЛИ 32.1 триггер 4.1 и триггер 8, запускается через элемент ИЛИ 19 элемент 30 задержки, осуществляется считывание из . 28 памяти кода теста по соответствующему адресу и запись в регист 29 кода теста и кода адреса контролируемого объекта.

Код тестовос о сообщения с информа 1ЩОННЫХ выходов выходного регистра 29 по информационной шине поступает на выход 34 устройства. С выхода 34 тестовое сообщение поступает в кана- лообразующее устройство, прием сообщения синхронизируется импульсом, поступающим с выхода 33 устройства.

Следует отметить, что информационные выходы регистра 29 не блокируютс при записи в него информации, а следовательно, уже при записи сообщения в регистр 29 на его выходах будет присутствовать информация.

После окончания процесса перезаписи кодов в регистр 29 и выдачи сообщения импульс с выхода элемента 30 задержки проходит через элемент ИЛИ 21 и устанавливает соответствующие элементы устройства в исходное состояние. Устройство готовь к вьщаче нового тестового сообщения, но по адресу объекта, который был набран.

Формула изобретения

Устройство для формирования контрольных тестов, содержащее первую и вторую группы формирователей импульсов, формирователь импульсов, первую группу триггеров, два триггера, три группы элементов И, первый элемент И, пять элементов ИЛИ, блок памяти, первый регистр, элемент задержки и генератор импульсов, выход которого соединен с первым входом первого элемента И, выход первого элемента ИЛИ соединен со счетным входом первого триггера, выходы элементов И первой группы соединены с единичными входами

соединен с входом сброса второго три гера, прямой выход которого соединен первым входом второго элемента И, вы ход которого соединен с управляющими входами записи второго н третьего ре гистров и с вторыми вxoдa 0i элементо И второй группы, выходы которых соединены с входами первого шифратора, выходы которого соединены с информац онными входами второго регистра, информационные выходы которого соедине- .ны с адресными входами блока памяти, выходы формирователей импульсов первой и второй групп соединены соответ- 30 ственно с единичными входами триггеро второй и третьей групп, прямые выходы триггеров третьей грзшпы соединены с входами второго шифратора, выходы которого соединены с информационными вxoдa ш третьего регистра, выходы которого соединены с первой группой информационных входов первого регистра, прямые выходы триггеров второй группы соединены с первыми входами элементов 4Q И третьей группы, выходы которых соединены со счетными входаьш соответствующих счетчиков5 группы, первые инфор махщонные выходы которых соединены с первыми входами элементов И первой

триггеров первой группы, прямые выхо- дз четвертой групп и с входами пятого ды которых соединены с первыми входа- элемента ИЛИ, выход которого соединен ми элементов И второй группы, выход второго элемента ШШ соединен с единичным входом второго триггера, выход

с вторым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с вхо- 50 которого соединен с выходом третьего дом элемента задержки, выход которого элемента И, первый вход которого сое- соединен с первым входом четвертого динен с выходом первого триггера и с элемента ИЛИ,.информационные выходы вторым входом второго элемента И, вы- блока памяти соединены с первой груп- ход генератора импульсов соединен с пои информационных входов первого ре- 55 вторыми входами элементов И третьей гистра, информационные вьгходы которо- группы, вторые информационные выходы то являются информационными выходами устройства, отличающееся

счетчиков группы соединены с вторыми входами соответствующих элементов И четвертой группы и с входами инвертотем, что, с целью повьш1ения функцио20

нальной надежности устройства за счет снижения вероятности ложной выдачи сообщения на объект, в него введены вторая и третья группы триггеров, группа счетчиков, четвертая группа элементов И, второй и третий элементы И, группа инверторов, инвертор, первый и второй шифраторы, второй и Q третий регистры и группа элементов ИЛИ, выходы которых соединены соответственно с -входами сброса триггеров первой группы, прямые выходы которых соединены с входами второго элемента 15 ИЛИ, выход которого через инвертор

соединен с входом сброса второго триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с управляющими входами записи второго н третьего ре- гистров и с вторыми вxoдa 0i элементов И второй группы, выходы которых соединены с входами первого шифратора, выходы которого соединены с информационными входами второго регистра, информационные выходы которого соедине- .ны с адресными входами блока памяти, выходы формирователей импульсов первой и второй групп соединены соответ- 0 ственно с единичными входами триггеров второй и третьей групп, прямые выходы триггеров третьей грзшпы соединены с входами второго шифратора, выходы которого соединены с информационными вxoдa ш третьего регистра, выходы которого соединены с первой группой информационных входов первого регистра, прямые выходы триггеров второй группы соединены с первыми входами элементов Q И третьей группы, выходы которых соединены со счетными входаьш соответствующих счетчиков5 группы, первые инфор- махщонные выходы которых соединены с первыми входами элементов И первой

5

з четвертой групп и с входами пятого элемента ИЛИ, выход которого соединен

с вторым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого сое- динен с выходом первого триггера и с вторым входом второго элемента И, вы- ход генератора импульсов соединен с вторыми входами элементов И третьей группы, вторые информационные выходы

счетчиков группы соединены с вторыми входами соответствующих элементов И четвертой группы и с входами инвертоpa группы, выходы которых соединены с вторыми входами элементов И первой группы, выходы элементов И четвертой группы соединены с первыми входами соответствующих элементов ИЛИ группы и с входами третьего элемента ШШ,вы- ход которого соединен с управляющими .входами считьшания блока памяти, второго и третьего регистров, с управ- ляющим входом записи первого регистра и является сигнальным выходом устройства, выход формирователя ш-туль- са соединен с входами сброса триггеров третьей группы и третьего регистра и с вторым входом четвертого элемента ИЛИ, выход которого соединен с входами сброса первого и второго регистров, триггеров второй группы и счетчиков группы, с вторым -входом третьего элемента И и с вторыми входами элементов ИЛИ группыо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1987 |

|

SU1492360A1 |

| Устройство для передачи информации | 1989 |

|

SU1649586A1 |

| Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления | 1988 |

|

SU1525679A2 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для управления выдачей команд | 1990 |

|

SU1781683A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Программируемый коммутатор | 1985 |

|

SU1287277A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

Изобретение относится к области автоматики и вычислительной технике, в частности к устройствам формирования тестов, и может быть использовано для контроля функционирования средств вычислительной техники. Цель изобретения - повышение функциональной надежности устройства за счет снижения вероятности ложной выдачи сообщения на объект. Устройство содержит две группы формирователей импульсов, формирователь импульсов, три группы триггеров, два триггера, четыре группы элементов И, три элемента И, пять элементов ИЛИ, блок памяти, три регистра, элемент задержки, генератор импульсов, группуу счетчиков, группу инверторов, инвертор, два шифратора и группу элементов ИЛИ. В устройстве повышена стабильность длительности импульсов, формирующих адрес кода теста, хранящегося в блоке памяти, и как следствие, снижена вероятность ложной выдачи сообщения на объект за счет обеспечения синхронизации управляющих импульсов, поступающих с формирователей на элементы и блоки устройства. 2 ил.

Фигл

Фиг. 2

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-07-19—Подача