канала подключен к соответствующему выходу второй группы выходов блока управления.

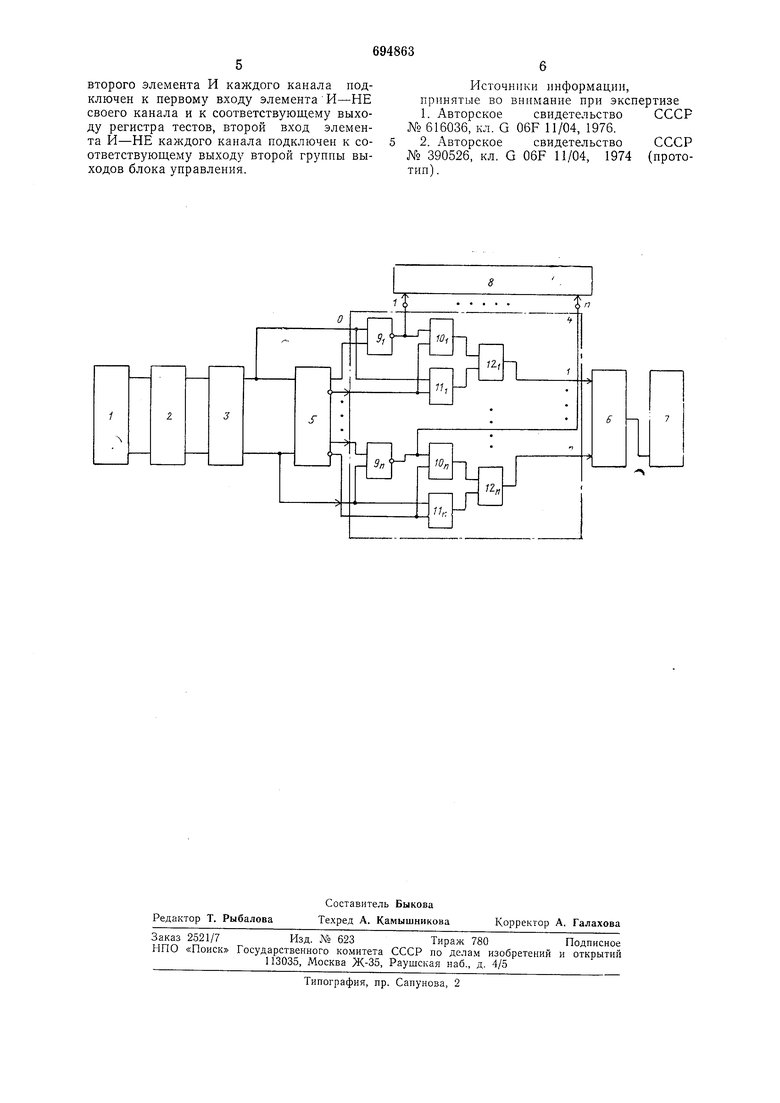

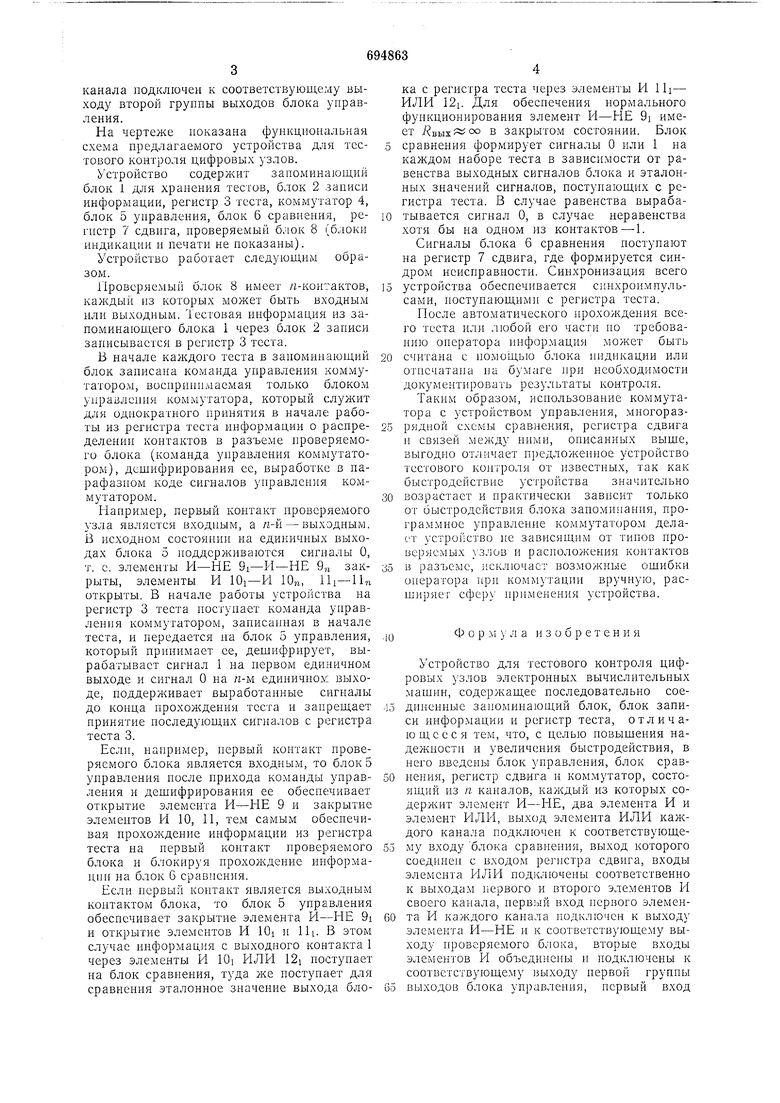

На чертеже показана функциональная схема предлагаемого устройства для тестового контроля цифровых узлов.

Устройство содержит запоминающий блок 1 для хранения тестов, блок 2 записи информации, регистр 3 теста, коммутатор 4, блок 5 управления, блок 6 сравнения, регистр 7 сдвига, проверяемый блок 8 (блоки индикации и печати не показаны).

Устройство работает следующим образом.

Проверяемый блок 8 имеет л-контактов, каждый из которых может быть входным или выходным. Тестовая информация из запоминающего блока 1 через блок 2 записи записывается в регистр 3 теста.

В начале каждого теста в запоминающий блок записана команда управления коммутатором, воспринимаемая только блоком управления коммутатора, который служит для однократного принятия в начале работы из регистра теста информации о распределении контактов в разъеме проверяемого блока (команда управления коммутатором), дещифрирования ее, выработке в парафазном коде сигналов управления коммутатором.

Например, первый контакт проверяемого узла является входным, а п-й - выходным. В исходном состоянии на единичных выходах блока 5 поддерживаются сигналы О, т. е. элементы И-НЕ 9i-И-НЕ 9„ закрыты, элементы И lOj-И 10„, lli-lln открыты. В начале работы устройства на регистр 3 теста поступает команда управления коммутатором, записанная в начале теста, и передается на блок 5 управления, который принимает ее, дешифрирует, вырабатывает сигнал 1 на первом единичном выходе и сигнал О на п-м единичном выходе, поддерживает выработанные сигналы до конца прохождения теста и запрещает принятие последующих сигналов с регистра теста 3.

Если, например, первый контакт проверяемого блока является входным, то блок 5 управления после прихода команды управления и дешифрирования ее обеспечивает открытие элемента И-НЕ 9 и закрытие элементов И 10, И, тем самым обеспечивая прохождение информации из регистра теста на первый контакт проверяемого блока и блокируя прохождение информации на блок 6 сравнения.

Если первый контакт является выходным контактом блока, то блок 5 управления обеспечивает закрытие элемента И-НЕ 9i и открытие элементов И lOi и Пь В этом случае информация с выходного контакта 1 через элементы И lOi ИЛИ 12i поступает на блок сравнения, туда же поступает для сравнения эталонное значение выхода блока с регистра теста через элементы И lli- ИЛИ 12). Для обеспечения нормального функционирования элемент И-НЕ 9i имеет в закрытом состоянии. Блок сравнения формирует сигналы О или 1 на каждом наборе теста в зависимости от равенства выходных сигналов блока и эталонных значений сигналов, поступающих с регистра теста. В случае равенства вырабатывается сигнал О, в случае неравенства хотя бы на одном из контактов-1.

Сигналы блока 6 сравнения поступают на регистр 7 сдвига, где формируется синдром неисправности. Синхронизация всего

устройства обеспечивается синхроимпульсами, поступающими с регистра теста.

После автоматического прохождения всего теста или любой его части по требованию оператора информация может быть

считана с помощью блока индикации или отпечатана на бумаге при необходимости документировать результаты контроля.

Таким образом, использование коммутатора с устройством управления, многоразрядной схемы сравнения, регистра сдвига и связей между ними, описанных выше, выгодно отличает предложенное устройство тестового контроля от известных, так как быстродействие устройства значительно

возрастает и практически зависит только от быстродействия блока запоминания, программное управление коммутатором делает устройство не зависящим от типов проверяемых узлов и расположения контактов

в разъеме, исключает возможные ощибки оператора при коммутации вручную, расширяет сферу ирименения устройства.

Формула изобретения

Устройство для тестового контроля цифровых узлов электронных вычислительных машин, содержащее последовательно соединенные запоминающий блок, блок записи информации и регистр теста, отличающееся тем, что, с целью повышения надежности и увеличения быстродействия, в него введены блок унравления, блок сравнения, регистр сдвига и коммутатор, состоящий из п каналов, каждый из которых содержит элемент И-НЕ, два элемента И и элемент ИЛИ, выход элемента ИЛИ каждого канала подключен к соответствующему входу блока сравнения, выход которого соединен с входом регистра, сдвига, входы элемента ИЛИ подключены соответственно к выходам первого и второго элементов И своего канала, первый вход первого элемента И каждого канала подключен к выходу элемента И-НЕ и к соответствующему выходу проверяемого блока, вторые входы элементов И объединены и подключены к соответствующему выходу первой группы

выходов блока управления, первый вход

второго элемента И каждого канала подключен к первому входу элемента И-НЕ своего канала и к соответствующему выходу регистра тестов, второй вход элемента И-НЕ каждого канала подключен к соответствующему выходу второй группы выходов блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 616036, кл. G 06F 11/04, 1976.

2.Авторское свидетельство СССР № 390526, кл. G 06F 11/04, 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля цифровых узлов | 1985 |

|

SU1262508A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для тестового контроля цифровых узлов электронно-вычислительных машин | 1981 |

|

SU993266A2 |

| Буферное запоминающее устройство | 1978 |

|

SU769620A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

Авторы

Даты

1979-10-30—Публикация

1976-10-13—Подача