Изофетение относится к управпенто .стационарными стационарными объектами и :мржет найти широкое применение при проектировании сие тем и испытаниях различных объектов. Известно устройство для идентификации объекта, содержашее блоки множителей, делитель, сумматоры, блок логики и реализующее алгоритм с коэффициентами , р Сп+Ч1, принимаютсими два значения: ноль и единица Однако оно обладает недоста о шо высоким быстродействием при ЫСп рГп+1 0 Наиболее близким к предлагаемому по технической сущности является устройство для идентификашш линейного обьf ЧсСп-2, )f2{ern 2,Ctn-lD)i

1 если

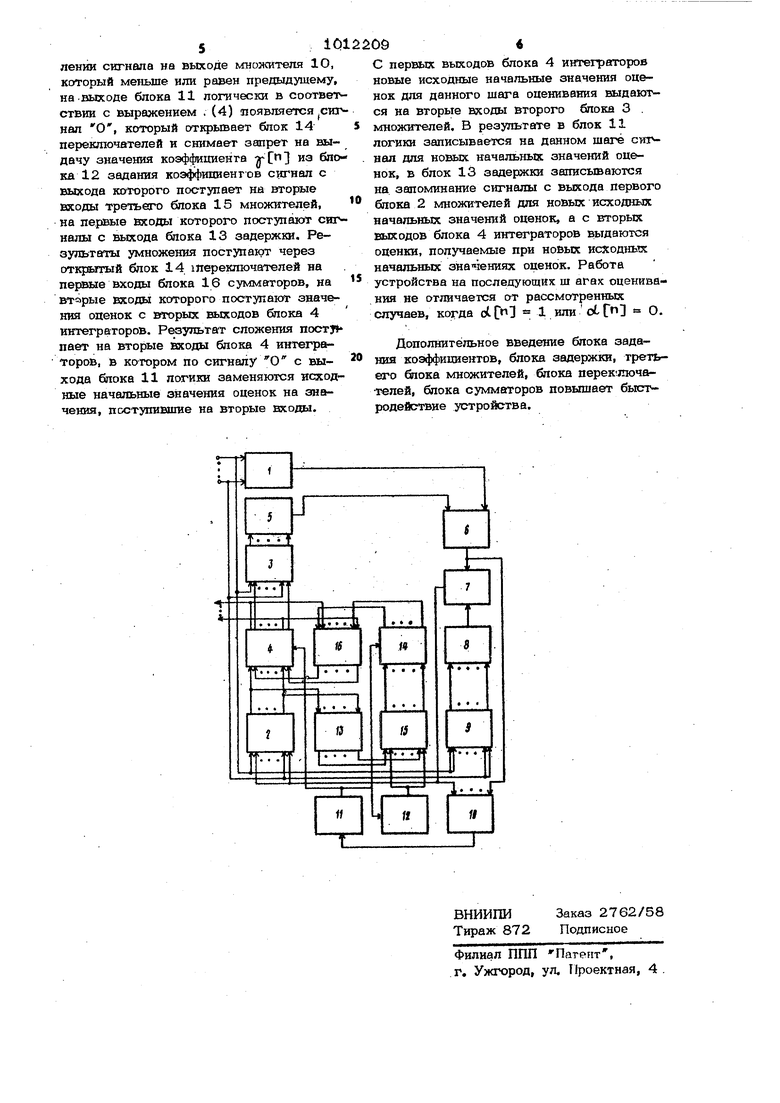

О в других случаях, где ,St1c)--ila V3Zl1sf (5 - квадрат расстояния от исходного началь ного оценки для К-го шага оценивания до К-й гиперплоскости 2. Недостатком устройства, реализукщего алгоритм (2) - (5), является относительно невысокое быстродействие при О. Цель изобретения - повышение быстродействия ycтpoйcтвa. Поставленная цель достигается тем, что устройство, содержашее последовательно соединенные первый блок множителей, блок интеграторов, вторые выходы которого являются выходом yCTpDЙC Sва, второй блок множителей, первый сумматор,. второй сумматор, подключенный вторым входом к выходу обтг екта идентификации, делитель, множ тель, блок логики, въосод которого соединен с управляющим входом блока интег раторов, последовательно соединенные блок квадратрров, третий сумматор, соединенный выходом с вторым входом делителя, первый вход и выкод которого подключены соотваетственно к второму входу множителя и к первым входам первого блока множителей, вторые входы которого соединены с входами объекта идентификации, с вторыми входами второго блока множителей и с входами блока квадраторов, содержит бясв задания коэффициентов, последовательно соединенные блок задержки, соединенный входами с

(4) екта с сильной временной корреляцией входных сигналов, описываемого в векторном виде , и где вектор параметров объекта; вектор фазовых координагг объекта. Устройство реализует алгоритм € h ccn-i х пЗ-сУ-132((2) Спиз сСп-1 с1 пз(с Сп-2 -с п--13, (5) выходами первого блока множителей, третий блок множителей, блок переклкУчателей, управлякшшй вход которогоподключен к выходу блока логики и к входу блока задания коэффициентов, блок сумматоров, вторые входы и выходы которого соединены соответственно с вторыми выходами и вторыми входами блока интегpfftopoB, выход блока задания коэффициентов подключен к вторым входам третьего блока множителей. t В данном устройстве дополнительно введена ;соррекция параметров при ctCn . В результате идентификацию производят по формулам xCn ytn 3zCn3 , V n-l} ot n Ch-2 44-otW) (с где otfhj- вычисляется в соответствии с выражением (4); ) - в соответствии с выражением (5); - некоторая монотонно аевозврашакяцая функция, удовлетворякхцая условию в случае dl О .ccn-fj ctn-aXrCrt i) хГп-43-С In-2l7M (9) или. Cn-il cCn-2 -b{yfn9 i) xrn-i V21zCn-i3 j-H- j 0, fOH 2Cn-l3 т.е. осуйхествпяетея дополнигельная коррекция исходного начального значения оценки ССп-2 и при dCn О, а в алгоригме (2) - (5) в этом случае ССп-1 ССп-1. (11) Блок задания коэффициентов выдает значение ЗгС Зв требуемые моменты времени, определяемые сигналами с выхода блока логики при о1.Сп1 О, если значения у С за даны в виде набора коэффициентов, либо может вычислять «значения , например, по формуле где гпр -число ситуаций О (тп 1,2....); L, некоторая наперед заданная ко станта, величина которой выбирается, ис ходя из априорньвс данных о процессах входа-выхода :;оот екта идентификации. Блок задержки осуществляет задержку и запоминание сигаалов с выхода пер вого блока множителей на один такт. На чертеже иаофажена функциональная схема устройства. . Устройство содержит обьокг 1 идент фикаций:., первый блок 2 множителей. второй блок 3 множителей, блок 4 интег раторов, первый сумма:тор 5, второй сум матор 6, делитель 7л третий сумматор блок 9 квадраторов, множиггель 1О, блок 11 логики, блок 12 задания коэффициентов, блок 13 задержки, блок 14 перекик чателей; третий блок 15 множителей, блок 16 сумматоров. Устройство работает следующим обра зом. При отсутствии сигналов входа-выхода объекта 1 вдентификадии на в ссодах перво1ч 2 и второго 3 блоков множителей сигналы отсутствуют, на входах третьего блока 15 множителей сигналы 10 094 акже отсутствуют. На первом и втором входах второго сумматора 6 на ЕКОДВХ множителя 1О сигналы отсутствуют И на выходе блока 11 логики сигнала нет. На вход блока 10 логически записан нулевой сигнал. Блок 14 переключателей закрыт. На выходах устройства сигналы отсутствуют. При поступлении сигналов с входов объекта 1 идентификашга на входы первого 2 и второго 3 блоков множителей на выходах второго блока 3 множителей появляются сигналы -. результагты умножения входных сигналов объекта 1 идентификации и начальных значеНИИ оценок параметров объекта, поступающих с первых выходов блока 4 интеграто- « ров на вторые входы второго блока 3 множителей. Результаты умножения поступают на входы первого сэмматора 5, с выходов которого результЕГТ суммирования поступает на первый вход второго сумматора 6, на второй ЕЖОД которого поступает сигнал с выхода объекта-1 идентификации. Результат вычитания поступает на первый вход делителя 7 и второй вход множителя 10. Н втгорой вход делителя 7 поступает сумма ЕВащ}атов входных сигналов объекта 1 идентификации, поступающих изкващаатора 9, полученная в третьем сумматоре 8. Результат деления с въпсода делителя 7 постз пает на вторые входы первого 6пока.2 множителей к первый вход множителя Юд с выхода которого результат умножения поступает на вход блока 11 логики, с выхода которого выдается сигнал 1 i так как в исходном состоянии в нем был записан нулевой сигнал.Этот сигнап 1 поступает на управляющий вход блока 4 интеграторов, не изменяя яcxoшIЫX начальных значений оценок на данном шаге, на управляющий вход блока 12 задания коэффициентов, зштрешая выдачу коэффициента. Результаты умножения с въкодов первого блока 2 множителей поступают на блок 13 задержки, записываясь на запоминание в нем, и на первые ВХОДЫ блока 4 HHierpaTopoB с BTOIS IX выходов которого выдаются значения оценок на данном шаге, а на первых выходах сохраняются исходныеначальные значения оценок. В блок 11 логикн загшсьнвается сигнал с выхода множи еля 1О. Если на последунлдих шагах оценивания значения сигналов с 1выхода множителя . 10 больше, чем на предыдущих, то работа устройства не отличается от рассмотревной и исходн ные начальные значения оценок остаются неизменными. При появ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для идентификации линейного объекта | 1986 |

|

SU1374184A1 |

| Устройство для идентификации объекта | 1979 |

|

SU960741A1 |

| Устройство для индентификации линейного объекта | 1978 |

|

SU744455A1 |

| Устройство для идентификации | 1982 |

|

SU1038924A1 |

| Система последовательного финитного управления конечным состоянием линейных стационарных динамических объектов | 1987 |

|

SU1467534A1 |

| Адаптивная система управления | 1982 |

|

SU1071996A1 |

| Адаптивная система управления | 1980 |

|

SU980070A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1994 |

|

RU2083410C1 |

| Устройство для успокоения колебаний упругого элемента переменной жесткости | 1987 |

|

SU1500990A2 |

УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ЛИНЕЙНОГО ОБЪЕКТА, содержащее последовательно соединенные первый блок множителей, блок интегра: торов, вторые выходы каторого являюпгся-)зыходом устройства, второй блок множителей, первый сумматор, второй /сумматор, подключенный вторым входом к выходу объекта идентификации, делитель, множитель, блок логики которого соединен с управляющим входом блока интеграторов, последовательно соединенные блок квадратов, третий сумматор, соединенный выходом с вторым входом делителя, пернвый вход и выход которого подкгаочены соответственно к второму входу множителя и к первым входам первого блока множителей, вторые входы которого соединены с входами объекта идентификации, с вторыми входами второго блока множителей и с входами лблока квадраторов, отличающееся тем, что, с целью повышения быстродействия уст ройства, оно содержит бпок задания коэффициентов, последовательно соединеншле блок задержки, соединенный входами с выходами первого блока множителей, третий блок множителей, блок переклк чателей, управляющий вход которого под(Л ключен к выходу блока логики и к входу блока задания коэффициентов, блок сумматоров, вторые входы и выходы которого соединены соатветствекно с 19торымв : выходами и вторыми входами блока интеграторов, выход блока задания коэффициентов подключен к вторым Еосодам третьего блока множителей. ьэ О со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аведьян Э | |||

| Д., Цьшкин Я | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Обоб щенный алгоритм Качмажа | |||

| - Автоматика ;И телемеханика, 1979 № 1, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| (прототип). | |||

Авторы

Даты

1983-04-15—Публикация

1981-11-25—Подача