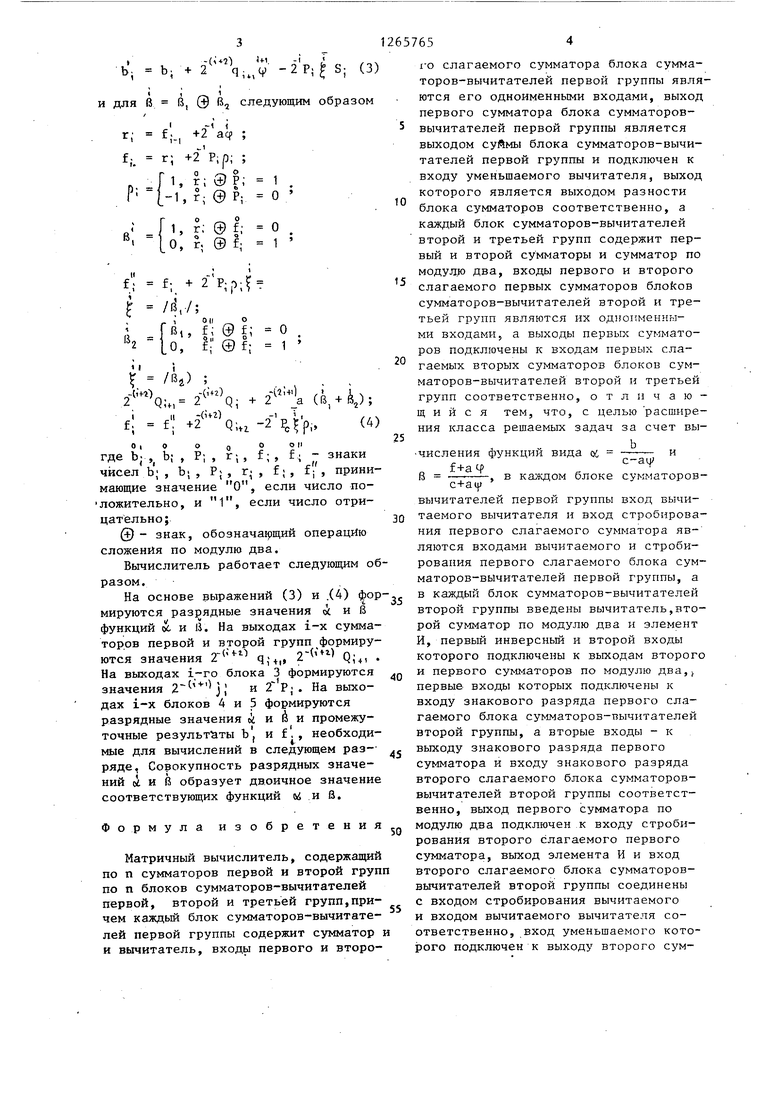

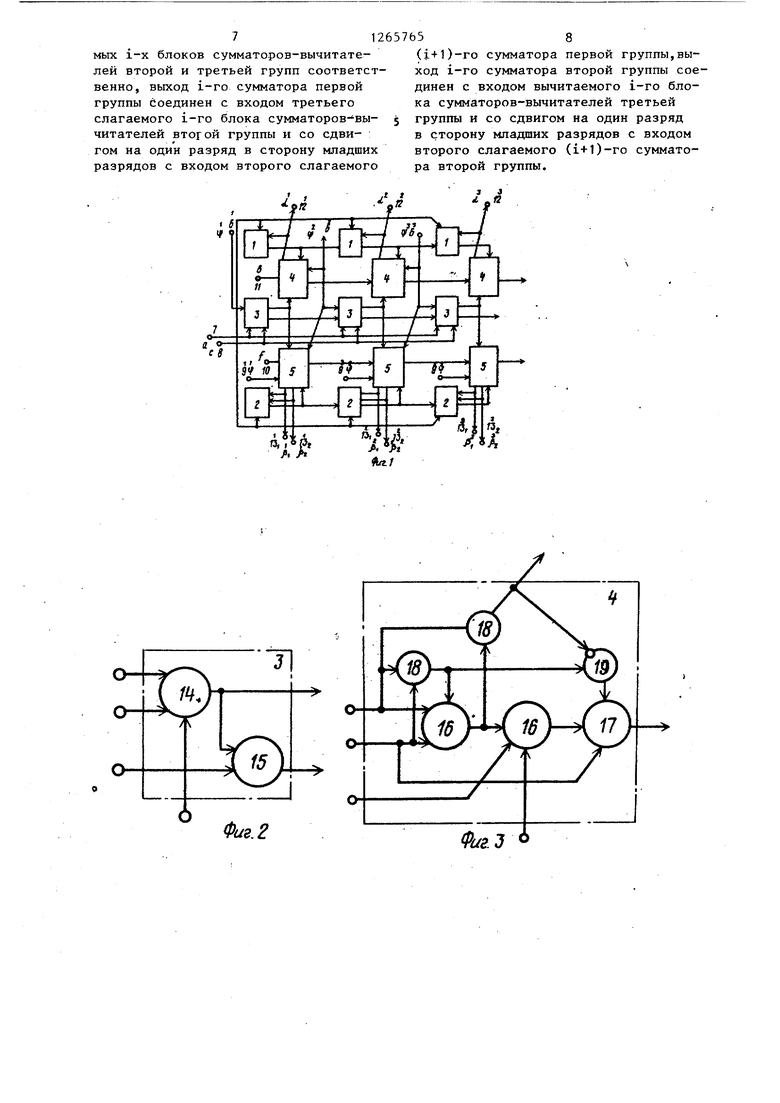

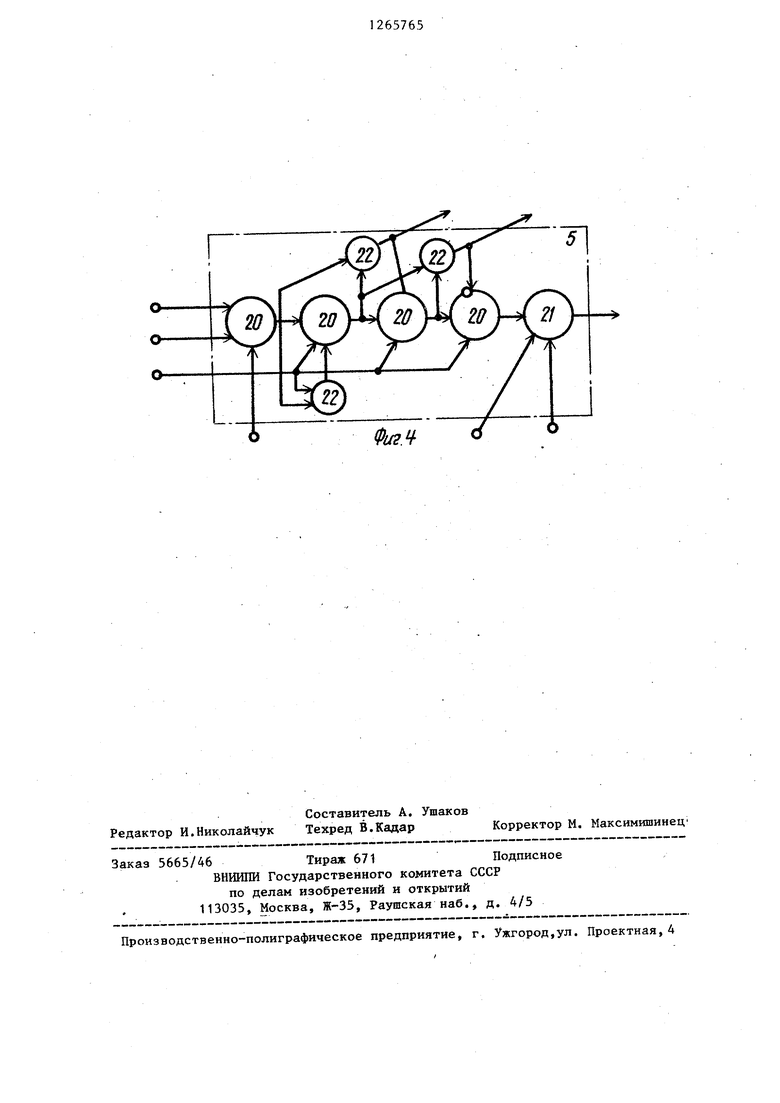

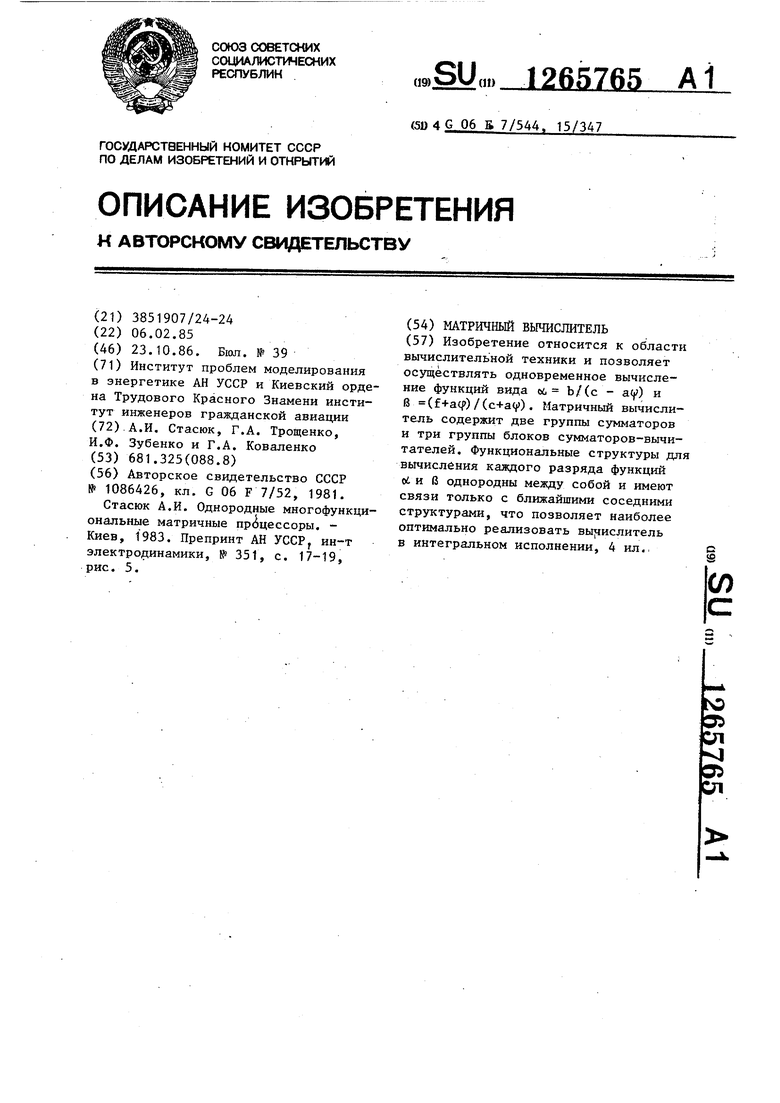

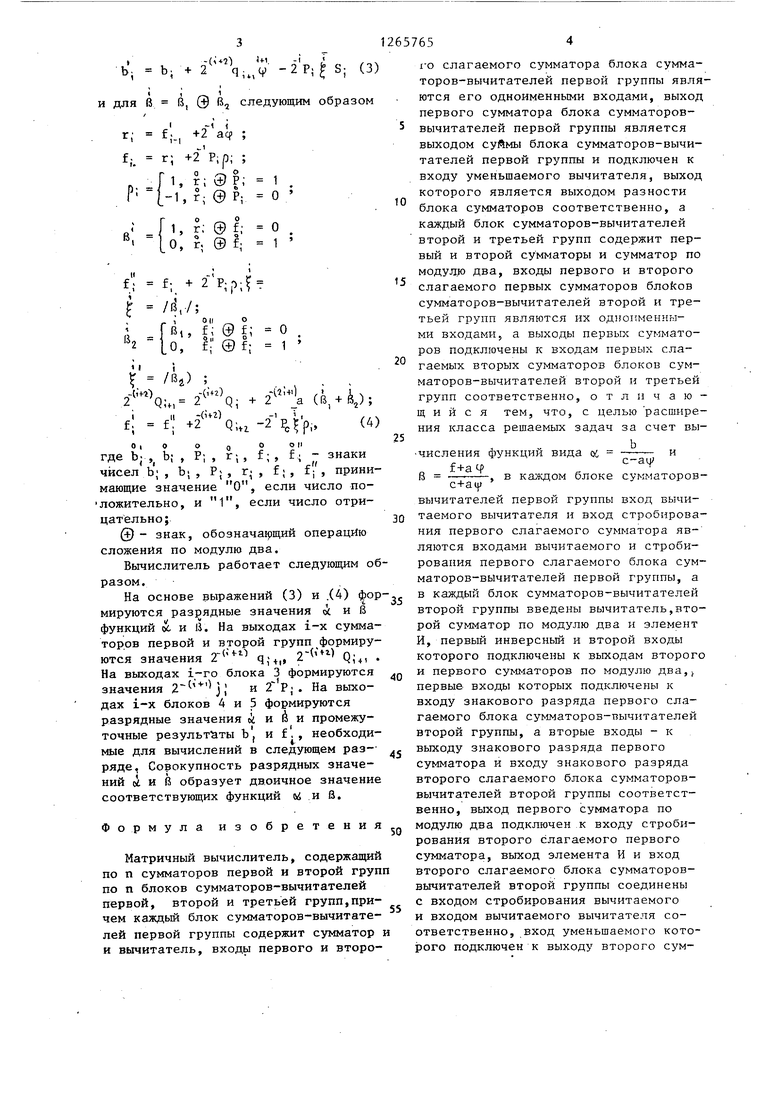

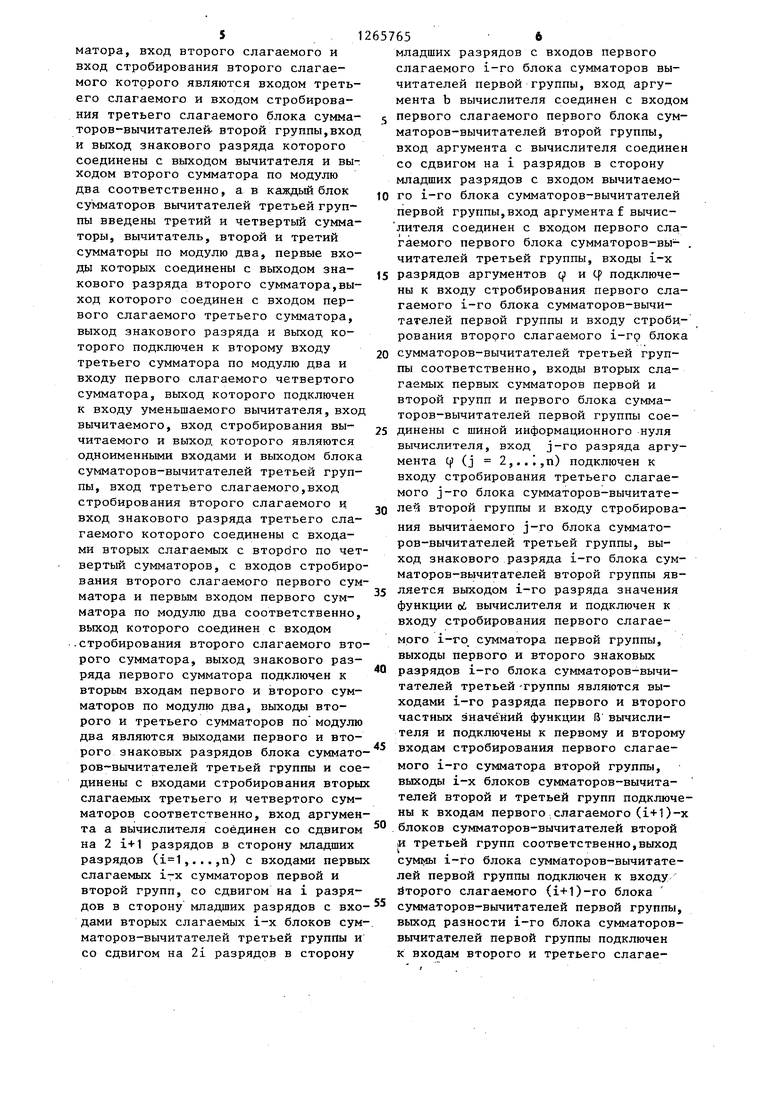

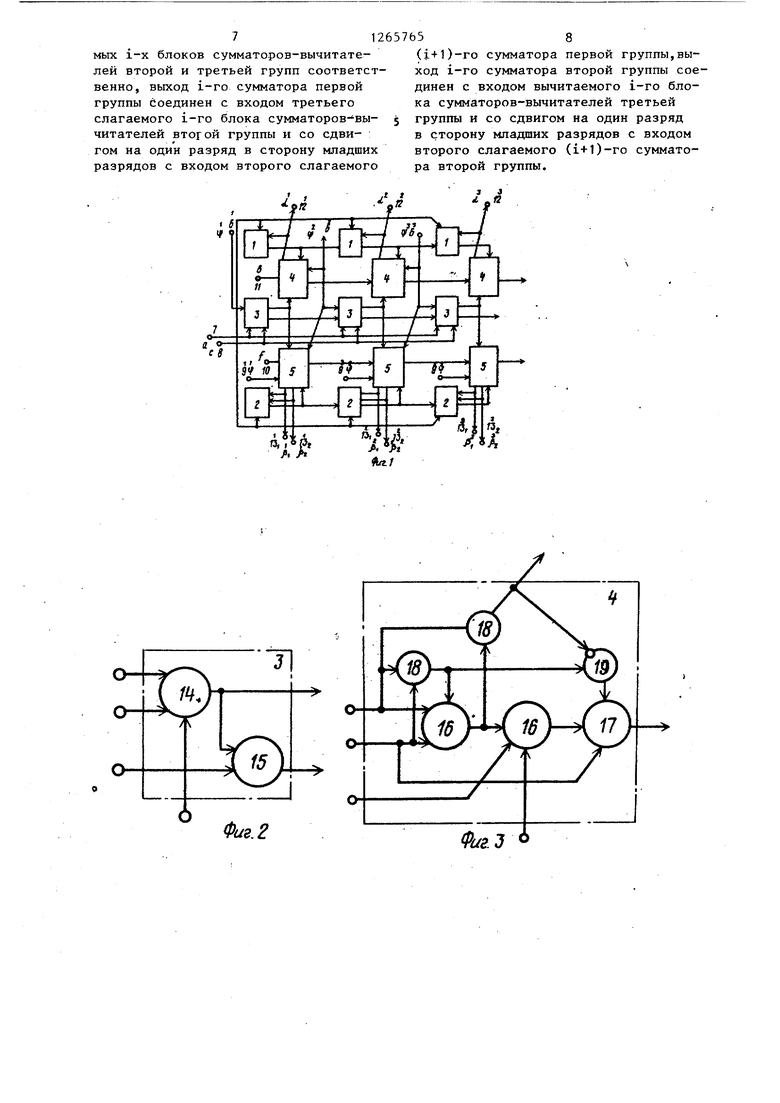

Изобретение относится к вычислительной технике и может быть использовано в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для оперативного вычисления прогоночных коэффициентов при решении дифференциальных уравненийметодом прогонки. Целью изобретения является расшире ние класса решаемых задач за счет вычисления функций вида ui На фиг, 1 приведена структурная схема матричного вычислителя; на фиг. 2-4 - функциональные схемы блоков сумматоров-вычитателей с первой по третью группу соответственно. Матричный вычислитель (фиг. 1) содержит по п сумматоров 1 и 2 первой и второй групп и по п блоков сумматоров-вычитателей 3-5 соответст венно первой, второй и третьей групп Аргументы if , а, с, ср , f, b поступают на входы 6-11 устройства соответственно . Разрядные значения функций W и i-e разряды первого и.вторрго частных значений функции В., и { фор мируются на выходах 12 и 13,, 13 соответств енно. Блок 3 (фиг.2) содержит сумматор I 14 и вычитатель 15. Блок 4 (фиг. 3) содержит два сумI - . матора 16, вычитатель 17, два сумматора 18 по модулю два и элемент И 19 Блок 5 (фиг. 4) содержит четыре с сумматора 20, вычитатель 21 и три ..сумматора 22 по модулю два. Вычислитель реализует вычисление функций: и1Л - ) c+a(fc-aif которое осуществляется следующим образом. Представим выражение (1) в разряд ной форме как U;4(() 0; (, ( У « п t , , р t где b7(b,b,...,b) ,et (о,с4,...,«) И (В,В|), (,,...,) , О (о,о,...,о) - разрядные векторы представляющие собой разрядное изображение чисел Ь,о6 , И, f, О соответственно;. , г 1 i ,-fc ((jf,(f,...,(f) - разрядный векбражающий число ф ые матрицы, представляющие азрядное изображение чисел при п 4 соответственно. щем случае выражение для выя каждо о i-ro разряда , В в cd и В могут быть предс авя «. соответственно как -(;t. -2i i 2. if;.,+2 av ; Ъ 2-f j;-2c5 t 2 P,. S, p. b,lo, b;., fl, B; @P; -1, B; ® P; / /; o-( , , -(;+г1 qU, 2 q; + 2 aoi Ъ- b; .,ф- -2Р; S; (3 /и для и в, (Э 2 следующим образом I-( 1 f;., +2 acf ; f;. г; +2 Р;р; ; 1, г; ® Р; 1 . -1,г; ©Р, О ОV 1, г; @ f; О . о, г, ® f; 1 + 2 Р;р; f /,/; /- 1 °1 ° В o.i ® ° о, f; @f; 1 V /йа) ; . , У%;., . (В,.,); 11-()- I f +2 Q;,, -2 Р,р,, f, f: +2- -Q;,, -2 РЛР,-,(О 0)0о Qо о II где Ь; , Ь; , Р; , г-,, f;, f; - знаки чисел b; , b; , Р;, г- , f;, f; , прини 0 если число помающие значение w , ложительно, и 1, если число отрицательно; (+) - знак, обозначающий операцию сложения по модулю два. Вычислитель работает следующим о разом. На основе выражений (3) и .(4) фо мируются разрядные значения ос и В функций об и и. На выходах i-x сумма торов первой и второй групп формиру ются значения q,-,,, Q;,, На выходах i-ro блока 3 формируются значения и 2) . На выходах i-x блоков 4 и 5 формируются разрядные значения i и В и промежуточные результаты Ь, и f,, необходи мые для вычислений в следующем разряде, Совокупность разрядных значений i и В образует дв.оичное значени соответствующих функций &4 и и. Формула изобретени Матричный вычислитель, содержащи по п сумматоров первой и второй гру по п блоков сумматоров-вычитателей первой, второй и третьей групп,при чем каждьй блок сумматоров-вычитате лей первой группы содержит сумматор и вычитатель, входы первого и второ го слагаемого сумматора блока сумматоров-вычитателей первой группы являются его одноименными входами, выход первого сумматора блока сумматороввычитателей первой группы является выходом суймы блока сумматоров-вычитателей первой группы и подключен к входу уменьшаемого вычитателя, выход которого является выходом разности блока сумматоров соответственно, а каждый блок сумматоров-вычитателей второй и третьей групп содержит первый и второй сумматоры и сумматор по модулю два, входы первого и второго слагаемого первых сумматоров 6nokoB сумматоров-вычитателей второй и третьей групп являются их одноименными входами 5 а выходы первых сумматоров подключены к входам первых слагаемых вторых сумматоров блоков сумматоров-вычитателей второй н третьей групп соответственно, отличающийся тем, что, с целью расширения класса решаемых задач за счет вы, - Ь числения функции вида ос и в каждом блоке сумматоровc+a()J вычитателей первой группы вход вычитаемого вычитателя и вход стробирова- ния первого слагаемого сумматора являются входами вычитаемого и стробировапия первого слагаемого блока сумматоров-вычитателей первой группы, а в каждый блок сумматоров-вычитателей второй группы введены вычитатель,второй сумматор по модулю два и элемент И, первый инверсный и второй входы которого подключены к выходам второго и первого сумматоров по модулю два, первые входы которых подключены к входу знакового разряда первого слагаемого блока сумматоров-вычитателей второй группы, а вторые входы - к выходу знакового разряда первого сумматора и входу знакового разряда второго слагаемого блока сумматороввычитателей второй группы соответственно, выход первого сумматора по модулю два подключен к входу стробирования второго слагаемого первого сумматора, выход элемента И и вход второго слагаемого блока сумматороввычитателей второй группы соединены с входом стробирования вычитаемого и входом вычитаемого вычитателя соответственно, вход уменьшаемого котоporo подключен к выходу второго сумматора, вход второго слагаемого и вход стробирования второго слагаемого которого являются входом третьего слагаемого и входом стробирования третьего слагаемого блока сумматоров-вычитателе второй группы,вход и выход знакового разряда которого соединены с выходом вычитателя и выходом второго сумматора по модулю два соответственно, а в каждый блок сумматоров вычитателей третьей группы введены третий и четвертый сумматоры, вычитатель, второй и третий сумматоры по модулю два, первые входы которых соединены с выходом знакового разряда второго сумматора,выход которого соединен с входом первого слагаемого третьего сумматора, выход знакового разряда и выход которого подключен к второму входу третьего сумматора по модулю два и входу первого слагаемого четвертого сумматора, выход которого подключен к входу уменьшаемого вычитателя, вход вычитаемого, вход стробирования вычитаемого и выход, которого являются одноименными входами и выходом блока сумматоров-вычитателей третьей группы, вход третьего слагаемого,вход стробирования второго слагаемого и вход знакового разряда третьего слагаемого которого соединены с входами вторых слагаемых с BTopdro по четвертый сумматоров, с входов стробирования второго слагаемого первого сумматора и первым входом первого сумматора по модулю два соответственно, выход которого соединен с входом .стробирования второго слагаемого второго сумматора, выход знакового разряда первого сумматора подключен к вторым входам первого и второго сумматоров по модулю два, выходы второго и третьего сумматоров по модулю два являются выходами первого и второго знаковых разрядов блока сумматоров-вычитателей третьей группы и соединены с входами стробирования вторых слагаемых третьего и четвертого сумматоров соответственно, вход аргумента а вычислителя соединен со сдвигом на 2 i+1 разрядов в сторону младших разрядов (,...,п) с входами первых слагаемых i-x сумматоров первой и второй групп, со сдвигом на i разрядов в сторону младших разрядов с входами вторых слагаемых i-x блоков сумматоров-вычитателей третьей группы и со сдвигом на 21 разрядов в сторону

младших разрядов с входов первого слагаемого 1-го блока сумматоров вычитателей первой группы, вход аргумента b вычислителя соединен с входом первого слагаемого первого блока сумматоров-вычитателей второй группы, вход аргумента с вычислителя соединен со сдвигом на i разрядов в сторону младших разрядов с входом вычитаемого 1-го блока сумматоров-вычитателей первой группы,вход аргумента f вычислителя соединен с входом первого слагаемого первого блока сумматоров-вычитателей третьей группы, входы 1-х разрядов аргументов ( н fJf подключены к входу стробирования первого слагаемого 1-го блока сумматоров-вычитателей первой группы и входу стробирования второго слагаемого 1-го блока сумматоров-вычитателей третьей группы соответственно, входы вторых слагаемых первых сумматоров первой и второй групп и первого блока сумматоров-вычитателей первой группы соединены с шиной информационного нуля вычислителя, вход j-ro разряда аргумента tf (J 2,..i,n) подключен к входу стробирования третьего слагаемого j-ro блока сумматоров-вычитателей второй группы и входу стробирования вычитаемого j-ro блока сумматоров-вычитателей третьей группы, выход знакового разряда 1-го блока сумматоров-вычитателей второй группы является выходом 1-го разряда значения функции oi вычислителя и подключен к входу стробирования первого слагаемого 1-го сумматора первой группы, выходы первого и второго знаковых разрядов 1-го блока сумматоров-вычитателей третьей -группы являются выходами 1-го разряда первого и второго частных значёний функции li вычислителя и подключены к первому и второму входам стробирования первого слагаемого 1-го сумматора второй группы, выходы i-x блоков сумматоров-вычитателей второй и третьей групп подключены к входам первого слагаемого (i+1).блоков сумматоров-вычитателей второй и третьей групп соответственно,выход суммы i-ro блока сумматоров-вычитателей первой группы подключен к входу второго слагаемого (i+1)-го блока сумматоров-вычитателей первой группы, выход разности 1-го блока сумматороввычитателей первой группы подключен к входам второго и третьего слагаемых i-x блоков сумматоров-вычитателей второй и третьей групп соответственно, выход i-ro сумматора первой группы соединен с входом третьего слагаемого i-ro блока сумматоров-вычитателей втогой группы и со сдвигом на один разряд в сторону младших разрядов с входом второго слагаемого

(i+1)-ro сумматора первой группы,выход i-ro сумматора второй группы соединен с входом вычитаемого i-ro блока сумматоров-вычитателей третьей группы и со сдвигом на один разряд в сторону младших разрядов с входом второго слагаемого (i+1)-ro сумматора второй группы.

i

V

«С лК

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Вычислительное устройство | 1985 |

|

SU1272330A1 |

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Цифровой гармонический анализатор | 1979 |

|

SU873148A1 |

| Матричный вычислитель | 1989 |

|

SU1647558A1 |

Изобретение относится к области вычислительной техники и позволяет осуществлять одновременное вычисление функций вида сб Ь/(с - ау) и 6 (f+a(f) / (c+av). Матричный вычислитель содержит две группы сумматоров и три группы блоков сумматоров-вычитателей. Функциональные структуры для вычисления калодого разряда функций ot и В однородны между собой и имеют связи только с ближайшими соседними структурами, что позволяет наиболее оптимально реализовать вы ислитель в интегральном исполнении, 4 ил.. (Л

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стасюк А.И | |||

| Однородные многофункциональные матричные процессоры | |||

| Киев, 1983 | |||

| Препринт АН УССР, ин-т электродинамики, № 351, с | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-23—Публикация

1985-02-06—Подача