Изобретение относится к вычислительной технике и может быть использовано в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для увеличения автоматическо- го управления быстропротекающими процессорами или динамическими объектами.

Цель изобретения - расширение класса решаемых задач за счет вычис-

ления функхщи вида

«

5.

х;; УЛ

20

25

где m - количество аргументов х; и у;.

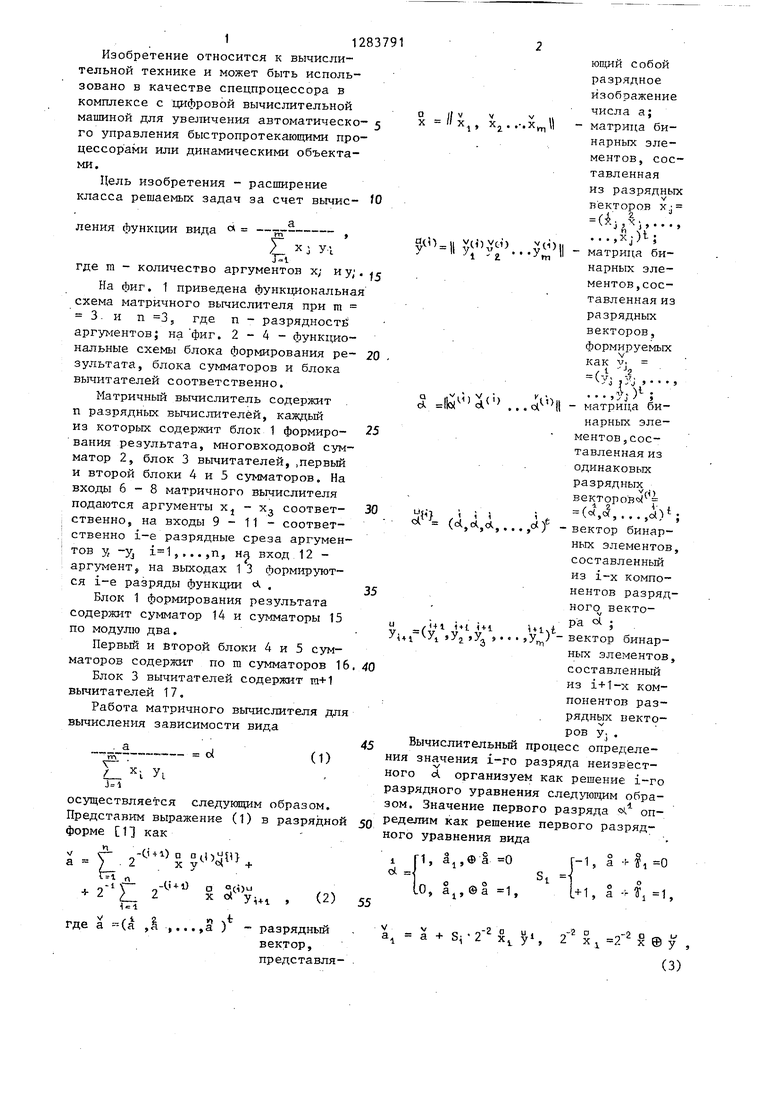

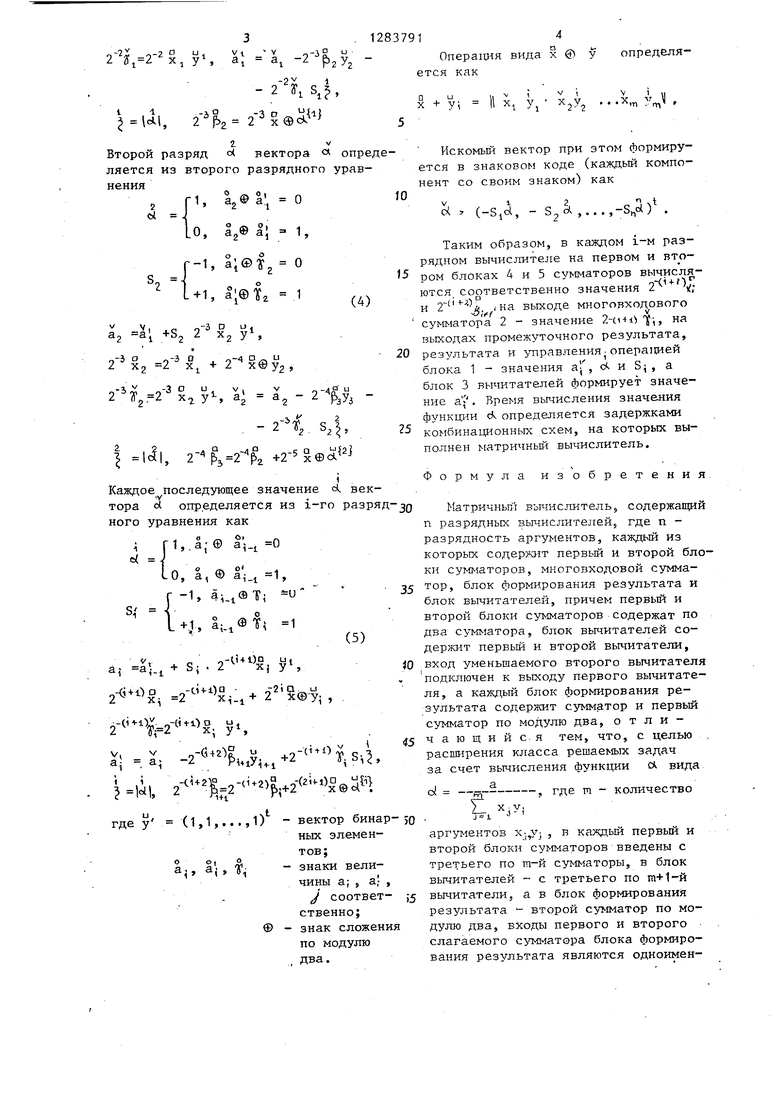

На фиг. 1 приведена функциональная схема матричного вычислителя при m 3- и п 3, где п - разрядности аргументов; на фиг. 2 - 4 - функциональные схемы блока формирования результата, блока сумматоров и блока вычитателей соответственно.

Матричный вычислитель содержит п разрядных вычислителей, каждый из которых содержит блок 1 формирования результата, многовходовой сумматор 2, блок 3 вычитателей, .первый и второй блоки 4 и 5 сумматоров. На входы 6-8 матричного вычислителя подаются аргументы х,, - х соответ ственно, на входы 9 - 11 - соответственно i-e разрядные среза аргументов у, -у ,...,п, на вход, 12 - аргументJ на выходах 1 3 формируются i-e разряды функции , ,

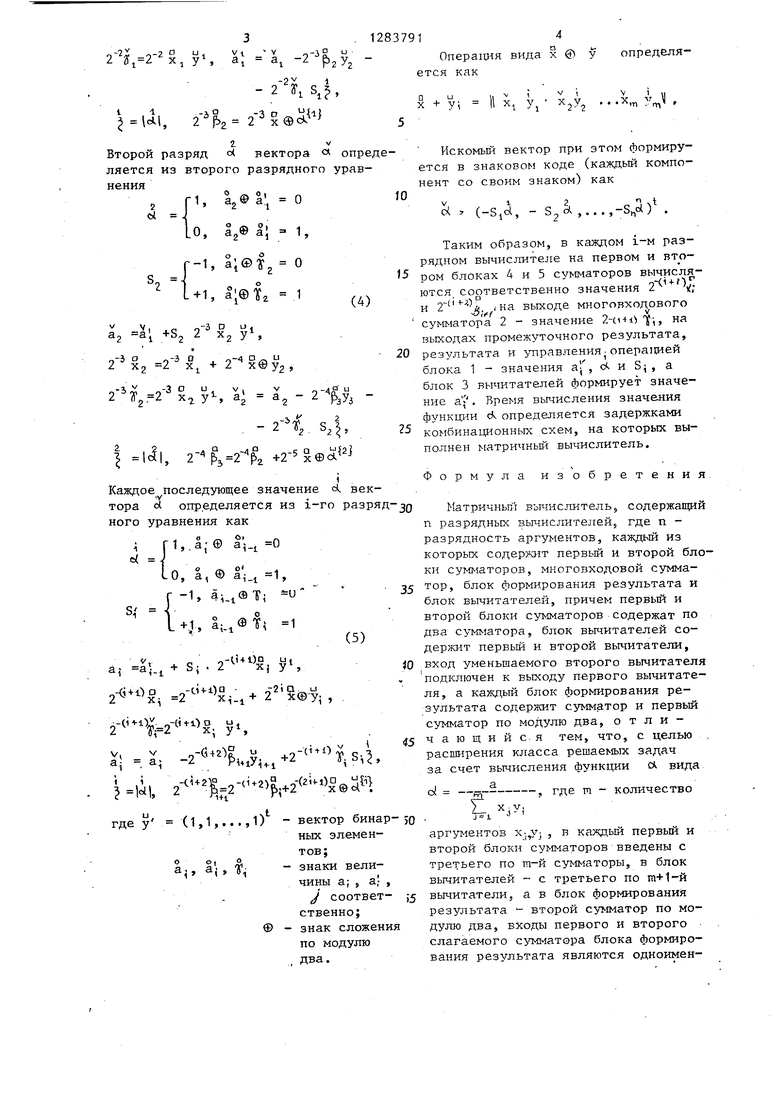

Блок 1 формирования результата содержит сумматор 14 и сумматоры 15 по модулю два.

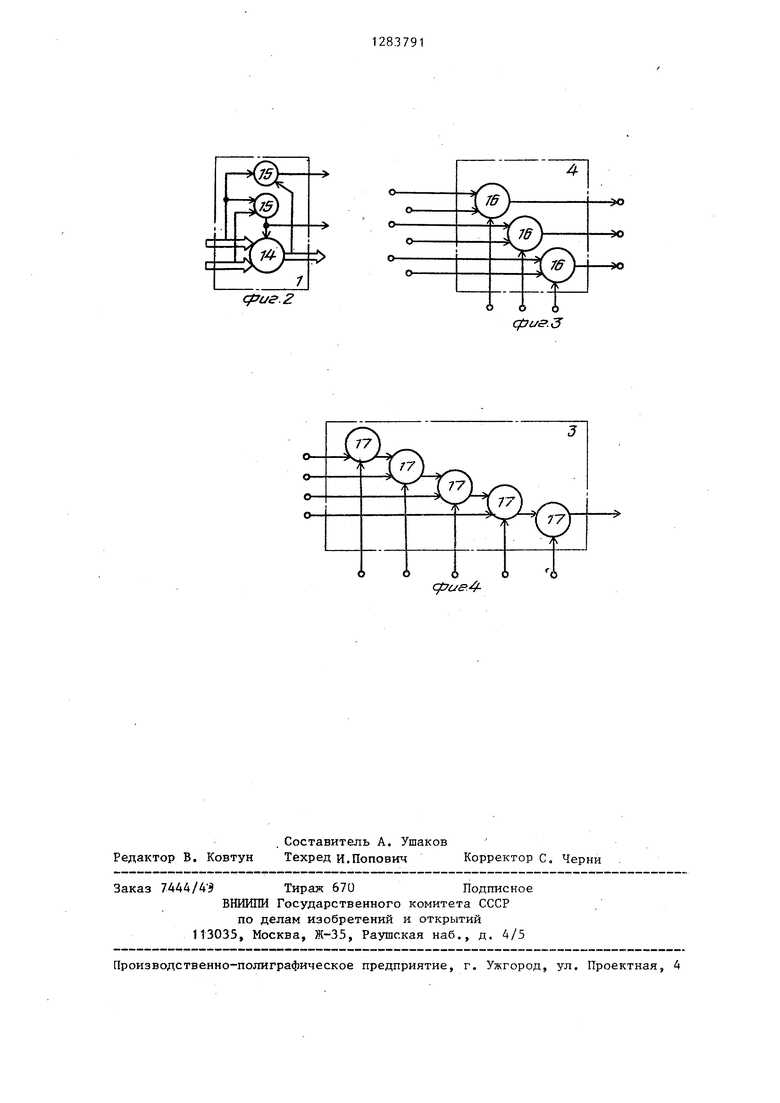

Первый и второй блоки 4 и 5 сумматоров содержит по m сумматоров 16

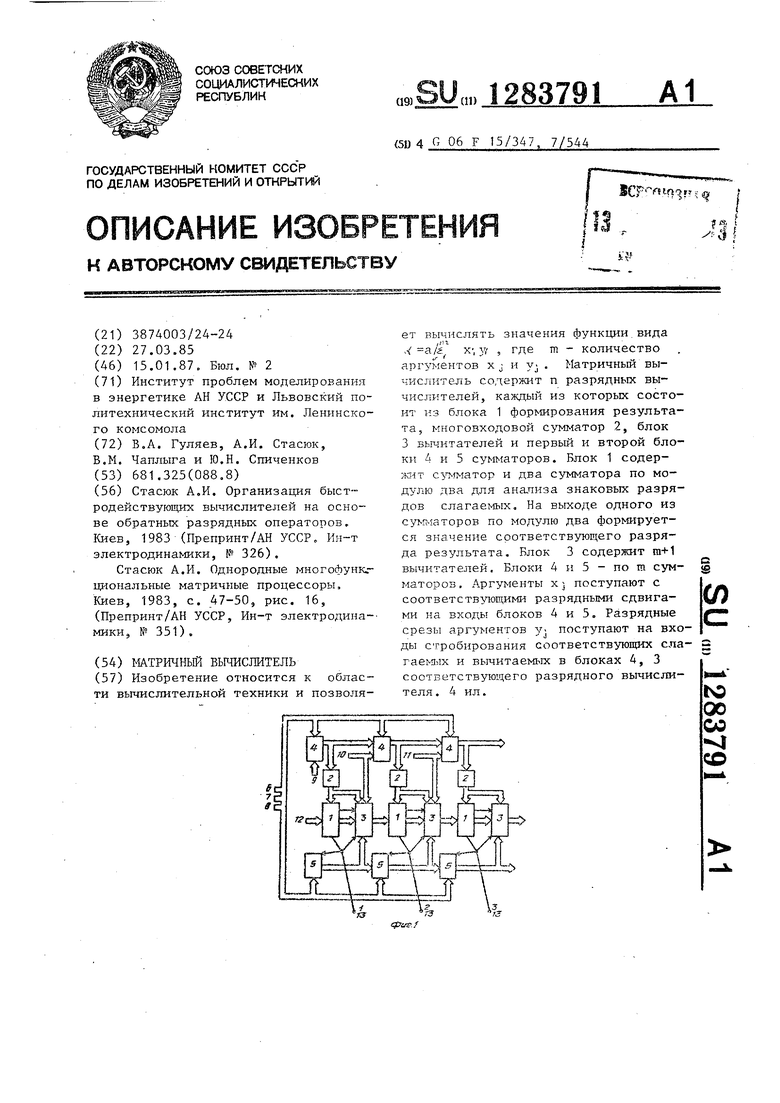

Блок 3 вычитателей содержит та+1 вычитателей 17.

Работа матричного вычислителя для вычисления зависимости вида

- 30

35

40

а

d

(Д,Д,А,

и /HI i + 1 f + 1

.Уг.Уз

...,Xj)t; матрица бинарных элементов, составленная из разрядных векторов, формируемых

V

как V.

/ 1 - 2

(yj . ,i-);

.«( ll - матрица бинарных элементов, составленная из одинаковых разрядных векторов 5( , (V,...,oiy

,,0) -вектор бинарных элементов составленный из i-x компонентов разряд ного векто. Ра ° I Ui.t , - вектор бинарных элементов составленный из i+1-x компонентов разрядных векторов у.

d

/

У1

Вычислительный процесс определе- (1) ния значения i-ro разряда неизвёст- d

ного d организуем как решение i-ro разрядного уравнения следующим образом. Значение первого разряда определим как решение первого разрядного уравнения вида

осуществляется следующим образом. Представим выражение (1) в разрядной форме 11 как

2 X (.

г ч

„-0-И)

где а

I,

Ъ -а д

0(4) и

yui

(2)

,а ) - разрядный вектор,

представля- 5 О

20

25

;.

я

6

я

30

35

40

о

X

1

V X,

ас)) ., vU)...)||

а

d

(Д,Д,А,

и /HI i + 1 f + 1

.Уг.Уз

ющий собой разрядное изображение числа а; матрица бинарных элементов, составленнаяиз разрядных

V

векторов xj (f. X.

VXj,,X . ..,

...,Xj)t; матрица бинарных элементов, составленная из разрядных векторов, формируемых

V

как V.

/ 1 - 2

(yj ..

,i-);

.«( ll - матрица бинарных элементов, составленная из одинаковых разрядных векторов 5( , (V,...,oiy;

,,0) -вектор бинарных элементов, составленный из i-x компонентов разрядного векто. Ра ° I Ui.t , - вектор бинарных элементов, составленный из i+1-x компонентов разрядных векторов у.

Вычислительный процесс определе- ния значения i-ro разряда неизвёст- d

ного d организуем как решение i-ro разрядного уравнения следующим образом. Значение первого разряда определим как решение первого разрядного уравнения вида

-1, а -ь I, 0

Ы

-1, I

1

i 0

10, ,,© 1,

ч у

Oj 1

1+1, а -ьЗ , 1,

V

а.

,2 -8-2- 5, y, ,2-Ч® ,

(3)

S

V I V

1 a, -2-p,, -p V

,I,

i 1 ,

i ы

Второй разряд c вектора « определяется из второго разрядного уравнения

2

Ы

I; О

1,® К

1,

S о

-1, а;© о

-и, а;©| 1

а, al +S, 2

-3 D X

2 г

0-3 о

2 X,

+ .

„-3,;;; „-30 U V, 2 Г 2 х , а

. - -

I ,

-«2-5 ФЛ

Ш

Каждое последующее значетора d определяется из

него уравнения как

ri,.I,-® а ,., 0

to, i,® I ,., 1,

Ч

1

-1, a.OTj и .1® 1

-041)0 U,

Г -Ь а., ,

а,- aV., -ь Si- S .OP, )-1 yS

-2

-(i-H)

.yu..S.b )-.2.iM)

f {

1+1

где у (1,1 ,... ,1) - вектор бинар-JQ

ных элементов;- знаки велиХ-У;

°1 S, а, a j, -у,

ЧИНЫ a; 5 a,- ,

аргументов , в каждый первьй и второй блоки сумматоров введены с третьего по т-й сумматоры, в блок вычитателей - с третьего по m+1-й соответ- ;5 вычитатели, а в блок формирования ственно; результата - второй сумматор по мо- - знак сложения дулю два, входы первого и второго по модулю слагаемого сум1 1атора блока формиро- два.вания результата являются одноимен12837914

Onepaip-iH вида x @ у ется как

определяX + у

,

m .

вектор при этом формируется в знаковом коде (каждый компонент со своим знаком) как

V 1 2 vt

Ы (-Sjd, - 5,,...,-5,Ы) .

4)

Таким образом, в каждом i-м разрядном вычислителе на первом и 1-5 ром блоках 4 и 5 сумматоров вычисляются соответственно значения 2 V;

и 2-. ,

.на выходе многовходового

су -шатора 2 - значение 2-(i + i J-,, на выходах промежуточного результата,

20 результата и з правления-операдаей блока 1 - значения , с и S , а блок 3 вычитателей формирует значение а ; , Бремя вычисления значелия функц и Л определяется задержками

комбинационных схем, на которых выполнен aтpичньD вычислитель.

Формула изобретения.

веказряд- Q

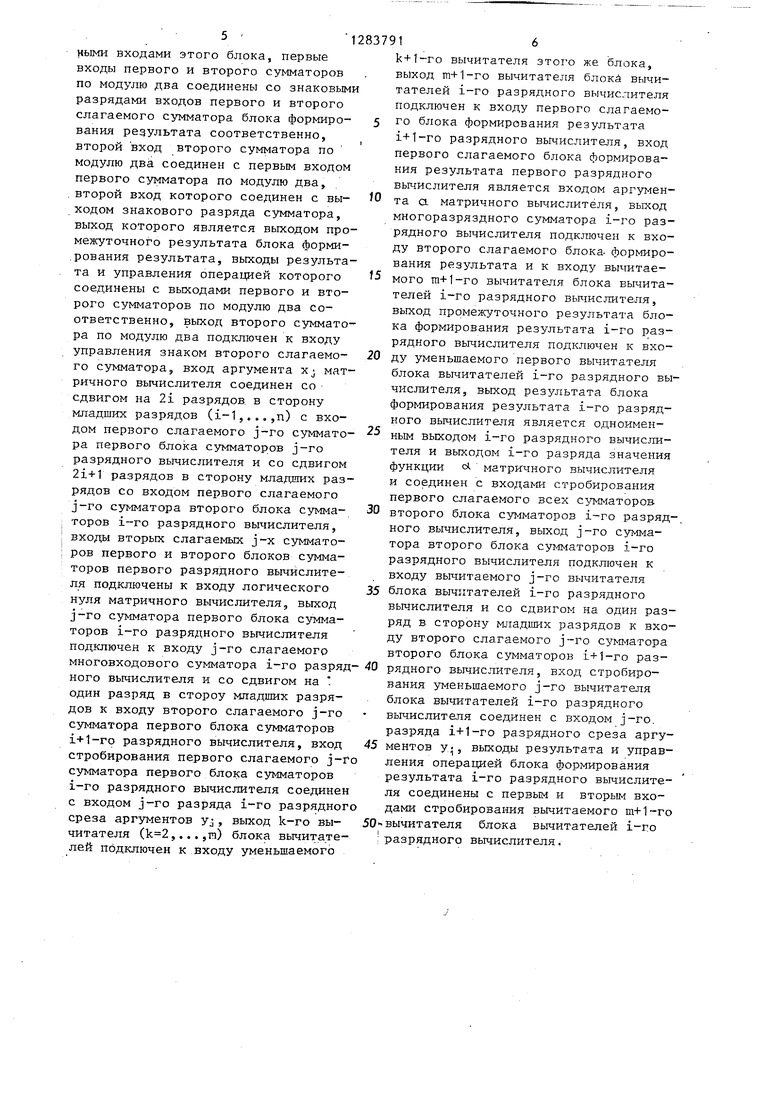

S.b yi

Матричньш вычислитель5 содержащий п разрядных вычислителей, где п - разрядность аргументов, каждый из которьк содержит первый и второй блоки сумматоров, многовходовой сумма- 35 блок формирования результата и блок вычитателей, причем первый и второй блоки сумматоров содержат по два сумматора, блок вычитателей содержит первый и второй вьгчитатели, 10 вход уменьшаемого второго вычитателя подключен к выходу первого вычитателя, а каждый блок формирования результата содержит сумматор и первый сумматор по модулю два, отли- { 45 тем, что, с целью расширения класса peшae 5ыx задач за счет вьтисления функции с вида а

d , где ш - количество

Х-У;

ными входами этого блока, первые входы первого и второго сумматоров по модулю два соединены со знаковым разрядами входов первого и второго слагаемого сумматора блока формирования результата соответственно,

второй вход второго сумматора по модулю два соединен с первьпч входом первого сумматора по модулю два, второй вход которого соединен с выходом знакового разряда сумматора, выход которого является выходом промежуточного результата блока форми- .рования результата, выходы результата и управления операцией которого соединены с выходами первого и второго сумматоров по модулю два соответственно, выход второго сумматора по модулю два подключен к входу управления знаком второго слагаемого сумматора, вход аргумента xj матричного вычислителя соединен со сдвигом на 21 разрядов, в сторону младших разрядов (i-1,..,,n) с входом первого слагаемого j-ro сумматора первого блока сумматоров j-ro разрядного вычислителя и со сдвигом 21+1 разрядов в сторону младших разрядов со входом первого слагаемого j-ro сумматора второго блока сумматоров 1-го разрядного вычислителя, входы вторых слагаемых j-x сумматоров первого и второго блоков сумматоров первого разрядного вычислителя подключены к входу логического нуля матричного вычислителя, выход j-ro сумматора первого блока сумматоров 1-го разрядного вычислителя подключен к входу j-ro слагаемого

многовходового сумматора 1-го разряд- 40 рядного вычислителя, вход стробироного вычислителя и со сдвигом на , один разряд в стороу младших разрядов к входу второго слагаемого j-ro сумматора первого блока сумматоров i+1-го разрядного вычислителя, вход стробирования первого слагаемого j-fo сумматора первого блока сумматоров 1-го разрядного вычислителя соединен с входом J-го разряда 1-го разрядного среза аргументов yj, выход k-ro вычитателя (,..,,m) блока вычитателей подключен к входу уменьшаемого

I

Ю

15

2837916

k+1-го вычитателя зтого же блока, выход m+1-ro вычитате1 я блоки вычи- тателей 1-го разрядного вычислителя подключен к входу первого слагаемого блока формирования результата 1+1-го разрядного вычислителя, вход первого слагаемого блока формирования результата первого разрядного вычислителя является входом аргумента а матричного вычислителя, выход многоразряздного сумматора 1-го разрядного вычислителя подключен к входу второго слагаемого блока- формирования результата и к входу вычитаемого m+1-ro вычитателя блока вычита- телей 1-го разрядного вычислителя, выход промежуточного результата блока формирования результата 1-го разрядного вычислителя подключен к входу уменьшаемого первого вычитателя блока вычитателей 1-го разрядного вычислителя, выход результата блока формирования результата 1-го разрядного вычислителя является одноименным выходом 1-го разрядного вычиcJШ- теля и выходом 1-го разряда значения функции сА матричного вычислителя и соединен с входами стробирования первого слагаемого всех сумматоров второго блока сумматоров разряд-, ного вычислителя, выход j-ro сумматора второго блока сумматоров i-ro разрядного вычислителя подключен к входу вычитаемого j-ro вычитателя блока вычитателей 1-го разрядного вычислителя и со сдвигом на один разряд в сторону младших разрядов к входу второго слагаемого j-ro сумматора второго блока сумматоров i+1-го раз20

25

30

35

вания уменьшаемого j-ro вычитателя блока вычитателей 1-го разрядного вычислителя соединен с входом j-ro. разряда i+1-го разрядного среза аргу45 ментов у-, выходы результата и управления операцией блока формирования результата i-ro разрядного вычислителя соединены с первым и вторым входами стробирования вычитаемого

50 Вычитателя блока вычитателей i-ro : разрядного вычислителя,

.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1983 |

|

SU1265793A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Матричный вычислитель логарифмов | 1981 |

|

SU1012251A1 |

| Матричный вычислитель | 1982 |

|

SU1083185A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для деления | 1981 |

|

SU1051535A1 |

| Вычислительное устройство | 1985 |

|

SU1272330A1 |

Изобретение относится к области вычислительной техники и позволяет вычислять значения функции.вида Х;У( , где та - количество аргументов Xj и у . Матричный вычислитель содержит п разрядных вычислителей, каждый из которых состоит из блока 1 формирования результата, многовходовой сумматор 2, блок 3 вычитателей и первый и второй блоки 4 и 5 сумматоров. Блок 1 содер- ;кит с тматор и два сумматора по модулю два для ана.пиза знаковых разрядов слагаемых. На выходе одного из сум;- аторов по модулю два формируется значение соответствующего разряда результата. Блок 3 содержит т+1 вычитателей. Блоки 4 li 5 - по m сумматоров. Аргументы xj поступают с соответствующими разрядными сдвигами на входы блоков 4 и 5. Разрядные срезы аргументов у поступают на входы стробирования соответствующих сла- raet fl.ix и вычитаемых в блоках 4, 3 соответствующего разрядного вычислителя. 4 ил. с iS (Л ю 00 со sl со

| Стасюк А.И | |||

| Организация быстродействующих вычислителей на основе обратных разрядных операторов, Киев, 1983 (Препринт/АН УССР, электродинамики, № 326) | |||

| Стасюк А.И | |||

| Однородные многофункг циональные матричные процессоры | |||

| Киев, 1983, с | |||

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1987-01-15—Публикация

1985-03-27—Подача