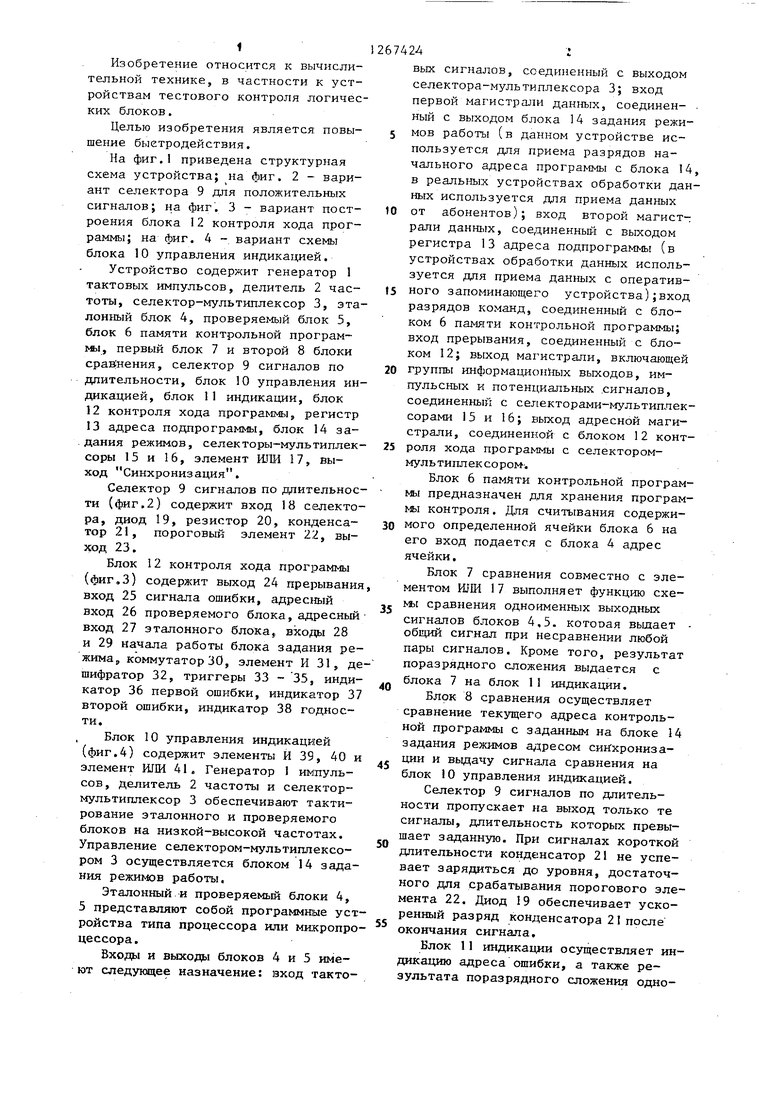

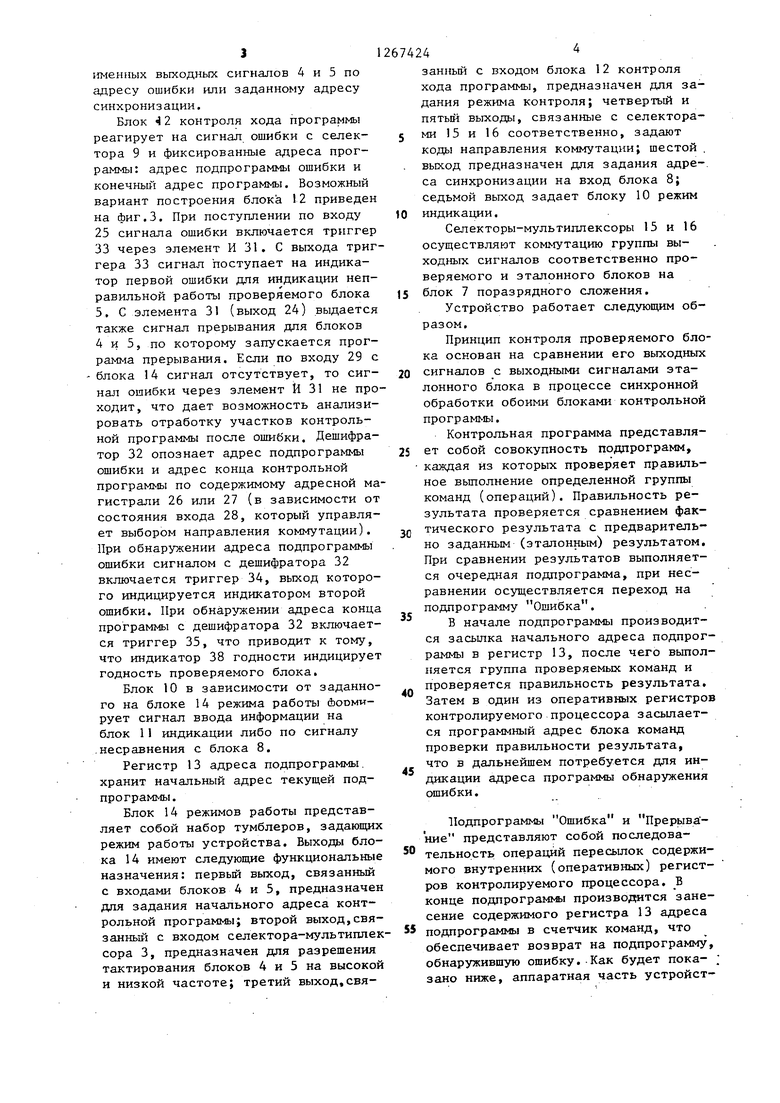

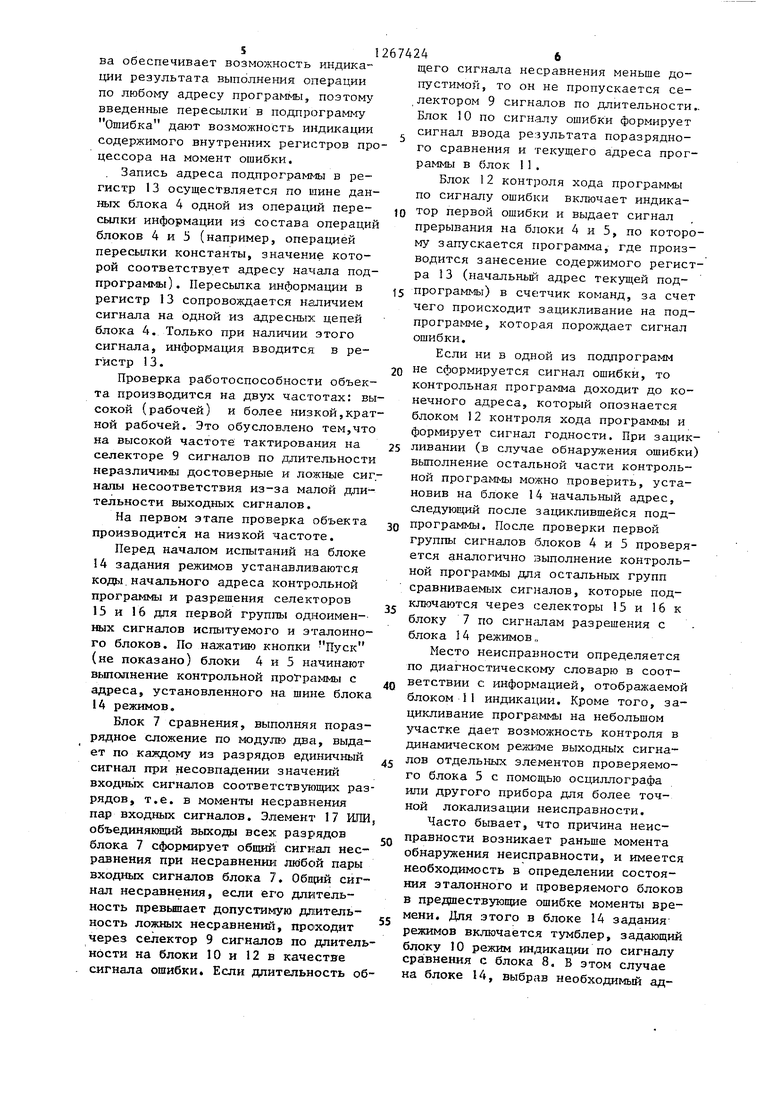

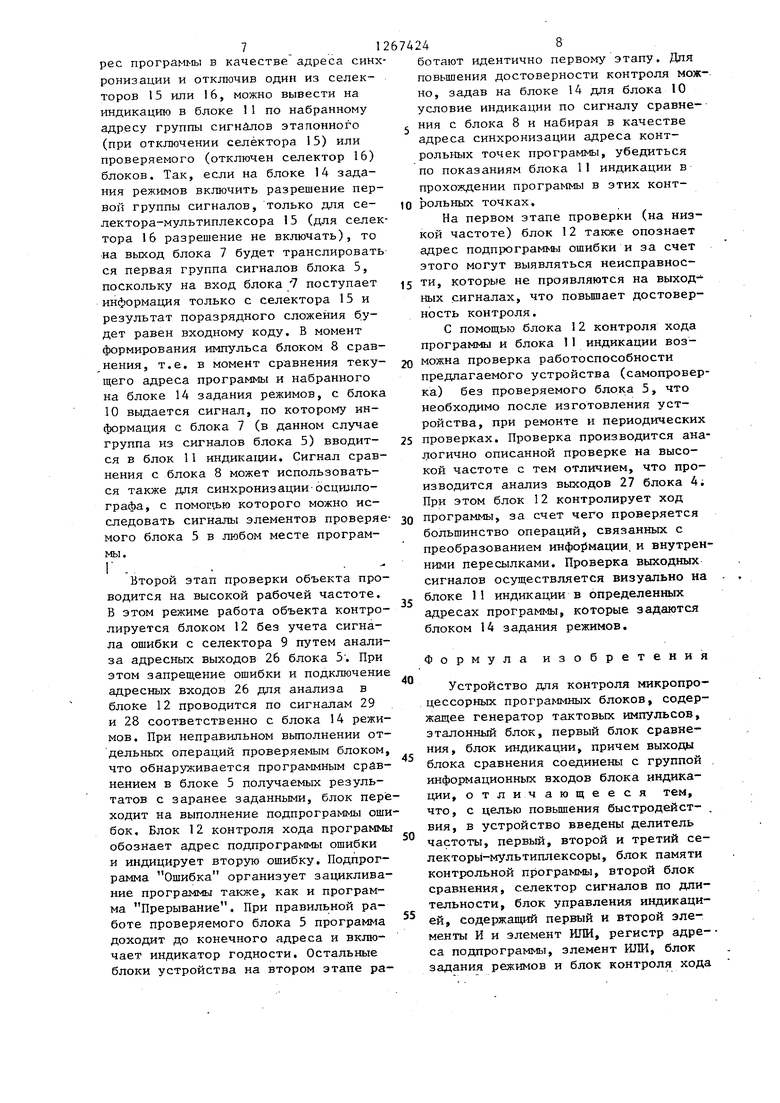

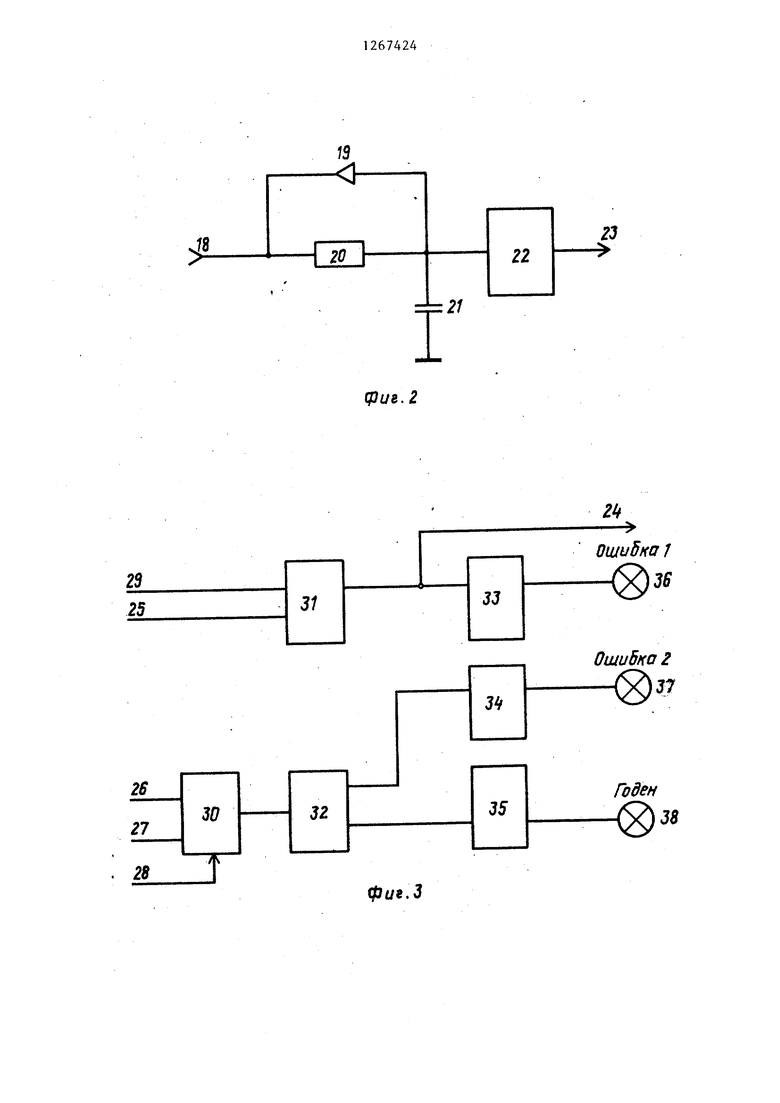

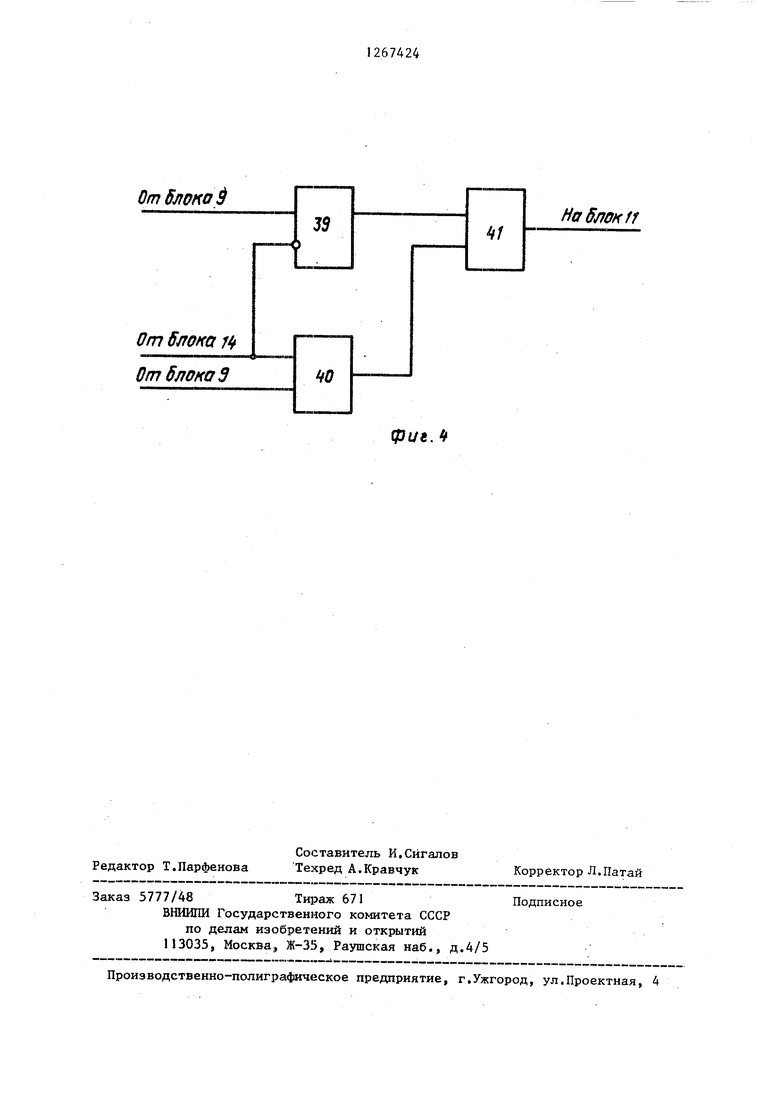

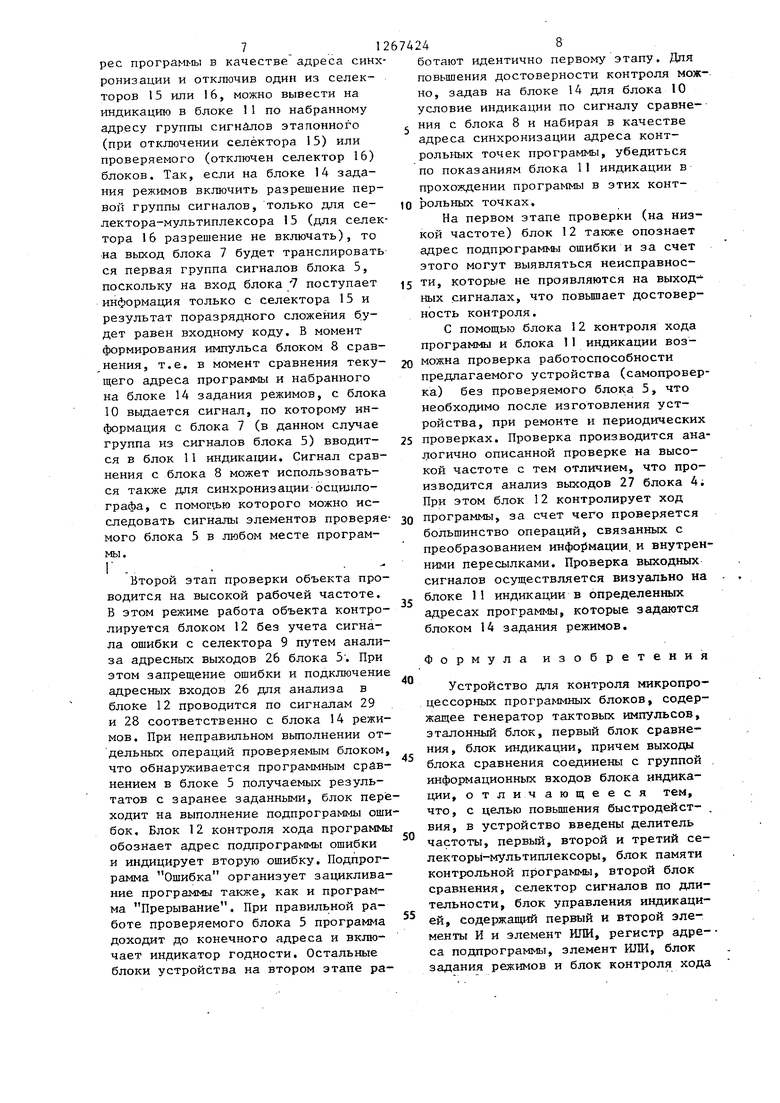

1 Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля логических блоков. Целью изобретения является повышение быстродействия. На фиг.1 приведена структурная схема устройства; на Лиг. 2 - вариант селектора 9 для положительных сигналов; на фиг. 3 - вариант построения блока 12 контроля хода программы; на фиг. 4 - вариант схемы блока 10 управления индикацией. Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, селектор-мультиплексор 3, эталонный блок 4, проверяемый блок 5, блок 6 памяти контрольной програм1 1, первый блок 7 и второй 8 блоки сравнения, селектор 9 сигналов по дпительности, блок 10 управления ин дика:цией, блок 11 индикации, блок 12контроля хода программы, регистр 13адреса подпрограммы, блок 14 за. Дания режим ов, селекторы-мультиплек соры 15 и 16, элемент ШШ 17, выход Синхронизация. Селектор 9 сигналов по длительнос ти (фиг.2) содержит вход 18 Свлекто ра, диод 19, резистор 20, конденсатор 21, пороговый элемент 22, выход 23. Блок 12 контроля хода программы (фиг.З) содержит выход 24 прерывани вход 25 сигнала ошибки, адресный вход 26 проверяемого блока, адресный вход 27 эталонного блока, входа 28 и 29 начала работы блока задания ре жима5, коммутатор 30, элемент И 31, д шифратор 32, триггеры 33 - 35, инди катор 36 первой ошибки, индикатор 3 второй ошибки, индикатор 38 годности. Блок 10 управления индикацией (фиг,4) содержит элементы И 39, 40 элемент ИЛИ 41. Генератор 1 импульсов, делитель 2 частоты и селектормультиплексор 3 обеспечивают тактирование эталонного и проверяемого блоков на низкой-высокой частотах. Управление селектором-мультиплексором 3 осуществляется блоком 14 зада ния режимов работы. Эталонный и проверяемый блоки 4, 5 представляют собой программные ус ройства типа процессора или микропр цессора. Входы и выходы блоков 4 и 5 имеют следукндее назначение: вход такто 4: вых сигналов, соединенный с выходом селектора-мультиплексора 3; вход первой магистрали данных, соединен- . ный с выходом блока 14 задания режимов работы (в данном устройстве используется для приема разрядов начального адреса программы с блока 14, в реальных устройствах обработки данных используется для приема данных от абонентов); вход второй магистрали данных, соединенный с выходом регистра 13 адреса подпрограммы (в устройствах обработки данных используется для приема данных с оперативного запоминающего устройства);вход разрядов команд, соединенный с блоком 6 памяти контрольной программы; вход прерывания, соединенный с блоком 12; выход магистрали, включающей группы информационных выходов, импульсных и потенциальных .сигналов, соединенный с селекторами-мультиплексорами 15 и 16; выход адресной магистрали, соединенной с блоком 12 контроля хода программы с селектороммультиплексором-. Блок 6 памяти контрольной програм ы предназначен для хранения програм№1 контроля, Для считывания содержимого определенной ячейки блока 6 на его вход подается с блока 4 адрес ячейки. Блок 7 сравнения совместно с элементом ШШ 1 7 выполняет функцию схеМЫ сравнения одноименнь1х выходных сигналов блоков 4,5. котооая вьщает общий сигнал при несравнении любой пары сигна.пов. Кроме того, результат поразрядного сложения выдается с блока 7 на блок 11 индикации. Блок 8 сравнения осуществляет сравнение текущего адреса контрольной программы с заданным на блоке 14 задания режимов адресом сиЯхронизацни и выдачу сигнала сравнения на блок 10 управления индикацией. Селектор 9 сигналов по длительности пропускает на выход только те сигналы, дх1ительность которых превышает заданную. При сигналах короткой дпительности конденсатор 21 не успевает зарядиться до уровня, достаточного для срабатывания порогового элемента 22. Диод 19 обеспечивает ускоренный разряд конденсатора 21 после окончания сигнала. Блок 11 индикации осуществляет индикацию адреса ошибки, а также результата поразрядного сложения одно3 выходных сигналов 4 и 5 по адресу ошибки или заданному адресу синхронна ации. Блок 42 контроля хода программы реагирует на сигнал ошибки с селектора 9 и фиксированные адреса программы: адрес подпрограммы ошибки и конечный адрес программы. Возможный вариант построения блока 12 приведен на фиг,3. При поступлении по входу 25 сигнала ошибки включается триггер 33 через элемент И 31. С выхода триг гера 33 сигнал поступает на индикатор первой ошибки для индикации неправильной работы проверяемого блока 5, С элемента 31 (выход 24) выдается также сигнал прерывания для блоков 4 и 5, по которому запускается программа прерывания. Если по входу 29 с блока 14 сигнал отсутствует, то сигнал ошибки через элемент И 31 не про ходит, что дает возможность анализировать отработку участков контрольной программы после ошибки. Дешифратор 32 опознает адрес подпрограммы ошибки и адрес конца контрольной программы по содержимому адресной ма гистрали 26 или 27 (в зависимости от состояния входа 28, который управляет выбором направления коммутации). При обнаружении адреса подпрограммы ошибки сигналом с дешифратора 32 включается триггер 34, выход которого индицируется индикатором второй ошибки. При обнаружении адреса конца программы с дешифратора 32 включается триггер 35, что приводит к тому, что индикатор 38 годности индицирует годность проверяемого блока. Блок 10 в зависимости от заданного на блоке 14 режима работы UOOMWрует сигнал ввода информации на блок 11 индикации либо по сигналу .несравнения с блока 8. Регистр 13 адреса подпрограммы. хранит начальный адрес текущей подпрограммы. Блок 14 режимов работы представляет собой набор тумблеров, задающих режим работы устройства. Выходы блока 14 имеют следующие функциональные назначения: первьй выход, связанный с входами блоков 4 и 5, предназначен дпя задания начального адреса контрольной программы; второй выход,связанный с входом селектора-мультиплек сора 3, предназначен для разрешения тактирования блоков 4 и 5 на высокой и низкой частоте; третий выход,свя24занный с входом блока 12 контроля хода программы, предназначен для задания режима контроля; четвертый и пятый выходы, связанные с селекторами 15 и 16 соответственно, задают коды направления коммутации; шестой , выход предназначен для задания адре-. са синхронизации на вход блока 8; седьмой выход задает блоку 10 режим индикации. Селекторы-мультиплексоры 15 и 16 осуществляют коммутацию группы выходных сигналов соответственно проверяемого и эталонного блоков на блок 7 поразрядного сложения. Устройство работает следующим образом. Принцип контроля проверяемого блока основан на сравнении его выходных сигналов с выходными сигналами эталонного блока в процессе синхронной обработки обоими блоками контрольной программы. Контрольная программа представляет собой совокупность подпрограмм, каждая из которых проверяет правильное выполнение определенной группы команд (операций). Правильность результата проверяется сравнением фак- тического результата с предварительно заданным (эталонным) результатом. При сравнении результатов выполняется очередная подпрограмма, при несравнении осуществляется переход на подпрограмму Ошибка. В начале подпрограммы производится засылка начального адреса подпрограммы в регистр 13, после чего выполняется группа проверяемых команд и проверяется правильность результата. Затем в один из оперативных регистров контролируемого процессора засылается программный адрес блока команд проверки правильности результата, что в дальнейшем потребуется для индикации адреса программы обнаружения ошибки. Подпрограммы Ошибка и Прерывание представляют собой последовательность. операций пересылок содержимого внутренних (оперативных) регистров контролируемого процессора. В конце подпрограмьы производится занесение содержимого регистра 13 адреса подпрограммы в счетчик команд, что обеспечивает возврат на подпрограмму, обнаружившую ошибку. Как будет пока- ; зано ниже, аппаратная часть устройства обеспечивает возможность индикации результата выполнения операции по любому адресу программы, поэтому введенные пересылки в подпрограмму Ошибка дают возможность индикации содержимого внутренних регистров процессора на момент ошибки.

Запись адреса подпрограмгЫ в регистр 13 осуществляется по шине данных блока 4 одной из операций пересыпки информации из состава операций блоков 4 и 5 (например, операцией пересылки константы, значение которой соответствует адресу начала подпрограммы). Пересылка информации в регистр 13 сопровождается нгшичием сигнала на одной из адресных цепей блока 4. Только при наличии этого сигнала, информаи 1я вводится в регистр 13.

Проверка работоспособности объекта производится на двух частотах: высокой (рабочей) и более низкой,кратной рабочей. Это обусловлено тем,что на высокой частоте тактирования на селекторе 9 сигналов по длительности неразличимы достоверные и ложные сигналы несоответствия из-за малой длительности выходных сигналов.

На первом этапе проверка объекта производится на низкой частоте.

Перед началом испытаний на блоке

14задания режимов устанавливаются коды.начального адреса контрольной программы и разрешения селекторов

15и 16 для первой группы одноименных сигналов испытуемого и эталонного блоков. По нажатию кнопки Пуск (не показано) блоки 4 и 5 начинают выполнение контрольной программы с адреса, установленного на шине блока 14 режимов.

Блок 7 сравнения, выполняя поразрядное сложение по модулю два, выдает по каждому из разрядов единичный сигнал при несовпадении значений входньпс сигналов соответствующих разрядов, т.е. в моменты несравнения пар входных сигналов. Элемент 17 ИЛИ объединякяций выходы всех разрядов блока 7 сформирует общий сигнал несравнения при несравнении любой пары входных сигналов блока 7, Общий сигнал несравнения, если его длительность превьшает допустимую диительность ложных несравнений, проходит через селектор 9 сигналов по длительности на блоки 10 и 12 в качестве сигнала ошибки. Если длительность общего сигнала несравнения меньше допустимой, то он не пропускается се, лектором 9 сигналов по длительности.. Блок 10 по сигналу ошибки формирует сигнал ввода результата поразрядного сравнения и текущего адреса программы в блок 11.

Блок 12 контроля хода программы по сигналу ошибки включает индикатор первой ошибки и выдает сигнал

0 прерывания на блоки 4 и 5, по которому запускается программа, где производится занесение содержимого регистра 13 (начальный адрес текущей подпрограммы) в счетчик команд, за счет

5 чего происходит зацикливание на подпрограмме, которая порождает сигнал ошибки.

Если ни в одной из подпрограмм не сформируется сигнал ошибки, то

0 контрольная программа доходит до конечного а,дреса, который опознается блоком 12 контроля хода программы и формирует сигнал годности. При зацикливании (в случае обнаружения ошибки) выполнение остальной части контрольной программы можно проверить, установив на блоке 14 начальный адрес, следующий после зациклившейся подпрограммы. После проверки первой группы сигналов блоков 4 и 5 проверяется аналогично выполнение контрольной программы для остальных групп сравниваемых сигналов, которые подключаются через селекторы 15 и 16 к блоку 7 по сигн;шам разрешения с блока 14 режимов„

Место неисправности определяется по диагностическому словарю в соответствии с информацией, отображаемой блоком 1I индикации. Кроме того, зацикливание программы на небольшом участке дает возможность контроля в динамическом режкие выходных сигналов отдельных элементов проверяемого блока 5 с помощью осциллографа или другого прибора для более точной локализации неисправности.

Часто бывает, что причина неисправности возникает раньше момента обнаружения неисправности, и имеется необходимость в определении состояния эталонного и проверяемого блоков в предшествующие ошибке моменты времени. Для этого в блоке 14 задания режимов включается тумблер, задающий блоку 10 режим индикации по сигналу сравнения с блока 8. В этом случае на блоке 14, выбрав необходимый ад7pec программы в качестве адреса синх ронизации и отключив один из селекторов 15 или 16, можно вывести на индикацию в блоке 11 по набранному адресу группы сигналов этапонного (при отключении селектора 15) или проверяемого (отключен селектор 16) блоков. Так, если на блоке 14 задания режимов включить разрешение первой группы сигналов, только для селектора-мультиплексора 15 (для селек тора 16 разрешение не включать), то на выход блока 7 будет транслировать ся первая группа сигналов блока 5, поскольку на вход блока 7 поступает информация только с селектора 15 и результат поразрядного сложения б.удет равен входному коду, В момент формирования импульса блоком 8 сравнения, т.е. в момент сравнения текущего адреса программы и набранного на блоке 14 задания режимов, с блока 10 выдается сигнал, по которому информация с блока 7 (в данном случае группа из сигналов блока 5) вводится в блок I1 индика1щи. Сигнал сравнения с блока 8 может использоваться также для синхронизации-осциллографа, с помопгью которого можно исследовать сигналы элементов проверяе мого блока 5 в любом месте программы. Г . .. Второй этап проверки объекта проводится на высокой рабочей частоте. В этом режиме работа объекта контролируется блоком 12 без учета сигнала ошибки с селектора 9 путем анализа адресных выходов 26 блока 5; При этом запрещение ошибки и подключение адресных входов 26 для анализа в блоке 12 проводится по сигналам 29 и 28 соответственно с блока 14 режимов. При неправильном вьтолнении отдельных операций проверяемым блоком что обнаруживается программным сравнением в блоке 5 получаемых результатов с заранее заданными, блок пере ходит на выполнение подпрограммы оши бок. Блок 12 контроля хода программы обознает адрес подпрограммы ошибки и индицирует вторую ошибку. Подпрограмма Ошибка организует зацикливание программы также, как и программа Прерывание, При правильной работе проверяемого блока 5 программа доходит до конечного адреса и включает индикатор годности. Остальные блоки устройства на втором этапе ра248ботают идентично первому этапу. Для повьш1ения достоверности контроля можно, задав на блоке 14 для блока 10 условие индикации по сигналу сравне- ния с блока 8 и набирая в качестве адреса синхронизации адреса контрольных точек программы, убедиться по показаниям блока 11 индикации в прохождении программы в этих контрольных точках. На первом этапе проверки (на низкой частоте) блок 12 также опознает адрес подпрограммы ошибки и за счет этого могут выявляться неисправности, которые не проявляются на выходных сигналах, что повышает достоверность контроля. С помощью блока I2 контроля хода программы и блока 11 индикации возможна проверка работоспособности предлагаемого устройства (самопроверка) без проверяемого блока 5, что необходимо после изготовления устройства, при ремонте и периодических проверках. Проверка производится аналогично описанной проверке на высокой частоте с тем отличием, что производится анализ выходов 27 блока 4; При этом блок 12 контролирует ход программы, за счет чего проверяется большинство операций, связанных с преобразованием инфо15мации. и внутренними пересылками. Проверка выходных сигналов осуществляется визуально на блоке 11 индикации в определенных адресах программы, которые задаются блоком 14 задания режимов. Формула изобретения Устройство для контроля микропроцессорных программных блоков, содержащее генератор тактовых импульсов, эталонный блок, первый блок сравнения, блок индикации, причем выхода блока сравнения соединены с группой . информационных входов блока индикации, отличающееся тем, что, с целью повьшения быстродействия, в устройство введены делитель частоты, первый, второй и третий селекторы-мультиплексоры, блок памяти контрольной программы, второй блок сравнения, селектор сигналов по длительности, блок управления индикацией, содержащий первый и второй элементы И и элемент ИЛИ, регистр адре- са подпрограммы, элемент ИЛИ, блок задания режимов и блок контроля хода программы, причем выход генератора тактовых импульсов соединен с первым Ш1формационным входом и через делитель частоты - с вторым информационным входом первого селектора-мультиплексора, выход которого соединен с тактовыми входами эталонного и прове ряемого блоков, выход начгшьного адреса программы блока задания режимов соединен с входами установки начального адреса эталонного и проверяемого блоков, выход начала работы блока задания режимов соединен с управляющим входом первого селектора-1чультиплексора, информапионный и адресный выходы проверяемого блока соединены соответственно с первым и вторым информационными входами второго селектора-мультиплексора, выход которого соединен с первым входом первого бло ка сравнения, адресный и информацион ный выходы эталонного блока соединеш. соответственно с первым и вторым информационными входами третьего селектора-мультиплексора, выход которо го соединен с вторым входом первого блока сравнения, адресный выход эталонного блока соединен с входом записи регистра адреса подпрограммы, с первым входом второго блока сравнения, с первым ин формационным входом блоко индикации и с адресным входом блока памяти контрольной программы, выход которого соединен с входами команд эталонного и проверяемого блоков,, информационный выход эталонного блока соединен с информационным входом регист ра адреса подпрограммы, информационный выход которого соединен с адресными входами эталонного и проЕ1еряемо г6 блоков, первый и второй вых.оды оп ределения направления коммутац;ии блока задания режимов соединены с первыми управляющими входами второго и третьего селекторов-мультиплексоров соответственно, адресный выход и выход разрешения индикации блока заданий режимов соединень соответственно с вторым входом второго блока сравнения и с первым входом первого элемента И и с инверсным входом второго элемента И блока управления индикацией, выход элемента ИЛИ блока управления индикацией соединен с управляющим входом блока индикации, выход второго блока сравнения соединен с вторым входом первого элемента И блока управления индикацией и является выходом ошибки устройства,выт ходы первого блока сравнения соединены с входами элемента ШШ, выход которого через сепектор сигналов по длительности соединен с прямым входом второго элемента И блока управления индшсацией, выходы первого и второго элементов И блока управления индикацией соединены с входами элемента ШШ, блок контроля хода програм содержит коммутатор, элемент И, дешифратор, первый, второй и третий триггеры, индикатор первой ошибки, индикатор второй ошибки и индикатор годности, причем выход начала работы блока задания режимов соединен с первым входом элемента И и с управляющим входом коммутатора, выход которого соединен с входом дешифратора, первый и второй выходы которого соединены с единичными входами соответственно первого и второго триггеровэ выход элемента И соеди нен с единичным входом третьего триггера блока контроля хода програмт г, входами прерывания эталонного и проверяемого блоков, адресные выходы эталонного и проверяемого блоков соединены соответственно с первьм и вторым информационными входами коммутатора блока контроля хода программы, выхо,цы первого, второго и третьего триггеров блока контроля кода программы соединены соответственно с индикатором годности, входом индикатора первой ошибки, входом индикатора второй ошибки, выход селектора сигналов по длительности соединен с вторым входом: элемента И блока контроля хода программы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1783545A1 |

| Устройство для контроля электрических соединений | 1988 |

|

SU1619310A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля логических блоков. Целью изобретения является поввшение быстродействия.Устройство содержит генератор тактовых импульсов 1, делитель 2 частоты, селектор-мультиплексор 3, эталонный блок 4, проверяемый блок 5, блок 6 памяти контрольной прюграммы, первый блок 7 сравнения, второй блок 8сравнения, селектор 9 сигналов по длительности, блок 10 управления индикацией, блок 11 индикации, блок 12 контроля хода программы, регистр 13 адреса подпрограммы, блок 14 задания режимов, два селектора-мультиплексора 15,16, элемент ИЛИ 17.4 ил. (Л с

J8

26

30

32

27

2J

22

2/

(риг. 2

Ошибка 2 |J7

J«

Годен

35

38

фи.З

От djfPKO§

33

От блока ify

О т блока 9

4G

Н а блок f г

1

(put. 4

| Устройство для контроля и диагностики цифровых блоков | 1976 |

|

SU605216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1983-03-30—Подача