1

Изобретение относится к вычислительной технике и может использоваться как системное устройство для связи цифровых вычислительных машин (ЦВМ) в многомашинном вычислительном комплексе

Наиболее близким к предлагаемому по технической сущности является адаптер канал-канал ЕС4060, состоящий из буферного регистра, входами и выходами подключенного к двум идентичным блокам связи с каналом, каждый из которых обслуживает канал, подключенный к нему через интерфейс ввода-вывода. Каждый блок связи с каналом содержит узел входных сигналов, регистр команд, дешифратор команд, регистр адреса, узел сравнения адресов, узел управления, узел выходных сигналов и регистр байта состояния },

Однако такое устройство обладает низкой разрешающей способностью диагностики и локализации неисправностей.

О его работоспособности можно судить только по результату передачи через него байтов данных и байтов состояния, которые после передачи их в ОЗУ доступны программе и оператору. Такая проверка не позволяет производить диагностику и локализацию неисправности с требуемой точностью.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что адаптер канал-канал, содержащий два полуадаптера, каждый из которых содержит регистр команд, дешифратор команд, регистр адреса, блок сравне10ния сщресов, блок управления, блок сопряжения с вычислительной машиной, регистр байта состояния, буферный регистр, блок синхронизации, причем информационный вход полуадаптера со15единен со входом регистра команд и первым входом блока сравнения адресов, второй вход которого подключен к выходу регистра адреса, а выход блока сравнения адресов соединен

20 с первым входе блока управления, второй вход котордго подключен к выходу дешифратора команду, выход которого подключен к .выходу регистра команд, управляющий вход полуадаптера

25 соединен с третьим входом блока управления, первый выход которого соединен с управляющим выходом полуадаптера, а второй, третий и четвертый выходы .блока управления соединены со30 ответственно с первым входом блока сопряжения с вычислительной машиной, первым входом буферного регистра и со входом регистра байта состояния, выход которого соединен со вторым входом блока сопряжения с вычислительной машиной, выход которого соединен с информационным выходом полуадаптера/ третий вход блока сопряжения с вычислительной машиной подключен к выходу регистра адреса, пятый выход блока управления первого прлуадаптера соединен с третьим входом блока управления второго полусждаптеpaj пятый выход блока управления вто- . рого полуадаптера соединен с третьим входом блока управления первого полуадаптера/ выход буферного регистра первого полуа аптера соединен с четвертым входом блока сопряжения с вычислительной машиной второго полуадаптера, а выход буферного регистра второго полуадаптера соединен с чет:-. вертым входом блока сопряжения с вычислительной машиной первого полу - адаптера, в каждый полуадаптер дополнительно введены коммутатор, блок фиксации переходов, блок передачи диагностической информации и элемент И, первый вход которого подключен к выходу блока синхронизации, а выход к пятому входу блока управления, шестой выход которого соединен с первым входом блока фиксации переходов, выход которого соединен со вторым вхоом элемента И и с первым входом блока передачи диагностической информации, второй и третий входы которого подключены соответственно к выходу дешифратора команд и к выходу блока синхронизации, первый, второй и третий выходы блрка передачи диагностической информации подключены соответственно к первому входу буферного регистра, ко второму входу блока фиксации переходов и к первому входу коммутатора, второй, третий и четвертый входы которого подключены соответственно к информационному входу полуадаптера, к первому и седьмому выхоам блока управления, выход коммутатора соединен со вторым входом буферного регистра, четвертый вход и четвертый выход блока передачи диагностической информации первого полуадаптера соединены соответственно с етвертым выходом и четвертым входом блока переда чи диагностической информации второго полуадаптера.

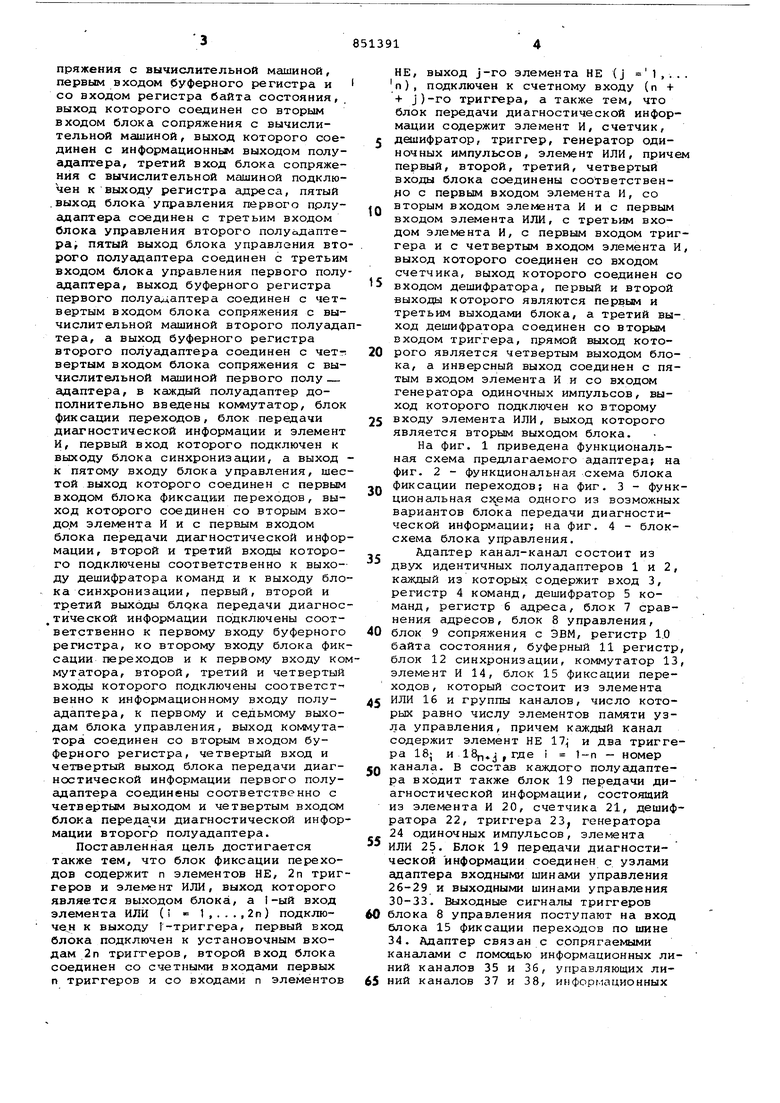

Поставленная цель достигается также тем, что блок фиксации перехоов содержит п элементов НЕ, 2п тригеров и элемент ИЛИ, выход которого вляется выходом блока, а 1-ый вход лемента ИЛИ ( 1 , . . . , 2п ) подклю4ejH к выходу 1-триггера, первый вход лока подключен к установочным вхоам 2 п триггеров, второй вход блока соединен со счетными входами первых п триггеров и со входами п элементов

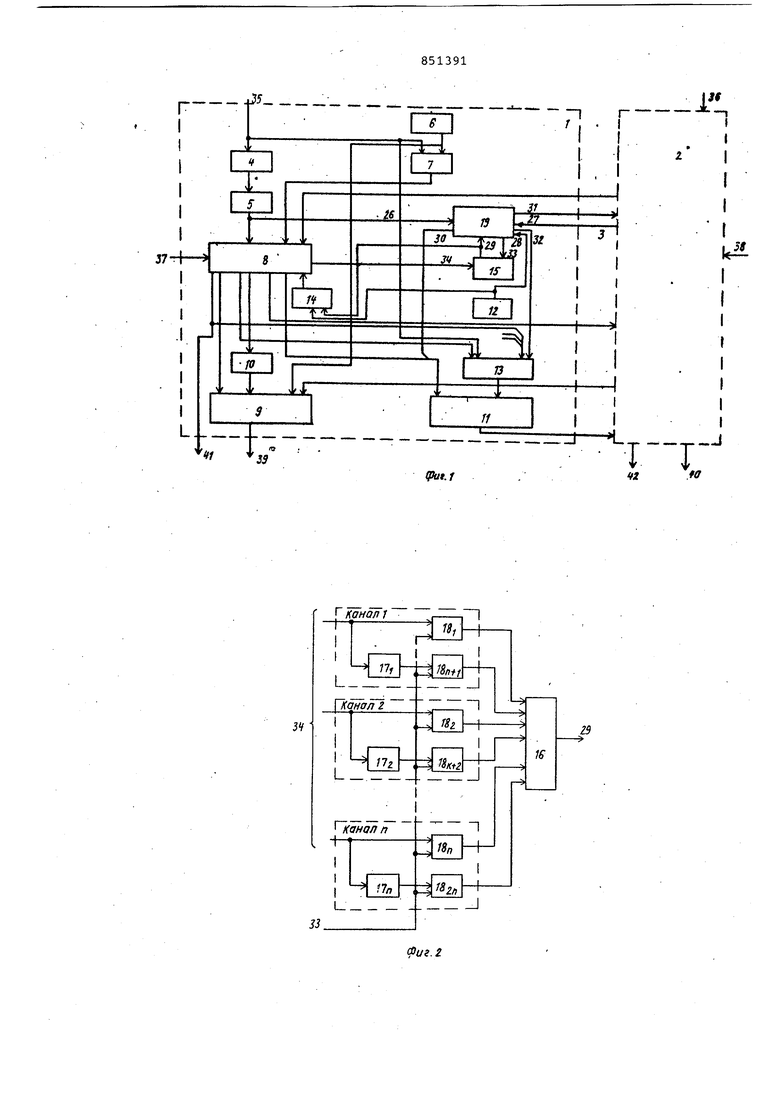

НЕ, ВЫХОД j-ro элемента НЕ (j ,.. п), подключен к счетному входу (п + + j)-го триггера, а также тем, что блок передачи диагностической информации содержит элемент И, счетчик, дешифратор, триггер, генератор одиночных импульсов, элемент ИЛИ, приче первый, второй, третий, четвертый входы блока соединены соответственно с первым входом элемента И, со вторым входом элемента И и с первым входом элемента ИЛИ, с третьим входом элемента И, с первым входом триггера и с четвертым входом элемента И выход которого соединен со входом счетчика, выход которого соединен со входом дешифратора, первый и второй выходы которого являются первым и третьим выходами блока, а третий выход дешифратора соединен со вторым входом триггера, прямой выход которого является четвертым выходом блока, а инверсный выход соединен с пятым входом элемента И и со входом генератора одиночных импульсов, выход которого подключен ко второму входу элемента ИЛИ, выход которого является вторым выходом блока.

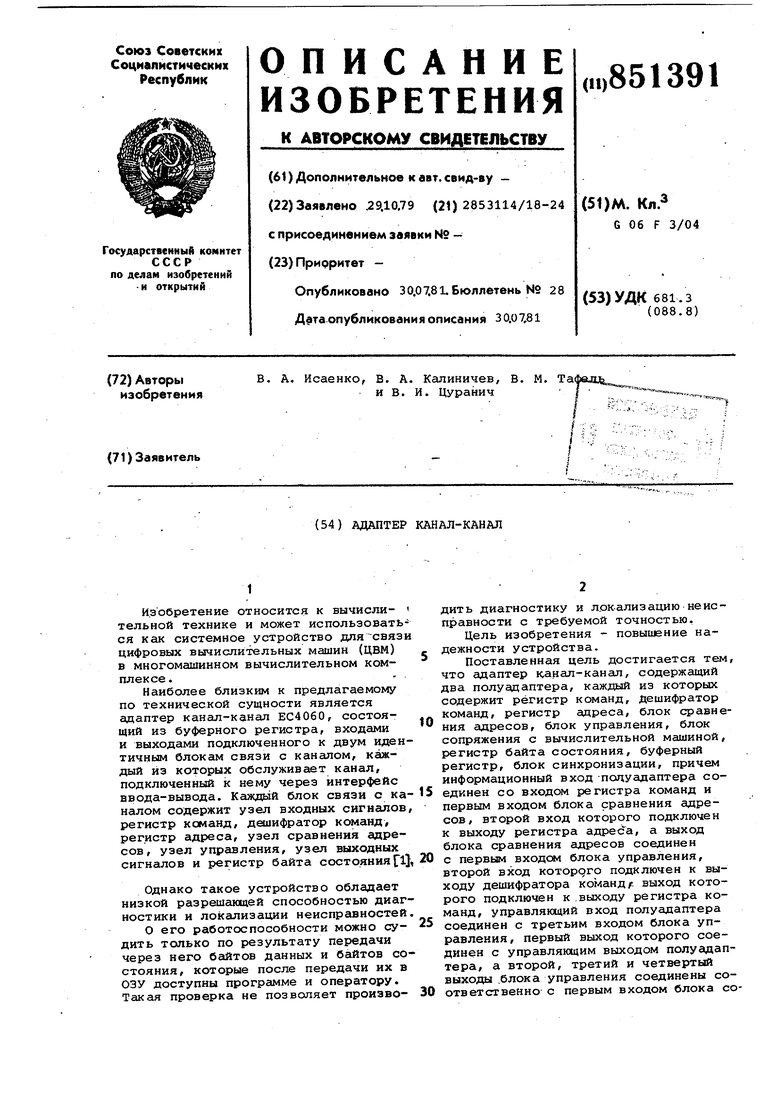

На фиг. 1 приведена функциональная схема предлагаемого адаптера; на фиг. 2 - функциональная схема блока фиксации переходов; на фиг. 3 - функциональная схема одного из возможных вариантов блока передачи диагностической информации; на фиг. 4 - блоксхема блока управления.

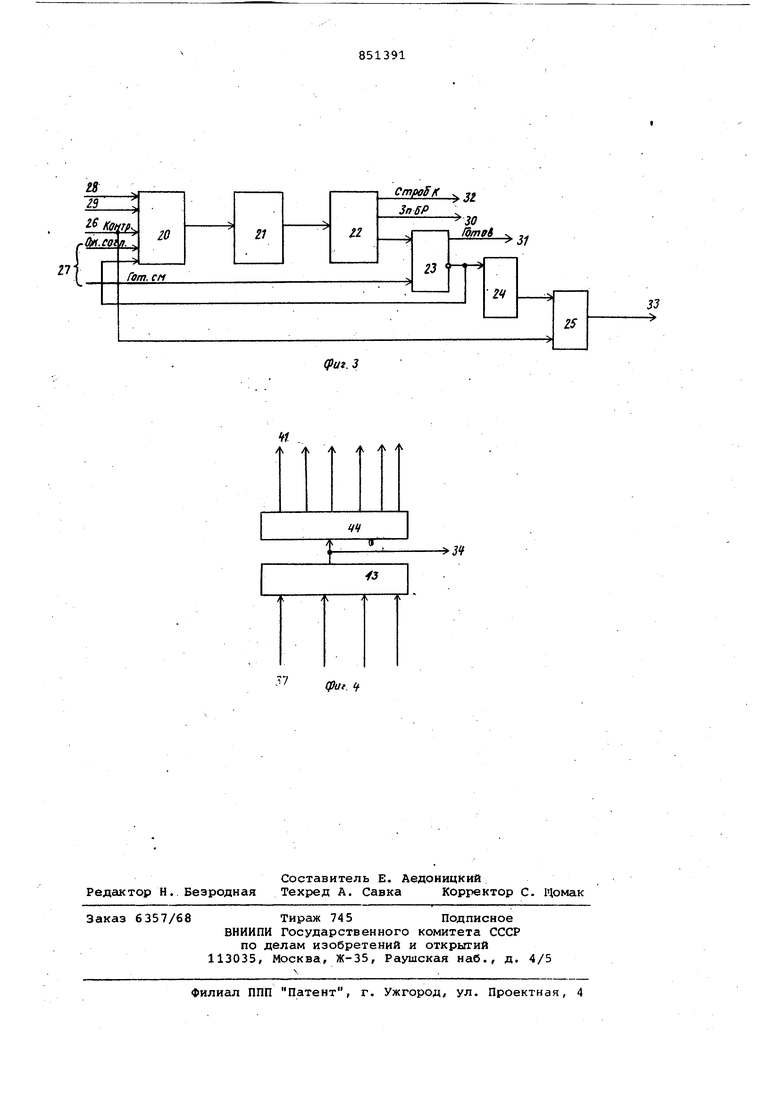

Адаптер канал-канал состоит из двух идентичных полуадаптеров 1 и 2, каждый из которых содержит вход 3, регистр 4 команд, дешифратор 5 команд, регистр 6 адреса, блок 7 сравнения адресов, блок 8 управления, блок 9 сопряжения с ЭВМ, регистр 1.0 байта состояния, буферный 11 регистр блок 12 синхронизации, коммутатор 13 элемент И 14, блок 15 фиксации переходов, который состоит из элемента ИЛИ 16 и группы каналов, число которых равно числу элементов памяти узла управления, причем каждый канал содержит элемент НЕ и два триггера 18 и 18р,|,где i 1-п - номер канала. В состав каждого полуадаптера входит также блок 19 пе едачи диагностической информации, состоящий из элемента И 20, счетчика 21, дешифратора 22, триггера 23, генератора 24 одиночных импульсов, элемента ИЛИ 25. Блок 19 передачи диагностической информации соединен с узлами адаптера входными шинами управления 26-29 и выходными шинами управления 30-33. Выходные сигналы триггеров блока 8 управления поступают на вход блока 15 фиксации переходов по шине 34. Адаптер связан с сопрягаемыми каналами с помощью информационных линий каналов 35 и 36, управляющих линий каналов 37 и 38, информационных линий абонентов 39 и 40 и управляющи линий абонентов 41 и. 42. В адаптере канал-канал предусмотрено два режима работы: РАБОТА и КОНТРОЛЬ. Режим работы задается с помсицью указателя (разряда) в формате команды обмена. Если этот разряд равен нулю, команда выполняется в режиме РАБОТА, если единице - в режиме КОНТРОЛЬ. Блок управления (фиг. 4) , предста ляющий собой синхронный цифровой авт лaт, вырабатывает функциональные сиг налы, обеспечивающие работу адаптера в соответствии с заложенным алгоритмом и входными сигналами, поступагаци ми с выхода дешифратора 5 команд, блока 7 сравнения адресов, блока 8 управления другого полуадаптера и уп равляющими сигналами к анаша, поступа ющими по линиям 37 и 38. Блок 8 управления содержит, напри мер, счетчик 43 и дешифратор 44. Переход блока управления из одного состояния в другое происходит по фронту синхросигналов, вырабатываеки блоком 12. в режиме РАБОТА сигнал на шине 29 равен единице и синхросигналы поступают на вход блока 8 управле ния через элемент И 14. Сигналы со- . пряжения с другим-полуадаптером, фор мируемые блоком 8 управления на шине 28, поступают (кроме блока управлени другого попуадаптера) на вход блока 19 передачи диагностической информации другого полуадаптера. Однако в режиме РАБОТА блок 19 не реагирует на эти сигналы и не выдает выходных сигналов. В режиме КОНТРОЛЬ адаптер работает следующим образом. Канал (например, канал 1 при проверке второго полуадаптера) выбирает адаптер и вводит команду СЧИТАТЬ, после чего первый полуадаптер выдает сигнал ожидания согласования (ОЖ, СОГЛ) по шине 31 в блок 8 управления второго полуадаптера. По этому сигналу второй полуадаптер передается в канал 2 байт состояния с указателем ВНИМАНИЕ. При этом его блок 8 управления изменяет состояние, что приводит к записи единицы хотя бы в один из триггеров 18 блока 15. Пусть изменение состояния этих триггеров происходит по положительному фронту сигнала на счетном входе. Тогда состояние йервого триггера изменяется при переходе из нуля в единицу, а второго - из единицы в ноль сигнала на выходе соответствующего элемента памяти узла управления. Таким образо при любом изменении состояния блока 8 управления (состояния элементов памяти узла управления) на выходе элемента ИЛИ 16, вырабатывается сигнал, запрещающий прохождение синхроимпульсов через элемент И 14 и разрешающий прохождение синхросигналов на счетный вход счетчика 21 через элемент, И 20 (сигналы КОНТРОЛЬ и ОЖ СОГЛ на шинах 26 и 31 равны единице) . Счетчик 21представляет собой последовательный двоичный двухразрядный счетчик. В исходном состоянии счетчика 21 на выходах дешифратора 22 сигналы не вырабатываются. По положительному фронту сигнала на счетном входе счетчик/ 21 начинает изменять свои состояния. В первом и во втором состояниях вырабатывается сигнал на шине 32, разрешгиоадий прохождение диагностической .информации Через коммутатор 13 на вход буферного регистра. Во втором состоянии счетчика на шине 30 вырабатывается сигнал записи в буферный регистр 11, по которому диагностическая информация заносится в буферный регистр. В третьем состоянии счетчика вырабатывается сигнал, устанавливаюций в единицу триггер 23. Сигнал с прямого выхода этого триггера поступает в блок управления первого полуадаптера, по которому последний считывает информацию с буферного регистра второго (проверяемого) полуадаптера и передает ее в канал. Сигнал с инверсного выхода триггера 23 запрещает прохождение синхросигналов через элемент И 20. После окончания цикла передачи диагностической информации в канал второй полуадаптер выдает сигнал ГОТ СМ по шине 31, который сбрасывает триггер 23. По следующему синхросигналу счетчик 21 возвращается в исходное состояние. При переходе триггера из единицы в нуль на выходе генератора 24 одиночных импульсов вырабатывается сигнал, по которому сбрасываются триггеры блока фиксации переходов 15 и на шине 29 вырабатывается сигнал, разрешающий прохождение синхроимпульсов на вход блока управления контролируемого полуадаптера и запрещающий прохождение синхросигналов на вход счетчика 21. в режиме РАБОТА по сигналу КОНТРОЛЬ на шине 26 вырабатывается сигнал на вь1ходе элемента ИЛИ 25, удерживающий триггеры блока 15 в нулевом состоянии. Проверка первого полуадаптера производится аналогично. При этом канал 2 выбирает второй полуадаптер, вводят-команду СЧИТАТЬ, а в первом полуадаптере вводится команда, правильность выполнения которой необходимо пров ерит ь. На основании физического или программного моделирования составляется словарь неисправностей, в котором Ксокдой неисправности ставится в соответствие полученная от полуадаптера диагностическая информация. Предлагаемое устройство обеспечивает локализацию места неисправности с точностью до 2 сменных узлов и позволяет на 1-3 порядка по сравнению с известным сократить время поиска неисправностей. Формула изобретения 1. Адаптер канал-канал, содержащи два полуадаптера, каждый из которых содержит регистр команд, дешифратор команд, регистр адреса, блок сравнения адресов, блок управления, блок сопряжения с вычислительной машиной, регистр байта состояния, буферный регистр, блок синхронизации, причем информационный вход полуадаптера сое динен со входом регистра команд и первым входом блока сравнения адресов, второй вход которого подключен к выходу регистра адреса, а выход блока сравнения адресов соединен с первым входом блока управления, второй вход которого подключен к выходу дешифратора команд, выход которого подключен к выходу регистра комавд управлягаций вхсщ полуадаптера соединен с третьим входом блока управлени первый выход которого соединен с управляющим выходом .полуадаптера, а вт рой, третий и четвертый выходы блока управления соединены соответственно с первым входом блока сопряжения с вычислительной машиной, первым входо буферного регистра и со входом регистра байта состояния, выход которого соединен со вторым входом блока сопряжения с вычислительной машиной, выход которого соединен с информационным выходом полуадаптера, третий вход блока сопряжения с вычислительной машиной подключен к выходу регистра адреса, пятый выход блока управ ления первого полуадаптера соединен с третьим входом блока управления второго полуадаптера, пятый выход блока управления второго полуадаптера соединен с третьим входом блока управления первого полуадаптера, выход буферного регистра первого полуадаптера соединен с четвертым входом блока сопряжения с вычислительной машиной второго полуадаптера, а выход буферного регистра второго полуадаптера соединен с четвертым входом блока сопряжения с вычислительной машиной первого полуадаптера, отличающийся тем, что, с целью повышения надежности, в каждый полуадаптер введены коммутатор, блок фиксации переходов/ блок передачи диагностической информации и элемент И, первый вход которого подключен к выходу блока синхронизации/ а выход - к пятому входу блока управления, шестой выход которого соединен с первым входом блока фикеации переходов выход которого соединен со вторым входом элемента И и с первым входом блока передачи диагностической информации, второй и третий входы которого подключены соответственно к выходу дешифратора команд и к выходу блока синхронизации, первый, второй и третий выходы блока передачи диагностической информации подключены соответственно к первому входу буферного регистра, ко второму входу блока фиксации переходов и к первому входу коммутатора, второй, третий и четвертый входы которого подключены соответственно к инфо мационному входу полуадаптера, к первому и седьмоиу выходам блока управления, выход конадутатора соединен со вторым входом буферного регистра, четвертый вход и четвертый выход блока передачи диагностической информации первого полуадаптера соединены соответственно с четвертым выходом и четвертым входом блока передачи диагностической информации второго полуадаптера. 2.Устройство по п. 1, отличающееся тем, что блок фиксации переходов содержит п элементов НЕ, 2п триггеров и элемент ИЛИ, выход которого является выходом блока, а i-ый вход элемента ИЛИ (i 1,...п) подключен к выходу i-го триггера, первый вход блока подключен к установочным входам 2п триггеров, второй вход блока соединен со счетными входами первых п триггеров и со входами п элементов НЕ, выход j-ro элемента НЕ (j J,,..,n) подключен к счетному входу (п + j)-ro триггера. 3.Устройство по п. 1, отличающееся тем,- что блок передачи диагностической информации содержит элемент И, счетчик, дешифратор, триггер, генератор одиночных импульсов, элемент ИЛИ, причем первый, второй, третий, четвертый входы блока соединены соответственно с первым входом элемента И,, со вторым входом элемента И и с первым входом элемента ИЛИ, с третьим входом элемента И, с первым входом триггера и с четвертым входом элемента И, выход которого соединен, со входом дешифратора, первый и .второй выходы которого являются первым и третьим выходами блока/ а третий выход дешифратора соеди- . ней со вторым входом триггера, прямой выход которого является четвертым выходом блока/ а инверсный выход соединен с пятым входом элемента И и со входом генератора одиночных импульс6В| выход которого подключен ко второму входу элемента ИЛИ, выход которого является вторым выходом блока. Источники информации, принятые во внимание при экспертизе 1. Антонов В. С./Соловьев С. П. и др. Электронная вычислительная машина ЕС-1050, - Статистика, 1976, С. 185-190.

-

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Адаптер канал-канал | 1987 |

|

SU1425694A1 |

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

371

тю

М

ffut.l

г /(ОНО/ 1

Г-:п:

34

I - -я I

J 1

5

Псанал п

п

57

(pUl. if CmpoSK j

Авторы

Даты

1981-07-30—Публикация

1979-10-29—Подача