Изобретение относится к интегральной схемотехнике, в частности к биполярным интегральным схемам памяти.i

Известны формирователи сигнала адреса оперативного запоминающего устройства (ОЗУ), включающие в себя помимо тока хранения источник выборки, подсоединенный через развязывающие диоды к одной из двух адресных шин каждой строки элементов памяти (ЭП) и обеспечивающий ускоренное понижение уровня напряжения на адресных шинах по окончании цикла обращения к строке ЭП l.

Недостаток данных схем заключается либо в существенном замедлении процесса перевода строки ЭП в режим покоя начиная с момента достижения одинаковых уровней напряжения на адресных шинах ЭП, выбираемых в соседних циклах обращения, либо в недостаточной, энергетической эффективности и большой площади, занимаемой ими на кристалле.

Наиболее близкой к предлагаемой по технической сущности является схема, которая содержит шину управления, первую и вторую адресные тины, генератор тока хранения, первый вывод которого подсоединен ко второй адресной шине, а второй - к отрицательному полюсу источника питания, первый п-р-п-транзистор, коллектор которого подсоединен ко второй адресной шине, а эмиттер и база - к первым выводам соответственно пер вого и второго резисторов, вторые выводы которых соединены с от зицательным полюсом источника питания, второй п-р-п-транзистор, коллектор которого подсоединен к положительному полюсу источника питания, эмиттер - к базе первого транзистора, а база - к коллектору третьего п-р-птранзистора, база которого соединена с шиной управления, эмиттер с первым выводом третьего резистора, коллектор - с первыми выводами четвертого резистора и первого конденсатора, а шина управления, в свою очередь, - с положительным полюсом источника опорного напряжения, второй конденсатор, первый вывод которого подсоединен к базе первого транзистора, а второй - к отрицательному полюсу источника опорного напряжения. Вторые вывйды первого конденсатора и четвертого резистора подсоединены к положительному полюсу источника .питания, а зторой вывод третьего резистора -. к отрицательному полюсу источника питания 2.

-Недостатками известной схёмл являюгсг, потребление мощности в режиме покоя, что может приводить к существенному увеличению мощности, потребляемой большой интегральной схемой памяти, так как количество схем формирователя сигнала адреса ОЗУ рано количеству строк в матрице ЭП, а также значительная площадь, занимаемая схемой на кристалле, что связано с наличием в ней резиртивноемкостных цепей с большими постоянными времени, обуславливающими задеку выключения тока, форсирующего понижение потенциала на адресной шине строки ЭП, которая выбиралась в цикле , предшествующем текущему циклу обращения, величина постоянной времени RC-цепи контролируется номиналами резистора и конденсатора, выпоняемого обычно в интегральных схема в виде обратно смещенного р-п-перехода, которые пропорциональны площади соответствующих схемных элементов.

Цель изобретения - уменьшение мощности, потребляемой формирователем .

Поставленная цель достигается Тем, что формирователь адресного сигнала для оперативного запоминающего устройства, содержащий первый адресный транзистор, транзистор связи, второй адресный транзистор, источник тока, первый и второй резисторы, первый вывод источника тока соединен с первой адресной шиной и коллектором первого адресного транзистора, эмиттер которого подключен к первому выводу первого резистора, база первого адресного транзистора соединена с первым выводом второго .резистора, эмиттер транзистора связи соединен с первым выводом второго резистора, коллектор подключен к шине источника питания, база ТраМзи тора связи соединена с коллектором второго адресного транзистора, бад,а второго адресного, тразистора подключена к шине управления, а вторые выводы резисторов и источника тока подключены к- общей шине, содержит дополнительный источник тока, первый вывод которого соединен с шиной управления, а второй вывод подклю чен к общей шине, эмиттер второго адресного транзистора соединен со второй адресной шиной.

Эмиттер транзистора связи подключен к шине источника питания, а коллектор - к базе первого адресно1ГО транзистора-.

Коллектор транзистора связи подключен ко второй адресной шине.

Коллектор транзистора связи соединен с шиной управления.

Формирователь содержит дополнительный лсточник питания в виде резистора, первый вывод которого сбединен С шиной управления, а второй вывод - с общей шиной.

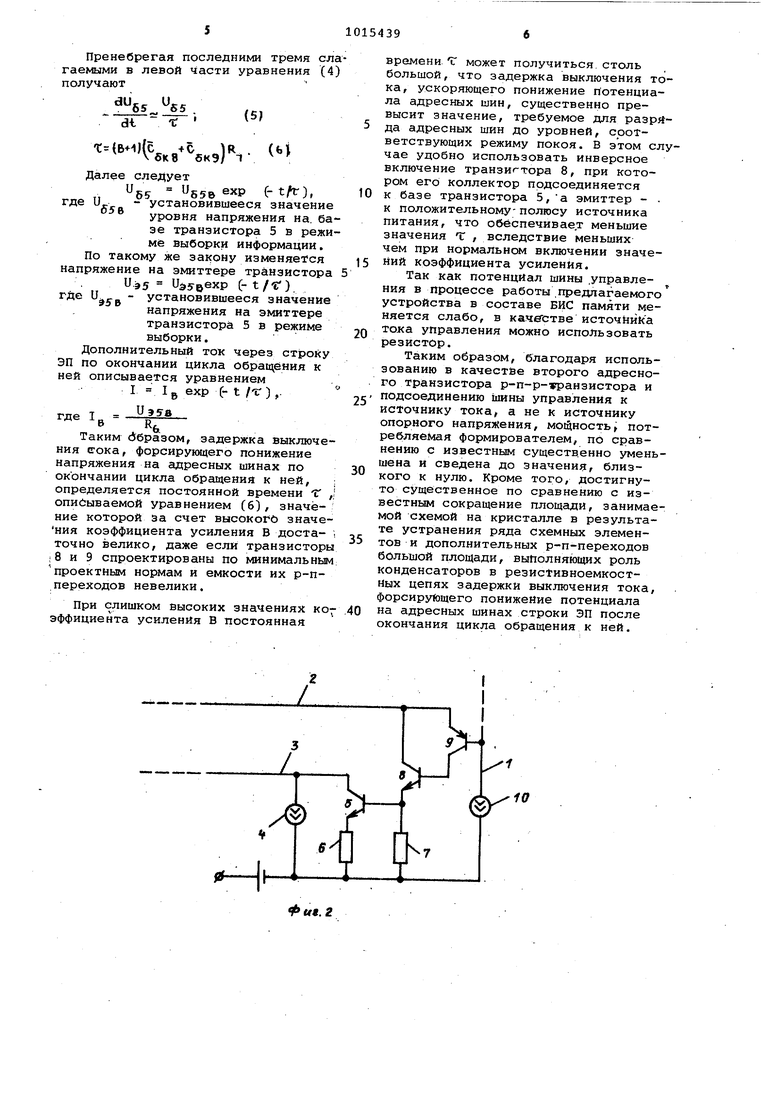

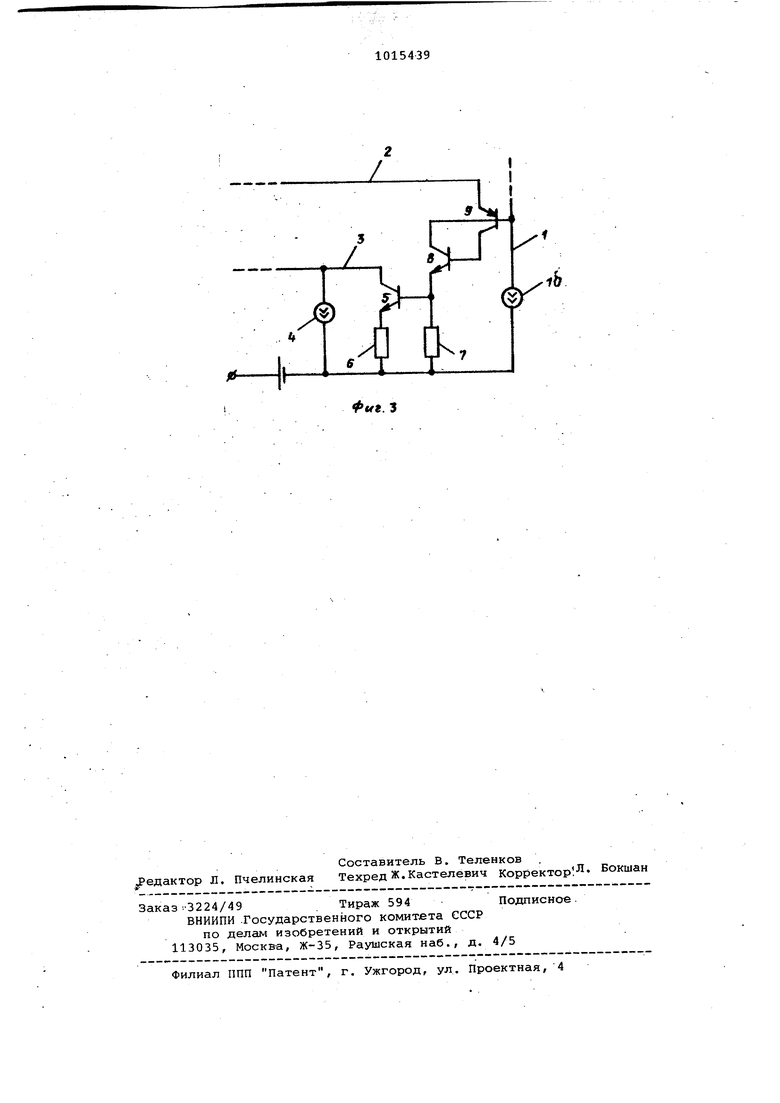

На фиг. 1 изображена электрическая схема устройства; на фиг, 2

и 3 - форлтройатели сигнала адреса ОЗУ.

Предлагаемая схема включает в себя шину 1 управления, первую 2 и вторую 3 адресные шины, основной источник 4 тока, первый вывод которого подсоединен ко второй адресной шине 3, а второй - к отрицательному полюсу источника питания, первый адресный транзистор 5, коллектор которого подсоединен ко второй адресной шине 3, а эмиттер и база к первым выводам соответственно первого б и второго 7 резисторов, вторые выводы которых соединены с отрицательным полюсом источника питания транзистор связи 8, коллектор которого подсоединен к положительному полюсу источника питания, эмиттер к базе.первого адресного транзистора 5, а база - к коллектору второго адресного транзистора 9, база которого, в свою очередь, соединена с I управления, эмиттер с первой адресной шиной 2, шина 9 управления через дополнительный источник 10 тока соединена с отрицательным полюсом источника питания.

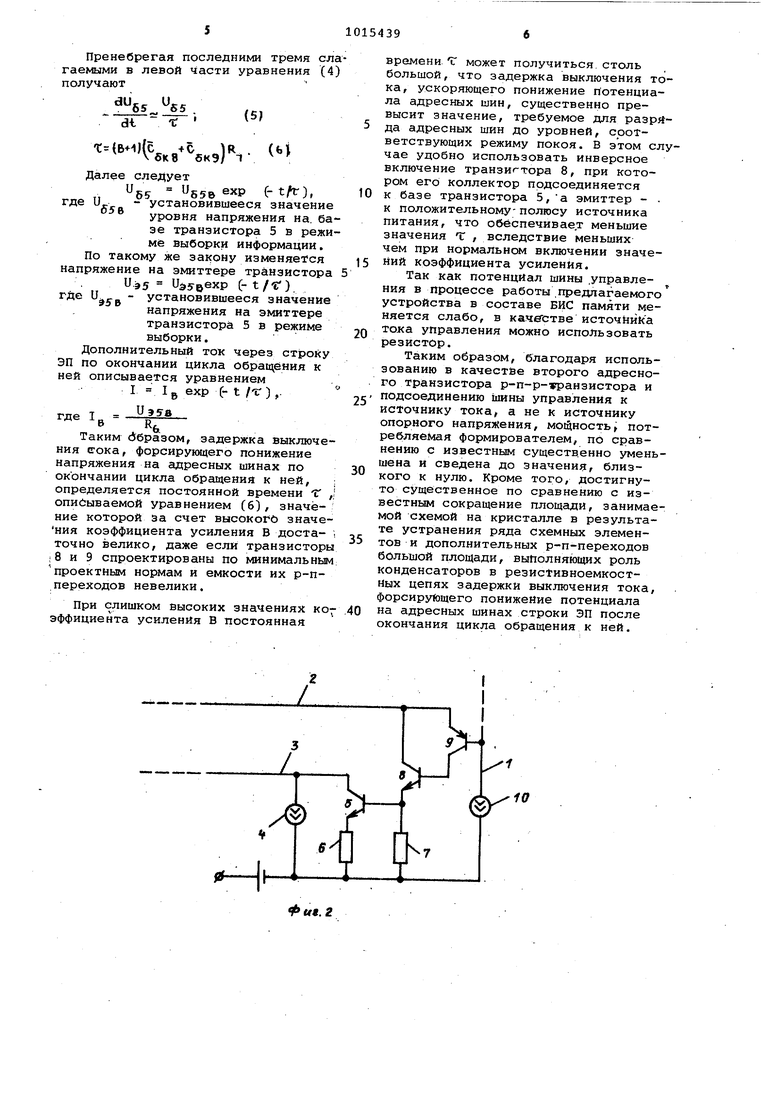

На фиг. 2 и 3 изображены формиг рователи сигнала адреса ОЗУ, в которых коллектор транзистора связи подсоединен соответственйо к первой адресной шине и к базе второго адресного транзистора.

Формирователь адресного сигнала ОЗУ работает следующим образом.

Скорость нарастания потенциалу на адресных шинах и 3. достаточно высока благодаря использованию эмиттерных повторителей .или усилителей Дарлингтона (не показаны). Для Д9стижения высокой скорости спа да уровня напряжения на адресных шинах 2 и 3 после окончания цикла обращения используется дополнительный ток, иротекаюпц й через строку ЭП в режиме выборки. Этот ток обеспечивается транзистором 5. При выборке строки, т.е. при повышении уровня напряжения . на адресных шинах 2 и |в данной строки, ток источника 10 тока через шину 1 управления, являющуюся общей для всех стро накопителя, -поступает в базу транзистора 9, что- приводит к повышению уровня напряжения на базах транзисторов 8 и 5, транзистор 5 переходит из режима отсечки в нормальный активный режим, увеличивая ток, протекгиощий через строку элементов памти (ие показаны), включенную между шинами 2 и 3.

При повышении поте.нциала на- адре ных тинах 2 и 3 строки, выбираемой в следующем цикле обращения, ток источника 10 тока начинает ответвляся в базу транзистора 9 данной строки. Однако дополнительный ток, протексцощий через строку ЭП, которая собиралась в предыдущем цикле обращения, выключается с задержкой, в результате чего сохраняется высокая скорость понижения уровня напряжения на адресных шинах 2 и 3 строку. Процесс изменения потенциа- ла на базах транзисторов 8 и 5 опи- сывается системой дифференциальных уравнений

%.с .

)

dt

и

$5

(1)

;(вИ)Каи,

58 IP

/г г j.r f -SselirV

;(«Г 1

ггде R-величина conpov явления резистора 7/

-усредненная емкость

RT резистора 7 f

6э5 SKS усредненные емкости соответственно эмиттерного и коллекторного и коллекторного -п-переходов тран зистора 5; Cg д, g- усредненные емкости соответственно эмиттерного и коллекторного р-п-переходов транзистора 8;

Cg д- усредненная емкос гь коллекторного р-пперехода транзистора 9; В - коэффициент усиления

транзистора8.

Так как узел, .к которому подключена база транзистора 8, разряжается лишь базовым током этого транг зистора, величина которого мала, скорость изменения напряжения в это узле определяет и скорость изменения напряжения на базе и эмиттере транзистора 5.

Таким образом.

3%.%

U)

at

at

Из уравнений (1), (2) и (3) получают

.С

) RlJ

dt

(} Пренебрегая последними тремя сл гаемыми в левой части уравнения (4 получают . di -С t(BH,(c.O)R. (bi Далее следует б 55В ехр C-tAr), где и - установившееся значение уровня напряжения на. ба зе транзистора 5 в режи ме выборки информации, По такому же закону изменяется напряжение на эмиттере транзистора и.э5 U55Bexp С- t/f). где - установившееся значение напряжения на эмиттере транзистора 5 в режиме выборки. Дополнительный ток через строку ЭП по окончании цикла Обращения к ней описывается уравнением I IP ехр (- t /Г),. Таким дбразом, задержка выключе ния «тока, форсирующего понижение напряжения на адресных шинах по окончании цикла обращений к ней, определяется постоянной времени Т описываемой уравнением (6, значение которой за счет высокох О значе ния коэффициента усиления В достаточно велико, даже если транзистор ;8 и 9 спроектированы по минимальны проектным нормам и емкости их р-ппереходов невелики. При слишком высоких значениях ко эффициента усиления В постоянная времени Т может получиться.столь большой, что задержка выключения тока, ускоряющего понижение потенциала адресных шин, существенно превысит значение, требуемое для разрйда адресных шин до уровней, соответствующих режиму покоя. В этом случае удобно использовать инверсное включение транзистора 8, при котором его коллектор подсоединяется к базе транзистора 5,а эмиттер - . к положительному-полюсу источника питания, что обёспечивае.т меньшие значения Т , вследствие меньших чем при нормальном включении значений коэффициента усиления. Так как потенциал шины управления в процессе работы предлагаемого устройства в составе БИС памяти меняется слабо, в каябстве источйиКа тока управления можно использовать резистор. Таким образом, благодаря использованию в качестве второго адресного транзистора р-п-р- ранзистора и подсоединению шины управления к источнику тока, а не к источнику опорного напряжения, мо1§ность потребляемая формирователем, по сравнению с известным существенно уменьшена и сведена до значения, близкого к нулю. Кроме того, достигнуто существенное по сравнению с известным сокращение площади, занимаемой схемой на кристалле в результате устранения ряда схемных элементов и дополнительных р-п-переходов большой площади, выполняющих роль конденсаторов в резис±ивноемкостных цепях задержки выключения тока, форсиру ощего понижение потенциала на адресных шинах строки ЭП после окончания цикла обращения к ней.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| Формирователь тока для магнитного запоминающего устройства | 1977 |

|

SU640366A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Формирователь двухполярного образцового напряжения | 1983 |

|

SU1115037A1 |

| Запоминающее устройство | 1983 |

|

SU1171849A1 |

| Управляемый стабилизатор тока,пРЕдНАзНАчЕННый для пиТАНия OT иС-ТОчНиКА ВХОдНОгО НАпРяжЕНия C НулЕ-ВОй ТОчКОй | 1978 |

|

SU802948A1 |

1. ФОРМИРОВАТЕЛЬ АДРЕСНОГО СИГНАЛА ДЛЯ ОПЕРАТИВНОГО ЗАПОМИНАЮ1ЧЕГО УСТРОЙСТВА, содержащий первый адресный транзистор, транзистор свя зи, второй адресный транзистор, источник тока, первый и второй резисторы, первый вывод источника тока соединен с первой адресной шиной и коллектором первого адресного транзистора, эмиттер которого подключен к первому выводу первого резистора, база первого адресного.транзистора соединена с первым выводом второго резистора, эмиттер транзистора связи соединен с первым выводом второго резистора, коллектор подключен к шине источника питания, база тран зистора связи соединена с коллектором второго адресного транзистора, база второго адресного транзистора подключена к шине управления, а вторые выводы резисторов и источника тока подключены к общей итне, отличающийся тем, что, с целью уменьшения потребляемой мощности формирователя, он ссщержит дополнительный источник тока, первый вывод которого соединен с шиной управления , а второй вывод подключен к общей шине, эмиттер второго адресного транзистора соединен с второй адресной шиной. 2.Формирователь ло п. 1, отличающийся тем, что эмиттер транзистора связи подключен к шине источника питания, а коллектор к базе первого адресного транзистора., 3.Формирователь по п. 1, о т ли ч ающийся тем, что коллектор транзистора связи подключен ко второй адресной шине. 4.Формирователь по п. 1, о тли чающийс я тем, что коллектор транзистора связи соединен с шиной управления. 5.Формирователь по пп. 1-4, отличающийся тем, что формирователь содержит дополнительнь1й источник питания в виде резистора, первый вывод которого соединен с шиной управления, а второй вывод с общей шиной. .

/

/©

5 we. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Не | |||

| Dev., 1979 6, с | |||

| Способ консервирования растений и трупов животных или их частей | 1921 |

|

SU886A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ISSCC Digest о Technical Papers, 1979, с | |||

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| . | |||

Авторы

Даты

1983-04-30—Публикация

1981-10-29—Подача