2

со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1988 |

|

SU1569901A1 |

| Формирователь адресного сигнала для оперативного запоминающего устройства | 1981 |

|

SU1015439A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

Изобретение относится к электронике и предназначено для использования в оперативных запоминающих устройствах на биполярных транзисторах. Целью изобретения является упрощение накопителя для запоминающего устройства Поставленная цель достигается тем, что вторые выводы источников 3 тока хранения соединены с первыми выводами резисторов 5 соответствующих токоог- раничительных элементов, вторые выводы которых объединены Повышенный ток через выбранный элемент 1 памяти обеспечивается соответствующий резистором 5, который отбирает часть тока резисторов 5 невыбранных элементов 1 памяти 1 ил.

uV vP ё3 5

: Г(

VJ ел

00 СП

Изобретение относится к электронике и предназначено для использования в оперативных запоминающих устройствах на биполярных транзисторах.

Известны накопители для оперативных запоминающих устройств, содержащие матрицу элементов памяти и источники тока хранения, обеспечивающие сохранность информации в невыбранных элементах памяти.

Недостатком указанных накопителей является низкая помехоустойчивость, обусловленная тем, что при выборке элементов памяти ток в них остается таким же, как в режиме хранения.

Наиболее близким к предлагаемому является накопитель для оперативного запоминающего устройства, содержащий матрицу элементов памяти, первые адресные шины которой являются входами выборки накопителя, элементы связи, каждый из которых состоит из транзистора и резистора, первый вывод которого соединен с коллектором транзистора, а второй подключен к шине питания устройства, эмиттеры транзисторов элементов связи подключены к соответствующим первым адресным шинам матрицы элементов памяти, а базы транзисторов элементов связи объединены и являются опорным входом устройства, формирователь задержки, состоящий из транзисторов и элементов памяти, первые адресные шины которых соединены с эмиттерами соответствующих транзисторов, базы транзисторов формирователя задержки соединены с коллекторами транзисторов соответствующих элементов связи, а кол- пекторы подключены к шине питания устройства, две группы источников тока хранения, первые выводы которых подключены к шине нулевого потенциала устройства, две группы токоограничительных элементов потенциала устройства, две группы токоограничительных элементов на резисторах, первые выводы резисторов токоограничительных элементов первой группы подключены к соответствующим вторым адресным шинам матрицы элементов памяти, а первые выводы резисторов токоограничительных элементов второй группы - к вторым адресным шинам соответствующих элементов памяти формирователя задержки, вторые выводы резисторов токоограничительных элементов соединены с вторыми выводами соответствующих источиков тока хранения первой и второй групп соответственно, элементы разряда на транзисторах, базы которых соединены с вторыми выводами соответствующих источников тока хранения второй группы, а коллекторы

подключены к соответствующим вторым адресным шинам матрицы элементов памяти, источник тока разряда, первый вывод которого подключен к шине нулевого потенциала, а второй вывод соединен с эмиттерами транзисторов элементов разряда

Известное устройство работает следующим образом,

При подаче на вход выборки накопителя

0 высокого уровня напряжения, лежащего выше уровня напряжения на опорном входе устройства минус пороговое напряжение эмиттерного p-n-перехода транзисторов элементов связи, соответствующий транзи5 стор элемента связи выключается. При этом ток через соответствующие данному входу выборки элементы памяти протекает по цепи: вход выборки накопителя; первая адресная шина; элементы памяти; вторая

0 адресная шина; резистор токоограничи- тельного элемента, источник тока хранения; шина нулевого потенциала. При этом на фронте выбора накопителя ток входа выборки накопителя равен току источника тока

5 хранения, соответствующий транзистор элемента разряда выключен, так как напряжение на его базе еще некоторое время, определяемое задержкой формирователя, задержки, после начала выбора остается ни0 же, чем напряжение на базе аналогичного транзистора преждевыбранной строки матрицы элементов памяти. При выключении транзистора элемента связи потенциал на его коллекторе возрастает и в базу транзи5 стора формирователя задержки через резистор элемента связи от шины питания поступает ток, транзистор формирователя задержки включается. При этом ток через элемент памяти формирователя задержки

0 протекает по цепи: шина питания; переход коллектор - эмиттер транзистора формирователя задержки; первая адресная шина; элементы памяти; вторая адресная шина; резистор токоограничительного элемента;

5 источник тока хранения. При спаде уровня на входе выборки накопителя транзистора элемента связи включается, а величина тока его нагрузки еще некоторое время, определяемое задержкой снижения уровня на вто0 рой адресной шине формирователя задержки, остается равной сумме токов источников тока хранения и тока разряда и, следовательно, все это время элементы памяти, переходящие в невыбранное состояние,

5 получают повышенный ток хранения, обеспечивающий им необходимую помехоустойчивость во время переходного процесса.

Недостатком устройства-прототипа является его сложность, заключающаяся в наличии в каждой строке матрицы элементов

памяти вспомогательных узлов: элемента связи, формирователя задержки, элемента разряда, второго токоограничительногр элемента и второго источника тока хранения.

Целью изобретения является упрощение накопителя для оперативного запоминающего устройства,

Поставленная цель достигается тем, что в накопителе для оперативного запоминаю- щего устройства, содержащем матрицу элементов памяти, первые адресные шины которой являются входами выборки накопителя, источники тока хранения, первые выводы которых подключены к шине нулевого потенциала, токоограничительные элементы на резисторах, первые выводы которых подключены к соответствующим вторым адресным шинам матрицы элементов памяти, вторые выводы источников тока хранения, соединены с первыми выводами резисторов соответствующих токоограничительных элементов, вторые выводы которых объединены.

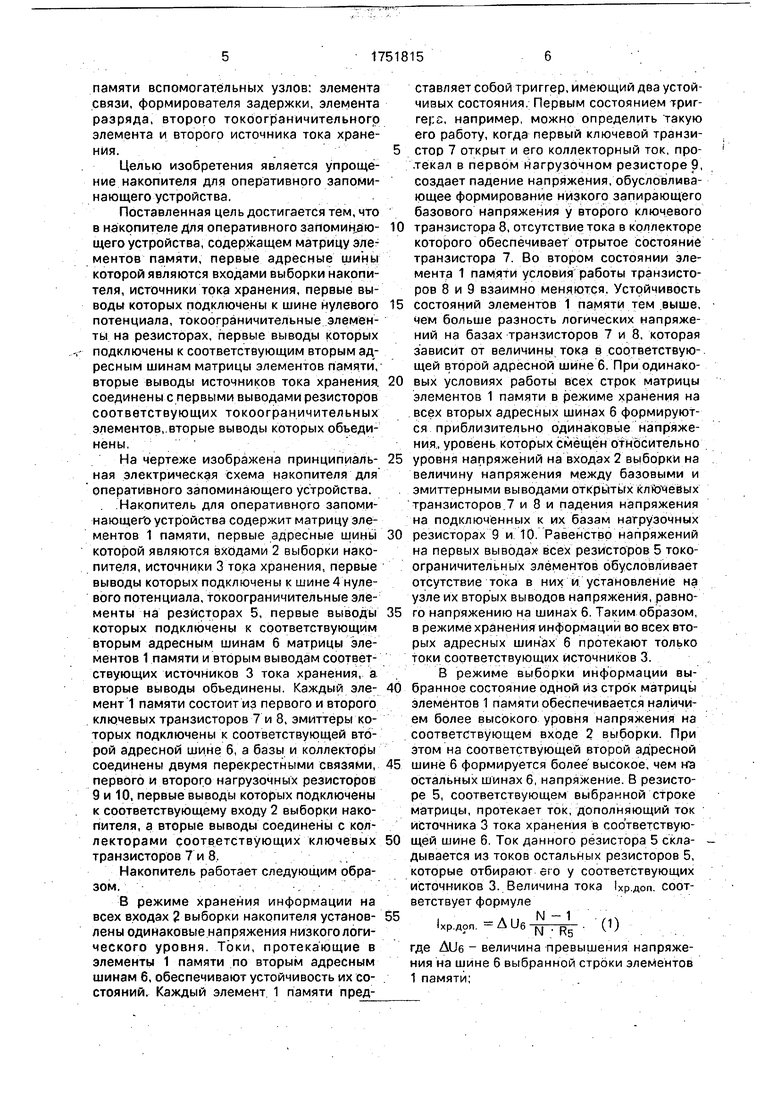

На чертеже изображена принципиаль- ная электрическая схема накопителя для оперативного запоминающего устройства.

Накопитель для оперативного запоминающего устройства содержит матрицу элементов 1 памяти, первые адресные шины которой являются входами 2 выборки накопителя, источники 3 тока хранения, первые выводы которых подключены к шине 4 нулевого потенциала, токоограничительные элементы на резисторах 5, первые выводы которых подключены к соответствующим вторым адресным шинам 6 матрицы элементов 1 памяти и вторым выводам соответствующих источников 3 тока хранения, а вторые выводы объединены. Каждый эле- мент 1 памяти состоит из первого и второго ключевых транзисторов 7 и 8, эмиттеры которых подключены к соответствующей второй адресной шине 6, а базы и коллекторы соединены двумя перекрестными связями, первого и второго нагрузочных резисторов 9 и 10, первые выводы которых подключены к соответствующему входу 2 выборки накопителя, а вторые выводы соединены с коллекторами соответствующих ключевых транзисторов 7 и 8.

Накопитель работает следующим образом.

В режиме хранения информации на всех входах 2 выборки накопителя установ- лены одинаковые напряжения низкого логического уровня. Токи, протекающие в элементы 1 памяти по вторым адресным шинам 6, обеспечивают устойчивость их состояний. Каждый элемент 1 памяти представляет собой триггер, имеющий два устойчивых состояния. Первым состоянием триг- герг, например, можно определить такую его работу, когда первый ключевой транзистор 7 открыт и его коллекторный ток, протекал в первом нагрузочном резисторе 9, создает падение напряжения, обусловливающее формирование низкого запирающего базового напряжения у второго ключевого транзистора 8, отсутствие тока в коллекторе которого обеспечивает отрытое состояние транзистора 7. Во втором состоянии элемента 1 памяти условия работы транзисторов 8 и 9 взаимно меняются. Устойчивость состояний элементов 1 памяти тем выше, чем больше разность логических напряжений на базах транзисторов 7 и 8. которая зависит от величины тока в соответствующей второй адресной шине 6. При одинаковых условиях работы всех строк матрицы элементов 1 памяти в режиме хранения на всех вторых адресных шинах б формируются приблизительно одинаковые напряжения, уровень которых смещен относительно уровня напряжений на входах 2 выборки на величину напряжения между базовыми и эмиттерными выводами открытых клю чевых транзисторов 7 и 8 и падения напряжения на подключенных к их базам нагрузочных резисторах 9 и 10. Равенство напряжений на первых выводах всех резисторов 5 токоограничительных элементов обусловливает отсутствие тока в них и установление на узле их вторых выводов напряжения, равного напряжению на шинах 6. Таким образом, в режиме хранения информации во всех вторых адресных шинах б протекают только токи соответствующих источников 3.

В режиме выборки информации выбранное состояние одной из строк матрицы элементов 1 памяти обеспечивается наличием более высокого уровня напряжения на соответствующем входе 2 выборки. При этом на соответствующей второй адресной шине 6 формируется более высокое, чем нга остальных шинах 6, напряжение. В резисторе 5, соответствующем выбранной строке матрицы, протекает ток, дополняющий ток источника 3 тока хранения в соответствующей шине б. Ток данного резистора 5 скла- дывается из токов остальных резисторов 5, которые отбирают ею у соответствующих источников 3. Величина тока Хрдоп. соответствует формуле

,А ,, N - 1 ,,.

1хрдоп AU6 N . Rs (1)

где AUe - величина превышения напряжения на шине б выбранной строки элементов 1 памяти;

N - количество строк в матрице;

RS - сопротивление резистора 5 токоог- раничительного элемента.

Из формулы (1) видно, что по мере перехода строки элементов 1 памяти в выбранное состояние дополнительный ток хранения возрастает пропорционально ДУб от нуля до максимального значения и падает до нуля по аналогичному закону при возвращении в режим хранения.

Данный накопитель для оперативного запоминающего устройства в режиме выборки информации может оказаться в таких условиях, когда выборка новой строки матрицы осуществляется одновременное переходом преждевыбранной строки в режим хранения. При этом самый неблагоприятный случай будет иметь место, если высокой логический уровень на входе 2 выбираемой строки окажется сформированным раньше, чем начнет падать уровень на преждевыб- ранном входе 2. Дополнительные токи хранения в элементах 1 памяти этих строк матрицы, как бы одновременно оказавшихся в выбранном состоянии, определяются формулой

I хр.доп. А Кб N . Rs

Сопоставляя формулы (1) и (2), легко убедиться в малом отличии хр.доп. от

1хр.доп при больших N, свойственных накопителям для оперативных запоминающих устройств высокой информационной емкости.

Таким образом, изобретение обеспечивает высокую помехоустойчивость накопителя для оперативного запоминающего устройства в режиме выборки информации при минимальном количестве дополнительных элементов, а именно по одному токоог- раничительному элементу на резисторе в каждой строке матрицы элементов памяти, чем и достигается его простота. Формула изобретения

Накопитель для оперативного запоминающего устройства, содержащий матрицу элементов памяти, первые-адресные шины которой являются входами выборки накопителя, источники тока хранения, первые выводы которых подключены к шине нулевого потенциала, токоограничительные элементы на резисторах, первые выводы которых подключены к соответствующим вторым адресным шинам матрицы элементов памяти,

отличающийся тем. что. с целью упрощения накопителя, вторые выводы источников тока хранения соединены с первыми выводами резисторов соответствующих токоограничительных элементов, вторые

выводы которых объединены.

| Валиев К.А., Орликовский А А | |||

| Интегральные схемы памяти на биполярных транзисторных структурах | |||

| М, Сов радио, 1979, с.178, рис.6.16,6 Авторское свидетельство СССР № 1538787, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-18—Подача