ог

-02

СП О2

4 02

;о

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования логических элементов с линией задержки | 1983 |

|

SU1152081A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| Согласующее устройство | 1976 |

|

SU736376A1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| Инвертор | 1983 |

|

SU1160556A1 |

| ТТЛ-элемент | 1985 |

|

SU1274150A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Разностный элемент | 1986 |

|

SU1345337A2 |

| Логический элемент | 1985 |

|

SU1262717A1 |

МНОГОШЛХОДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО ПО авт.ев; 834919, о Тличающеес я тем, что, с целью расширения функциональных возможностей, в него введены дополнительные транзисторы первого типа проводимости, эмиттеры и коллекторы которолх соответственно подключены к эмиттеру и коллектору основного транзистора первого типа-проврдимости, а базы - к дополнительным входам и дополнительным коллекторам транзистора второго типа проводимости. ш

jf

Изобретение относится к импульсной и вычислительной технике и може быть использовано для построения логических и запоминающих устройств. По основному авт.св. № 834919 . известно многовыходное логическое .устройство, содержащее транзистор первого типа проводимости, эмиттер которого соединен с первой шиной питания, база - с входом устройства и коллектором транзистора второго типа проводимости, эмиттер которого подключен к второй шине питания,jaaa - к коллектору транзистора первого типа проводимости, дополнительные коллекторы транзистора .второго типа проводимости подключены к .йыходам устройства, при этом транзистор первого типа проводимости выполнен в виде транзистора Шоттки flJ.

Недостатком известного устройств являются узкие функциональные возможности, так как оно не выполняет логическую функцию ИЛИ.

Цель изобретения - расширение .функциональных возможностей.

Поставленная цель достигается тем, что в устройство, содержащее транзистор первого типа проводимости эмиттер которого соединен с первой шиной питания, база - с входом устройства и коллектором транзистора второго типа проводимости, эмиттер которого подключен к второй шине .питания, база - к коллектору транзис тора первого типа проводимости, дополнительные коллекторы транзистора второго типа проводимости подключены к выходам устройства, введены дополнительные транзисторы первого типа проводимости, эмиттеры и коллекторы которых подключены соответственно к эмиттеру и коллектору основного транзистора первого типа проводимости, а базы - к дополнительным входам и дополнительным коллекторам транзистора второгс типа проводимоети..

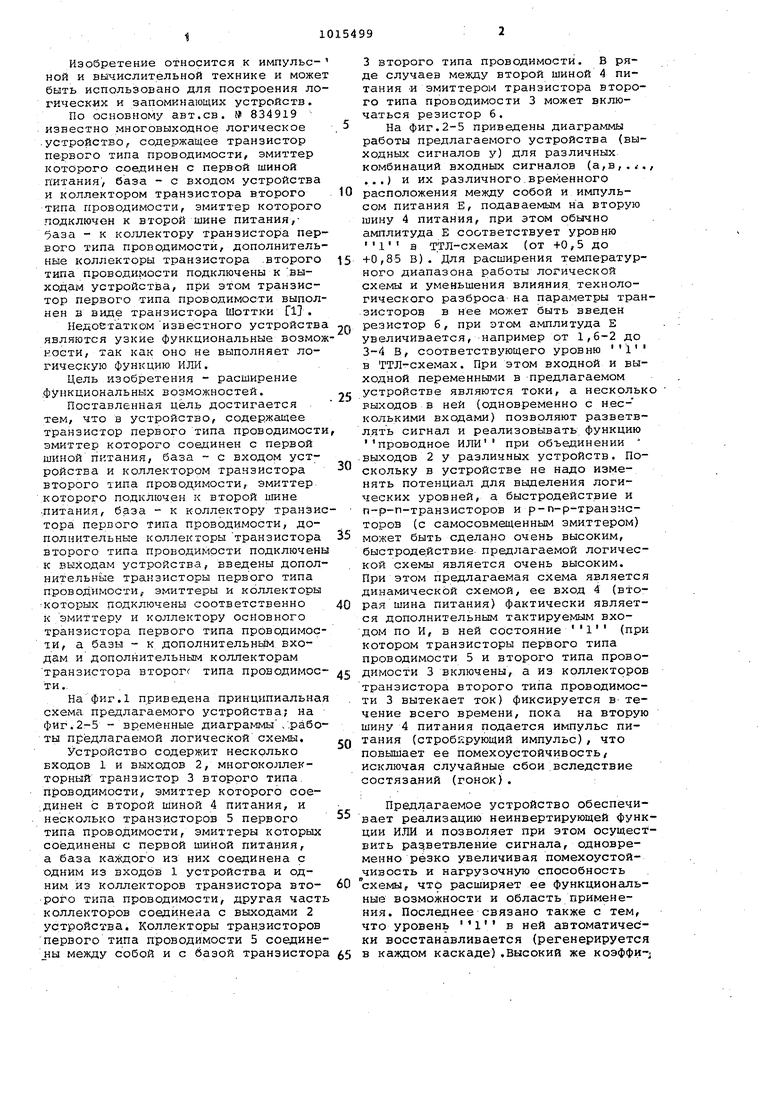

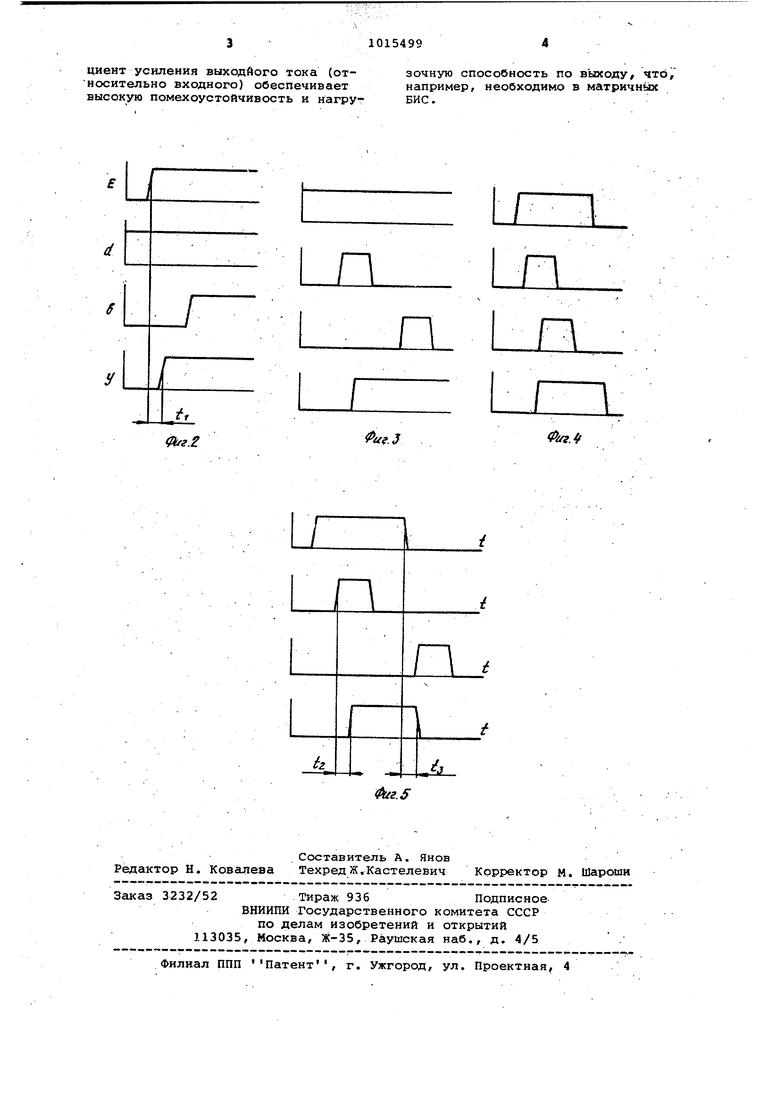

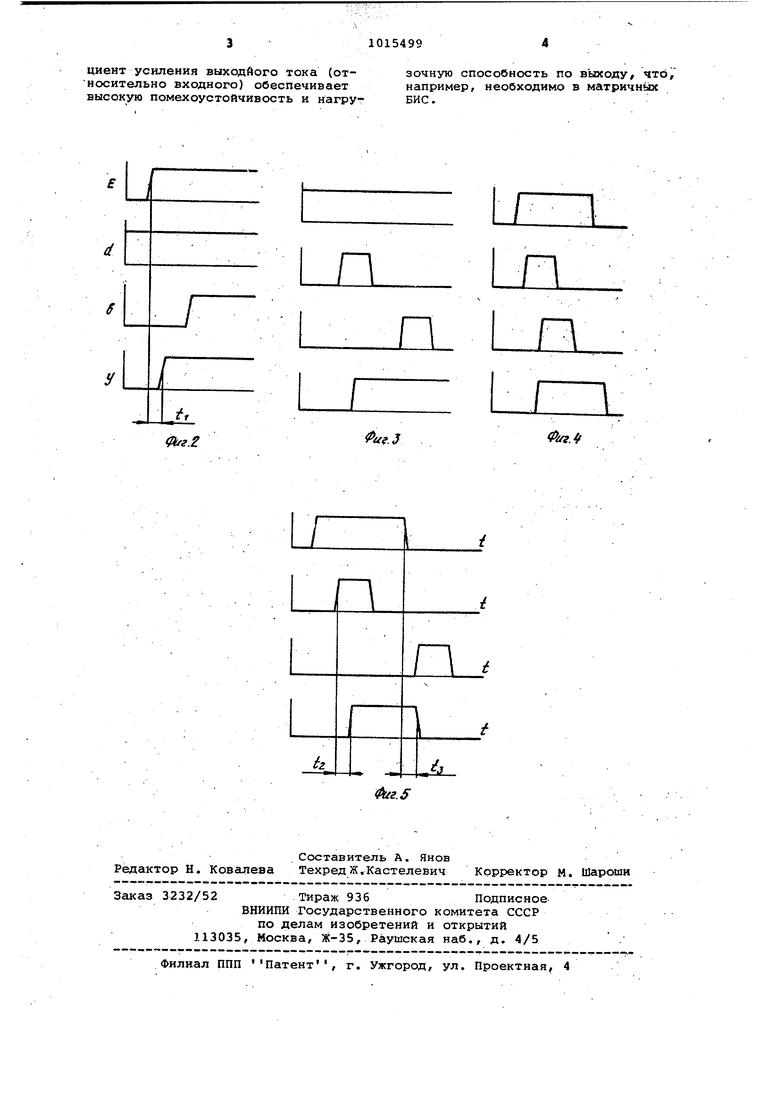

На фиг.1 приведена принципиальная схема предлагаемого устройства; на фИг.2-5 - временные диаграммы/.работы предлагаемой логической схемы. Устройство содержит несколько входов 1 и выходов 2, многоколлекторный транзистор 3 второго типа, проводимости, эмиттер которого сое.динен с второй шиной 4 питания, и несколько транзисторов 5 первого типа проводимости, эмиттеры которых соединены с первой шиной питания, а база каждого из них соединена с одним из входов 1 устройства и одним из коллекторов транзистора второго типа проводимости, другая часть коллекторов соединена с выходами 2 устройства. Коллекторы транзисторов первого типа проводимости 5 соедине ны между собой и с базой транзистора

3 второго типа проводимости. В ряде случаев между второй шиной 4 питания -и эмиттером транзистора второго типа проводимости 3 может включаться резистор 6.

На фиг.2-5 приведены диаграммы работы предлагаемого устройства (выходных сигналов у) для различных комбинаций входных сигналов (а,в,.. ...) и их различного.временного расположения между собой и импульсом питания Е, подаваемым на вторую шину 4 питания, при этом обычно амтлитуда Е соответствует уровню Ч а ТТЛ-схемах (от +0,5 до +0,85 В). Для расширения температурного диапазона работы логической схемы и уменьшения влияния, технологического разброса на параметры тран.зисторов в нее может быть введен резистор б, при этом амплитуда Е увеличивается, например от 1,6-2 до 3-4 В, соответствующего уровню в ТТЛ-схемах. При этом входной и выходной переменными в предлагаемом устройстве являются токи, а нескольк выходов в ней (одновременно с н.ес- колькими входами) позволяют разветвлять сигнал и реализовывать функцию проводное ИЛИ при объединении .выходов 2 у различных устройств. Поскол;ькУ в устройстве не надо изменять потенциал для выделения логических уровней, а быстродействие и п-р-п-транзисторов и р-п-р-транзисторов (с самосовмещенным эмиттером) может быть сделано очень высоким, быстродействие, предлагаемой логической схемы является очень высоким. При этом предлагаемая схема является динамической схемой, ее вход 4 (вторая шина питания) фактически является дополнительным тaктиpye lым вхоROM по И, в ней состояние 1 (при котором транзисторы первого типа проводимости 5 и второго типа проводимости 3 включены, а из коллекторов транзистора второго типа проводимости 3 вытекает ток) фиксируется в- течение всего времени, пока на вторую шину 4 питания подается импульс питания (стробйрующий импульс), что повышает ее помехоустойчивость/ исключая случайные сбои вследствие состязаний (гонок).

Предлагаемое устройство обеспечивает реализацию неинвертирующей функции ИЛИ и позволяет при этом осуществить разветвление сигнала, одновременно резко увеличивая помехоустойчивость и нагрузочную способность схемы, что расширяет ее функциональные возможности и область применения. Последнее связано также с тем.

в ней автоматичесчто уровень

ки восстанавливается (регенерируется в каждом каскаде) .Высокий же коэффи-.

циент усиления выходйого тока (относительно входного) обеспечивает высокую помехоустойчивость и нагруп

e.Z

зочную способность по выходу/ что, например, необходимо в матричных

БИС.

п

п

п

1

.4

Фи.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многовыходное логическое устройство | 1979 |

|

SU834919A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-04-30—Публикация

1981-11-17—Подача