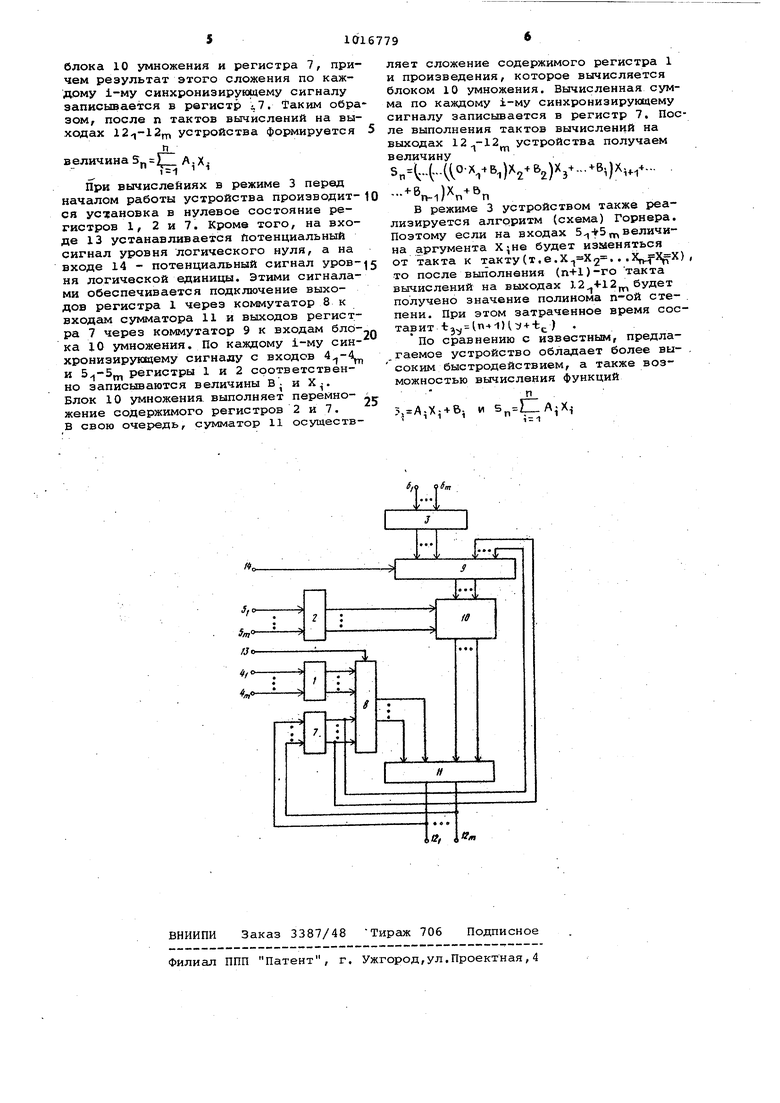

Изобретение относится к вычислительной технике и может быть исполь зовано в цифровых вычислительных ма шинах и системах для получения знач .НИИ функций + В-, SY, LIA. . в в .:. ... +в х в Известно устройство для вычислен значения полинома т-ой степени, со; держащее устройство управления, три сдвигающих регистра, четыре элемент И, счетчик переносов и сумматор 1 Недостатками известного устройст ва являются невозможность вычислени п величины 5 -Z,А.Х.а также низкое быстродействие при формировании зна чений полинома т-ой степени и выражения S -sA-X +B.. Известно множительно-накопительное устройство содержащее блок умно жения, приемные регистры операндов, накопитель и отклонякаций блок 2. Такое устройство позволяет полупчать значения S IZ1 А-Х. однако не п может быть использовано для вычисле ния значений полиномов и Выражения , т.е. обладает узкими фун циональными возможностями. Наиболее близким к предлагаемому является устройство для вычисления суммы степенного ряда. В схеме устройства имеется операционный блок для выполнения операций умножения и - суммирования, регистры аргумента и промежуточного результата, а также сдвиговая память для хранения значений коэффициентов . Такое устройство характеризуется низким быстродействием, поскольку для вычисления полинома п-й степени сначала происходит формирование членов полинома, а затем выполняется их суммирование. Для получения i-ro чле на устройством вычисляется произведе ние Х X (где X - аргумент) , а затем происходит умножение коэффициента А J. на i-ую степень аргумента , т.е X. -Время формирования результата в этом случае t nty + tTH)-tc Я® время умножения двух операндов, ty время сложения двух операндов. Кроме того, прототип обладает узкими функциональными возможностями, так как не позволяет вычислять значе НИН функций 5- А.X... и .. 1111 J-/I Цель изобретения - повышение быст родействия и расположение функциональных возможностей путем обеспечения возможности вычисления функций Vп 5.,..Б, и S.IIlAiX.. Поставленная цель достигается тем, что в вычислительное устройство, содержащее блок умножения, сумматор, регистр аргумента и регистр промежуточного, результата, введены первый и второй буферные регистры, первый и второй коммутаторы, причем установочные входы первого и второго буферных регистров являются соответственно входами первого и второго коэффициентов устройства, управляющие входы первого и второго коммутаторов являются соответственно первым и вторым управляющими входами устройства, установочные входы регистра аргумен.та являются группой входов аргумента устройства, выходы первого буферного регистра соединены с первой группой информационных входов первого коммутатора, выходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходам блока умножения, а выходы сумматора являются группой выходов устройства и соединены с установочными входами регистра промежуточного результата, выходы которого соединены с вторыми группами входов первого и второго коммутаторов, причем первая группа входов второго коммутатора подключена к выходам второго буферного регистра, а выходы второго коммутатора соединены .с первой группой вхо- . дов блока умножения, вторая группа входов которого подключена к выходам регистра аргумента. На чертеже представлена структурная схема устройства. Вычислительное устройство содержит первый буферный регистр 1, регистр 2 аргумента и второй буферный регистр 3. Входы 4.-4 первого коэффициента подключены к установочным входам регистра 1, входы . аргумента - к установочным входам регистра 2, а входы 6-,-б второго коэффициента - к установочным входам регистра 3. В состав устройства также входят регистр 7 промежуточного результата, первый коммутатор 8, второй коммутатор 9, блок 10 умножения и сумматор И, выходы которого являются выходами устройства, и к ним подключены входы регистра 7. К управлявсадему входу коммутатора 8 подсоединен первый вход 13 управления, а к управляющему входу коммутатора 9 - второй вход 14 управления. Выходы регистра 1 соединены с первой группой входов коммутатора 8, выходы которого подключены к первой группе входов сумматора 11, вторая группа входов сумматора 11 соединена с выходами блока 10 умножения, первая группа входов которого подключена к выходам регистра 2, а втора.я группа входов - к выходам KONMyTaTopa 9. Первая группа входов кокя утатора 9 соединена с выходами регистра 3, а вторая группа входов --с второй группой входов коммутатора 8 и выходами регистра 7.

Регистры 1 2, 3 и 7 представляют 5 собой т-разрядные регистры (где т-разрядность поступающих операндов) -с параллельной записью и выдачей информации. Входы управления записью информации в эти регистры на чертеже условЧО во не показаны.

-.

Блок 10 умножения предназначен для перемножения т-разрядных двоичных операндов. Сумматор 11 - это т-разрядный паралл,ельный сумматор комОинационного типа.

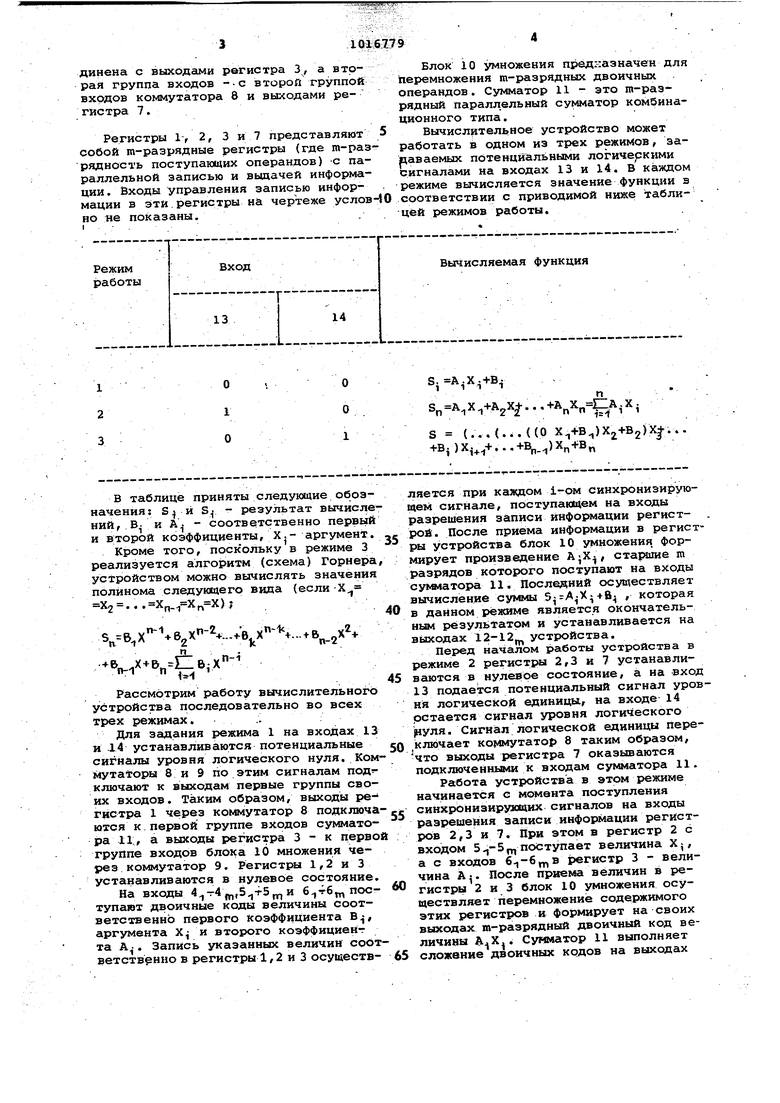

Вычислительное устройство может работать в одном из трех режимов, зараваемых потенциальными логическими сигналами на входах 13 и 14. В каждом режиме вычисляется значение функции в соответствии с приводимой ниже таблицей режимов работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления полиномов | 1982 |

|

SU1067509A1 |

| Вычислительное устройство | 1985 |

|

SU1262485A1 |

| Устройство для вычисления многочленов | 1982 |

|

SU1048481A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления полиномов | 1989 |

|

SU1674112A1 |

| Устройство для вычисления полиномов | 1985 |

|

SU1277098A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок умножения, сумматор, регистр аргумента и регистр промежуточного результата, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей его путем обеспечения возможности вычисления h функций5- А-Х:ч В- м5„ Ц1л-Х, , в него введены первый и второй буферные регистры, первый и второй коммутаторы ;11рич м установочные входы первого и второго буферных регистров являются соответственно входами первого и второго коэффициентов устройства, управляющие входы первого и второго коммутаторов являются соответственно первым и вторым управляющими входами устройства, установочные входы регистра аргумента являются группой входов. apryMeMta устройства, выходы первого буферного регистра соединены с первой группой информационных входов первого коммутатора, выходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходгил блока умножения, а выходу сумматора являются (Л группой выходов устройства, и соединены с установочньши входами регистра промежуточного результата, выходы которого соединены со вторыми группами входов первого и второго коммутато- ров,причем первая группа входов второго коммутатора подключена к выходам второго буферного регистра, а выходы второго коммутатора соединены с первой группой входов блока умнокения, о: вторая группа входов которого подклю-. чена к выходам регистра аргумента. sj « со

Вход

Режим работы

13

О 1 О

1 2 3 в таблице приняты следующие обозначения: S и S - результат вычисле ний,. В и А - соответственно первый и второй коэффициенты, X.- аргумент. Кроме того, поскольку в режиме 3 реализуется алгоЁ итм (схема) Горнера устройством можно вычислять значения полинома следующего вида (если Х 2 п-1 ..;e ... ,Х+&„-Е:В-Х - Рассмотрим работу вычислительного устройства последовательно во всех трех режимах. Для задания режима 1 на входах 13 и .14 устанавливаются потенциальные сигналы уровня логического нуля. Ком мутаторы 8 и 9 по этим сигналам подгключают к выходам первые группы своих входов. Таким образом, выходы регистра 1 через коммутатор 8 подключа ются к.первой группе входов сумматора 11 , а выходы регистра 3 - к перво группе входов блока 10 множения через коммутатор 9. Регист1мл 1,2 и 3 устанавливаются в нулевое состояние. На входы , 6 4-6„поступают двоичные коды величины соответственно первого Коэффициента В, аргумента Х и второго коэффициента А. Запись указанных величин соответств нно в регистры 1,2 и 3 осуществВычисляемая функция

S,A.X.+B

,..,..

S (... (.i.({0 )Х,Ч-В2)Х±.. +В.)Х,+ ...+В„.)Х„+В„ ляется при каждом 1-ом синхронизирующем сигнале, поступающем на входы разрешения записи информации регистрой. После приема информации в регистры устройства блок 10 умножения. Формирует произведение , ста1яаие m разрядов которого поступают на входы cyhtttaTOpa 11. Последний осуществляет вычисление суммы , которая в данном режиме является окончательным результатом и устанавливается на выходах 12-12 устройства. Перед началом работы устройства в режиме 2 регистры 2,3 и 7 устанавливаются в нулевое состояние, а на вход 13 подается потенциальный сигнал уровня логической единицы, на входе 14 остается сигнал уровня логического руля. Сигнал логической единицы Пере/ключает ком «утатор 8 таким образом, что выходы р егистра 7 оказываются подключенными к входам сумматора 11. Работа устройства в этом режиме начинается с момента поступления синхронизирующих сигналов на входы разрешения записи информации регистров 2,3 и 7. При этом в регистр 2 с входом поступает величина Х, а с входов регистр 3 - величина А. После приема величин в регистры 2 и 3 блок 10 умножения осуществляет перемножение содержимого этих регистров и формирует на своих выходах т-разрядный двоичный код величины .i Сумматор 11 выполняет сложение двоичных кодов на выходах

блока 10 умножения и регистра 7, причем результат этого сложения по каждому 1-му синхронизирующему сигналу записывается в регистр 1. Таким образом, после п тактов вычислений на выхсщах 12-,-12 устройства формируется п

величина5„ Г11 А.Х- jTi 1 1

При вычислениях в режиме 3 перед началом работы устройства производится установка в нулевое состояние регистров 1, 2 и 7. Кроме того, на входе 13 устанавливается Потенциальный сигнал уровня логического нуля, а на входе 14 - потенциальный сигнал уровня логической единицы. Этими сигналами обеспечивается подключение выходов регистра 1 через коммутатор 8 к входам сумматора 11 и выходов регистра 7 через коммутатор 9 к входам блока 10 умножения. По каждому i-му синхронизирующему сигналу с входов и регистры 1 и 2 соответственно записываются величины В и Х. Блок 10 умножения, выполняет перемножение содержимого регистров 2 и 7, В свою очередь, сумматор 11 осуществляет сложение содержимого регистра 1 и произведения, которое вычисляется блоком 10 умножения. Вычисленная сумма по каждому i-му синхронизирующему сигналу записывается в регистр 7. После выполнения тактов вычислений на выходах устройства получаем величину

Sn444i°-V)))Hi--- B i)V%

в режиме 3 устройством также реализируется алгоритм (схема) Горнера. Позтому если на входах 5 +5 величина аргумента будет изменяться от такта к такту (т.е... . то после выполнения (п+1)-го такта вычислений на выходах будет получено значение полинома п-ой степени. При этом затраченное время составит i:3,)) .

По сравнению с известным, предлагаемое устройство обладает более высоким быстродействием, а также возможностью вычисления функций

п 5. Л.Х + В, и

М

J,0,

Sn,

/Jo

«/«-:- -5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления значения полинома -ой степени | 1978 |

|

SU744559A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1983-05-07—Публикация

1981-11-02—Подача