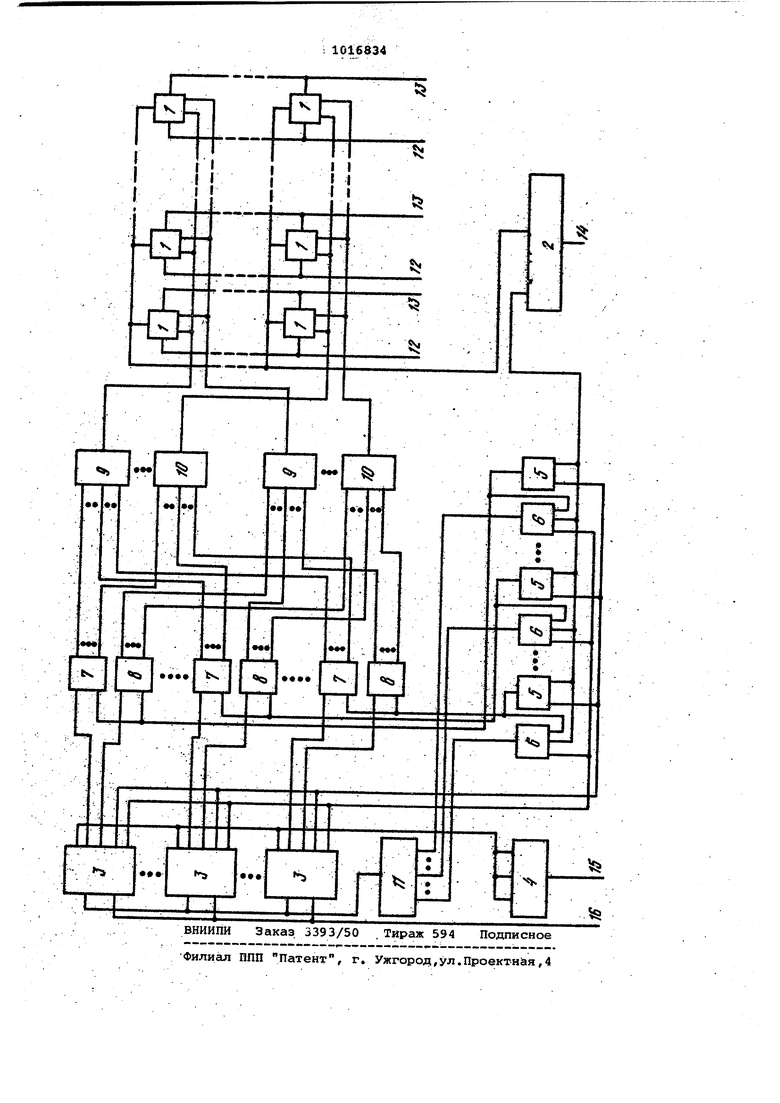

Изобретение относится к вычислительной технике и может быть испаль зовано при проектировании оперативяых запоминающих ycTpoJtcTB цифровых вы ислиоепьных маишн. Известно запоминакадее устройство содержащее матричный накопитель, ре гистр адреса, генератор управляющих импульсов и дешифратор тактовых сиг налов Сп Недостатком данного устройства является низкое быстродействие из-з невоэможнОсти начать новое обращени даже к другой строке матричного накопителя до окончания предыдущего о ращения, Наиболее близким к предлагаемому по технической сущности является устройство, содержащеематричный накопитель с К строками, регистр адреса, .дешифратор строк, К генераторов управляющих импульсов, формирователь сигнала записи-считывания и блок фор мирования сигнала разрешения обращения, причем адресные входы блоков йамяти матричного накопителя .соединены с выходами регистра адреса, их тактовые входы-- с первыми выходами генераторов управляющих импульсов, входы записи-считывания - с выходом формирователя сигнала записи-считывания, информационные входы и выходы являются входами и выходами устройства, вход формирователя записисчитывания является входом записисчитывания устройства, вторые выходы генераторов управляющих импульсов соединены с входами блока формирования сигнала разрешения обращения, а его выход является управляюдам выходом устройства, входы генераторов управляющих импульсов соединены с выходами дешифратора строк, а его входы - с выходами регистра адреса, входы которого явлйются адресными входами устройства. Устройство характеризуется возможностью выполнения обращений в режиме совмещения циклов и следовательно, высоким быстродействием f2. Недостатком известного устройства является сложность схем управления из-за большого количества генераторов управляющих импульсов,. Цель изобретения -.упрощение устройства за счет уменьшения количества генераторов управляющих импульсов без снижения его быстродействия. Поставленная цель достигается тем, что запоминающее устройство, содержащее регистр адреса, ганераторы управляющих импульсов, блок .формирования сигнала разрешения обращения и -Матричный накопитель с К стро; ками (к гр-(Где N - емкость запо-. минающего устройства, fn емкость блоков памяти, матричного накррителя), причем адресные входы блоков памяти матричного накопителя соединены с выходами регистра адреса, а их информационные входы и выходы являются входами и выходами устройства j входы регистра адреса являются, адресными входа1ли устройства, входы блока форишрования сигнала разрешенияобращения соединены с первыми выходами генераторов управлякяцих импульсов, а его выход является управляющим выходом устройства дополнительно содержит m регистров номера строки (где К 2) , «1 схем сравнения,m дешифраторов тактовых сигналов,m дешифраторов сигналов записи-исчитывания, две группы по, R элементов ИЛИ и блок запрещения запуска генераторов управляющих импульсов, причем тактовые входы и. входы-записи-считывания блоков памяти каждой строки матричного накопителя соединены с выходами соответствующих элементов ИЛИ первой и второй групп соответственно, одноименные выходы дешифраторов тактовых сигнешов и дешифраторов сигналов записи-считывания соединены с входами Соответствующих элементов ИЛИ первой и второй групп соответственно, стробирующие входам дешифраторов тактовых сигналов и дешифраторов сигналов записи-считывания подключены соответственно к вторым и третьим выходам соответствующих генераторов управляющих импульсов, входы дешифраторов тактовых сигнсшов, дешифраторов сигналов записи-считывания и входы первой группы входов схем сравнений подключены к выходам соответствующих регистров номера строки, входы регистров номера строки и входы второй ГРУППЫ входов схем сравнения подключены к соответствующим выходам регистра адреса, стробирующие входы регистров номера строки и схем сравнения подключены соответственно к четвертому и пятому выходам.соответствующих генераторов управляющих импульсов, выходы схем сравнения соединены с входами блока запрещения з.апуска генераторов управляющих импульсов, а его выход - с первыми входами генераторов управляющих импульсов, вторые входы которых объединены и являются входом записи-считывания запоминающего устройства. На чертеже изображена структурная схема устройства. Запоминающее устройство содержит блоки 1 памяти матричного накопителя (не показан), регистр 2 адреса, m генераторов 3 управляющих импульсов, блок4 формирования сигнала р 13решения обращения, m регистров 5 номера строки, m схем 6 сравнения, гп дешифраторов 7 тактовых сигналов, n дешифраторов 8 сигналов записисчитывания, К элементов ИЛИ 9 перво группы, К элементов Или 10 второй группы, блок 11 запрещения запуска генераторов уп авляющих импульсов, причем аяресные входа блоков 1 памяти матричного накопителя соединены с регистром 2 адреса, а их информационнью входы и выхода являются вводами 12 и выходами 13 устройства, входа регистра адреса являются адресными входами 14 устройства, блока 4 формирования сигнала разреиения о1ИРс1щения соединены с первыми выходами генераторов 3 управляющих импульсов, а его выход является управляквдим шяходсяч 15 .устройства. Тактовые входгг и входы записисчитывания блркйв 1 памяти каждой строки матричного накопителя соединены соответственно с выходами соответствующих элементов ИЛИ 9 и 10 первой и второй групп, одноименные выходы дешифраторов 7 тактовых сигналов и дешифраторов 8 сигналов записи-считывания соедатнены с входаtm соответствующих элементов ИЛИ 9 и 10 первой и второй групп соответственно, стробирующие входы дешифраторов 7 тактовых сигналов и дешифраторов 8 сигналов аписи-считывания подключены соответственно к вторьалли третьим выходам соответствующих генераторов 3 управляющих импульсов, входы дешифраторов 7 тактовых сигналов, дешифраторов 8 сигналов записи-считывания и входаа группы входов схем 6 сравнения подключены к выходам соответствуюп х регистров 5 номера строки.

Входы регистров 5 номера строки и входы второй группы входов схем 6 сравнения подключены к соответствующим выходам регистра 2 адреса, стробируюшие входы регистров 5 номера строки и схем 6 сравнения подключены соответственно к четвертому и пятому выходам соответствующих генераторов 3 управляяэпшх импульсов, выходы схем б сравнения соединены с входами блока 11 запрещения запуска генераторов управляющих импульсов, а его выход - с первыми входами генераторов 3 управляющих импульсов, вторые вхо; которых объединены и являются входом 16 записи-считывания запоминакйцего устройства.

Устройство работает следующим образом.

Генераторы 3 управл;я1свд1х импульсов запускаются по оч1ереди. Если ни .один из генераторов 3 управляющихимпульсов не запущен отсутствует наложение обращений), процессор записывает в регистр 2 адрес И запускает очередной генератор 3 управляющих импульсов. Запущенный генератор 3 управлякшшх импульсов

разрешает прием в соответствующий регистр 5 номера строки кода номера строки, формирует строб соответствующего дешифратора 7 тактовых си1налрв,, который через соответствующие элементы ИЛИ 9 первой группы -разрйаает прием адреса на внутренние регистры адреса блоков 1 памяти выбранной строки матричного накопителя, и стробирует блок 4 формирования

0 сигнала разрешения обращения. При выполнении записи запущенный генератсф 3 управляющих Импульсов формирует строб соответствувддего даиифратора 8 сигналов записи-считывания,

5 при этом через соответствующие элементы ИЛИ 10 второй группы сигнал записи передается на выбранную строку матричного накопителя. После по лучения сигнала разрешения обращеQ ния процессор может .записать в регистр 2 адреса адрес следующего обращения.

Запущенный генератор 3 .управляющих импульсов формирует строб соответствующей схемы 6 сравнения. Если номера строк текущего и следуквдего обращений совпадаю±, то запуск следующего генератора 3 управЛяккщих импульсов блокируется до окончания

0 строба схемл б сравнения, длительность которого равна времени цикла блока 1 памяти, и наложение обращений отсутствует. Если номера строек текущего и следующего обращений не

5 совпадают, следукяцее обращение начинается сразу после фиксации адреса на внутренних регистрах адреса блоков 1 памяти .В э.том случае максимальный темп обмена процессора с

0 запоминающим устройством определяется нвобходи м временем фиксации адреса на регистре 2 адреса (адресные цепи пдя всех строк матричного наколителя обгаие).

5i . - -

Для полного использования быстродействия блоков 1 памяти количество {енердто0ов 3 управляющих импульсов, регисг|зов 5 номера отроки, схем 6

0 , дешифраторов 7 тактовых сигналов и Део фраторов 8 сигналов записи-считывалия должно быть не меньше от«1а01е«ия времени цикла блоков 1 памяти и йрем&ни фиксации ад- реса их адресных входах. Если в

кгместве блоков 1 памяти применить микросхему К565РУЗА, а схемы управления выполнить на микросхемах серии , это отношение может быть равно 2-3. Количество строк К матричного накопителя дпя памятей большой равно 8-16 и более, поэтому такая структура управления позволяет без уменьшения быстродействия уменьшить количество генераторов упра5& :тшаих импульсЬв до 2-3

51016834в

на устройство вместо одного на мощью небольшого количества генерастроку.торов управляющих импульсов позвоТаким обраэсм, предлагаемое за- равлёния без снижения быстродействия помингиоидае устройство за счет форми- оперативногЬ запоминающего-устройрования управляющих сигнале с - 5 ства большой емкости.

ляет существеино упростить цепи уп

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Генератор случайного Марковского процесса | 1982 |

|

SU1070548A1 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержатее регистр адреса, генераторы управляющих импульсов, блок формирования сигнсша разрешения обращения и матричный накопитель с К строками (К тг, где N - емкость запоминающеN. М го устройства, Мд - емкость блоков памяти матричного накопителя), адресные входы блоков памяти матричного накопителя соединены с выходами регистра адреса, а их инфор мационные входы и выходы являются входами и выходами устройства, входы регистра адреса являются адресными входами устройства, входы блока формирования сигнала разрешения обращения соединены с первыми выходами генераторов управляющих импульсов, а его выход является управляющим выходом устройства, о т л и ч а ю щ ее с я тем, что, с целью упрощения устройства без снижения его быстродействия , оно содержит m регистров номера строки (где К гп , 2),тсхем сравнения,m дешифраторов тактовых сигналов,m дешифраторов сигналов записи-считывания, две группы по К элементов ИЛИ и блок запрещения запуска генераторов управляющих импульсов, причем тактовые входы и входы записи-считывания блоков памяти каждой строки матричного накопителя соединены с выходами соответствующих элементов ИЛИ первой и второй групп соответственно, одноименные выходы дешифраторов тактовых сигналов и дешифраторов сигналов записи-считывания соединены с входами соответствующих элементов ИЛИ первой и второй групп соответствено, стробирующие входы дешифраторов тактовых сигналов и дешифраторов сигналов записи-считывания подключены соответственно к вторым и третьим выходам соответст- вующих генераторов управляквдих имсл пульсов, входы дешифраторов тактовых сигналов, даиифраторов сигналов запиic си-считывания и входы первой группы входов схем сравнения подключены к выходам соответствующих регистров номера строки, входы регистров номера -строки и входы второй группы входов схем сравнения подключены к соответствующим выходам регистра адреса., стробирующие входы регистров номера Од строки и схем сравнения подключены соответственно к четвертому и пято00 му выходам соответствующих генератосо ров управляющих импульсов, выходы 4 схем сравнения соединены с входами блока запрещения запуска генераторов управляющих импульсов, а его выход с первыми входами генераторов управляющих импульсов, вторые входы которых объединены и являются входом записи-считывания запоминающего устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Андреев В | |||

| П | |||

| и др | |||

| Полупроводниковые запоминающие устройства и их применение | |||

| М., Радио и связь, 1981, с | |||

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Полупроводниковое запоминающее устройство | 1975 |

|

SU598120A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-05-07—Публикация

1982-01-15—Подача