Изобретение относится к вычислительной технике, электронике и автоматике.

Известен многофункциональный логический элемент на МДП-транзистора содержащий первый и второй элементы равнозначности, у которых входы подключены к информационным и управляющим шинам, а выходы через aJfeMeH И подключены к входу третьего элемента равнозначности, второй вход которого подключен к соответртвую1щей управляющей шине l.

Недостатками данного элемента являются низкое быстродействие и болшая потребляемая мощность.

Известен также многофункциональный логический элемент на МДП-транзисторах, содержащий входную шину первого логического сигнала, подключенную к входу первого инвертора, входную шину второго логического сигнала, подключенную к входу второго инвертора, входнуй шину третьего логического сигнала, подключенную к элементу равнозначности, и выходной усилитель. Отличительной особенностью такого элемента является то, что он содержит три последовательно включенных каскада, выполненных на МДП-транзисторах р-типа 2J..

Недостатками указанного элемента являются низкое быстродействие и большая потребляемая мощность.

Цель изобретения - повышение быстродействия и уменьшение потребляемой- мощности.

Поставленная цель достигается тем что в многофункциональный логический элемента на ВДП транзисторах, содержащий входную шину первого логического сигнала, подключенную к входу первого инвертора, -входную шину второго логического сигнала, подключенную к входу второго инвертора, и входную шину третьего логического сигнала, введены две цепочки из двух последовательно включенных транзисторов р-типа, первая из которых включена между выходом первого инвертора и выходной шиной, а вторая - между выходом второго инвертора и выходной шиной, и три цепочки из двух последовательно включенных транзисторов п-типа, включенные между выходной шиной и общей шиной, причем затворы транзисторов р-типа первой цепочки подключены, соответственно к выходу второго инвертора и к входной шине инверсии третьего логического сигнала, затворы транзисторов р-типа второй цепочки - к выходу первого инвертора и к входной шине третьего логического сигнала, затворы транзисторов п-типа первой цепочки - к входной шине третьего логического сигнала и к входной шине третьего логического сигнала и к входной шине первого логического сигнала, затворы транзис-торов п-типа второй цепочки -.к входной шине инверсии третьего логического сигнала и к входной шине второго логического сигнала, а зат/воры транзисторов п-типа третьей цепочки - к выходу первого инвертора и к выходу второго инвертора.

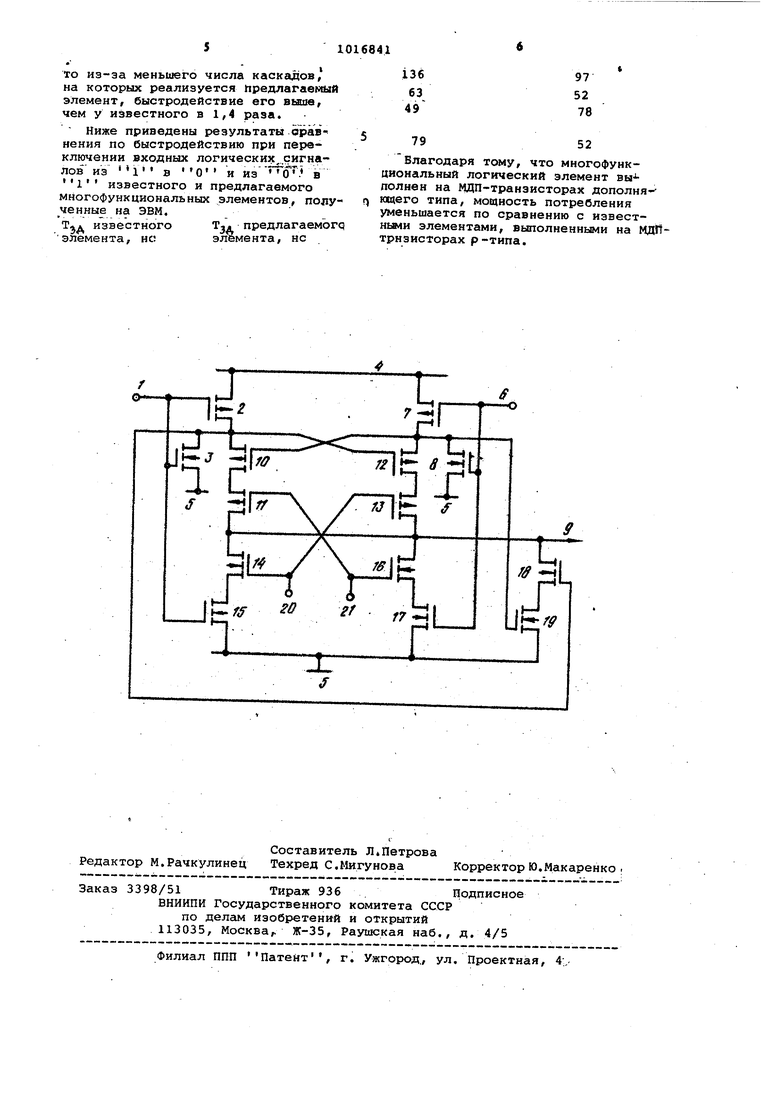

На чертеже представлена электрическая принципиальная схема предлагаемого элемента.

Элемент содержит входную шину 1 первого логического сигнала А, под(ключенную к входу первого инвертора (На МДП-транзисторах 2 и 3 дополняющего ипа, включенных между шиной 4 питания и общей шиной 5. Входная ишна б второго логического сигнала В подключена к входу второго инвертора выполненного на МДП-транзисторах 7 и 8 допОлнянлдего типа. Между выходом первого инвертора и выходной шиной 9 включена первая цепочка из двух - последовательно включенных транзисторов 10 и 11 р-типа. Между выходом второго инвертора и выходной шиной. 9 включена вторая цепочка из двух последовательно включенных транзисторо 12 и 13 р-типа. Между шинами 9 и 5 включены три цепочки, каждая из которых содержит два последовательно включенных транзистора 14 и 15,16 и 17 и 18 и 19|1-типа. Затворы транзисторов 2, 3 и 15 подключены к шине 1, а затворы транзисторов 7,8 и 11 - к шине 6 К шине 20 третьего логического сигнала С подключены затворы транз.исторов 13 и 14, а к шине 21 инверсии третьего логического сигнала С затворы транзисторов 11 и 16.

Выход первого инвертора, образованный стоками транзисторов 2 и 3, подключен к затворам транзисторов 12 и 18, а вь1ход второго инвертора, образованный стоками транзисторов 7 и 8 - к затворам транзисторов 10 и 1

Работа логического элемента иллюстрируется с помощью табл.1 и 2.

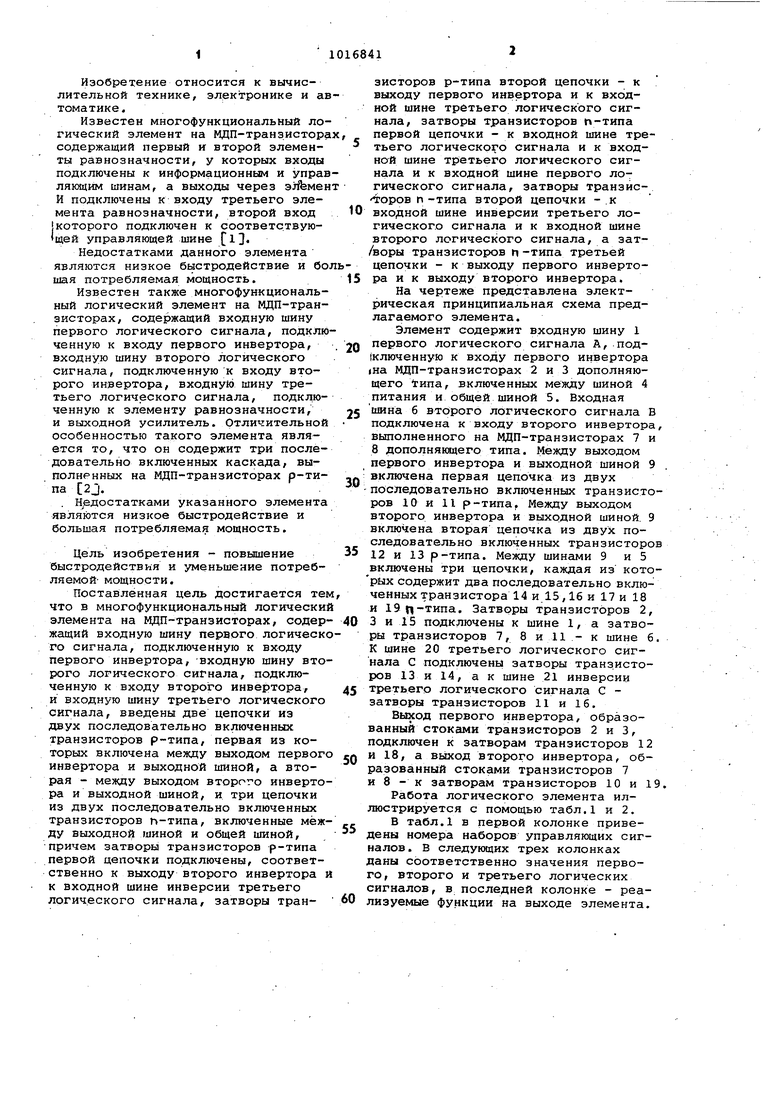

В табл.1 в первой колонке приведены номера наборов управляющих сигналов. В следующих трех колонках даны соответственно значения первого, второго и третьего логических сигналов, в последней колонке - реализуемые функции на выходе элемента.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| Логический элемент | 1981 |

|

SU997252A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Многофункциональный логический элемент | 1981 |

|

SU1005313A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| ЛОГИЧЕСКОЕ (МНОГОФУНКЦИОНАЛЬНОЕ) УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2081509C1 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| Логический элемент | 1982 |

|

SU1018250A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ на МДП-транзисторах, содержащий входную шину первого логического сигнала, подключенную к входу первого инвертора, входную шину .второго логического сигнала, подключенную к входу-второго инвертора, и входную шину третьего логического сигнала, отличающий с я тем, что, с целью повышения его быстродействия и уменьшения потребляемой мощности, в него введены две 11епочки из двух последовательно включенных транзисторов р-типа, первая из которых включена между выходом первого инвертора и выходной шиной, а вторая - между выходом второго инвертора и выходной шиной, и три цепочки яэ двух последовательно включенных транзисторов h-типа, включенные между выходной шиной и общей шиной, причем затворы транзисторов р-типа первой цепочки подключены соответственно к выходу второго инвертора и к входной шине инверсии третьего логического сигнала, затворы транзисторюв р-типа второй цепочки - к выходу первого инвертора и к входной шине третьего логического сигнала, затворы транзисторов п-типа первой цепочки - к входН (Л ной шине третьего логического сиг- I нала и к входной шине первого логи- i ческого сигнала, затворы транзисторов h-типа второй- цепочки - к входной шине инверсии третьего логического сигнала и к входной шине второго ло- гического сигнала, а затворы транзисторов п-типа третьей цепочки - к выходу первого инвертора и к выходу второго инвертора. О) 00

1

9

1

О

Xi

О

X,

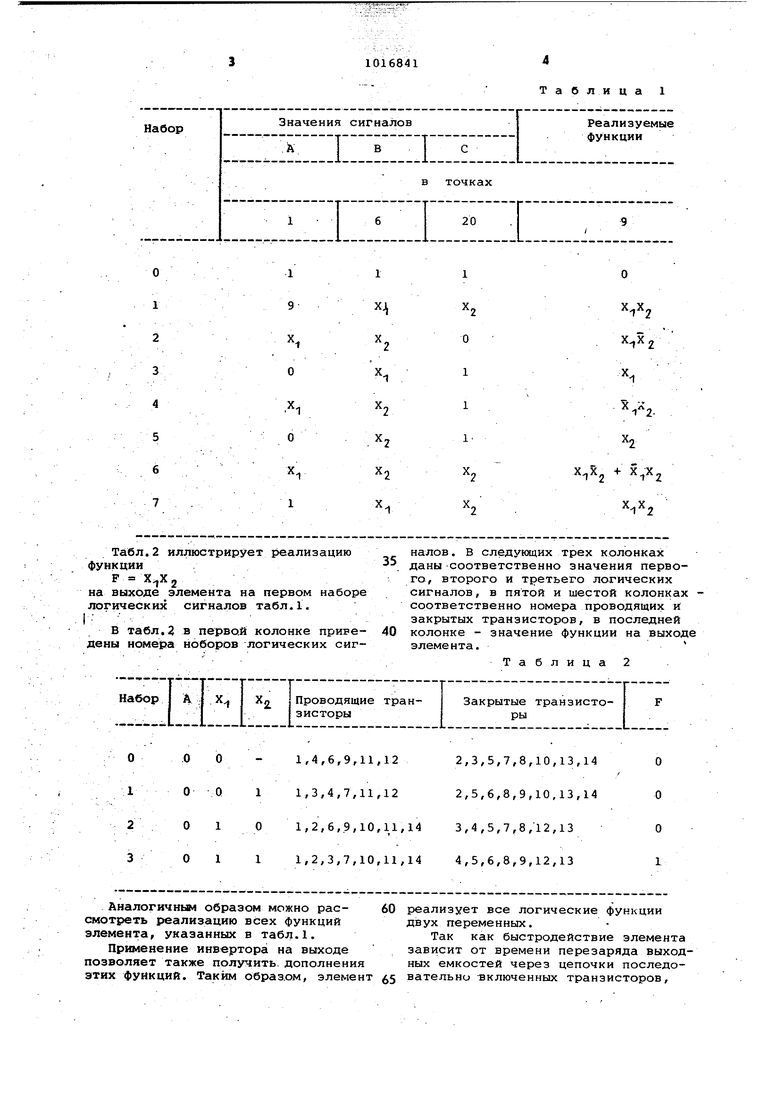

Табл.2 иллюстрирует реализацию функции

F

на выходе элемента на первом наборе логических сигналов табл.1.

В табл.2 в первай колонке приведены номера ноборов логических сигНабор

Проводящие транзисторы

0О О -1,4,6,9,11,12

1О Q 11,3,4,7,11,12

2О 1 О1,2,6,9,10,11,14

30111,2,3,7,10,11,14

Аналогичным образом можно рассмотреть реализацию всех функций элемента, указанных в табл.1.

Применение инвертора на выходе позволяет также получить, дополнения этих функций. Таким образ.ом, элемент

1

Xj

о 1

1

х„

Х.Х

налов. В следующих трех колонках даны -соответственно значения первого, второго и третьего логических сигналов, в пятой и шестой колонках соответственно номера проводящих и закрытых транзисторов, в последней колонке - значение функции на выходе элемента.

Таблица2

Закрытые транзисторы

2,3,5,7,8,10,13,14 2,5,6,8,9,10,13,14 3,4,5,7,8,-12,13 4,5,6,8,9,12,13

реализует все логические функции двух переменных.

Так как быстродействие элемента зависит от времени перезаряда выходных емкостей через цепочки последовательно -включенных транзисторов.

то из-за меньшего числа каскадов, на которых реализуется нредлагаеиый элемент, быстродействие его вшив, чем у известного в 1,4 раза. Ниже приведены результаты орав нения по быстродействию при переключении входных логически5,..сигналов из 1 э О и из о . в 1 известного и предлагаемого многофункциональных элементов, полученные на ЭВМ.

Tj, предлагаемог

известного

ЭА элемента, не .

элемента, не

97 52 78

52

Благодаря тому, что многофункциональный логический элемент вы- полнен на МДП-транэисторах дополня-towero типа, мощность потребления уменьшается по сравнению с известными элементами, выполненными на Mflltтрнзисторах р-типа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический элемент | 1977 |

|

SU686146A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофункциональный логический элемент | 1978 |

|

SU718928A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-07—Публикация

1982-02-22—Подача