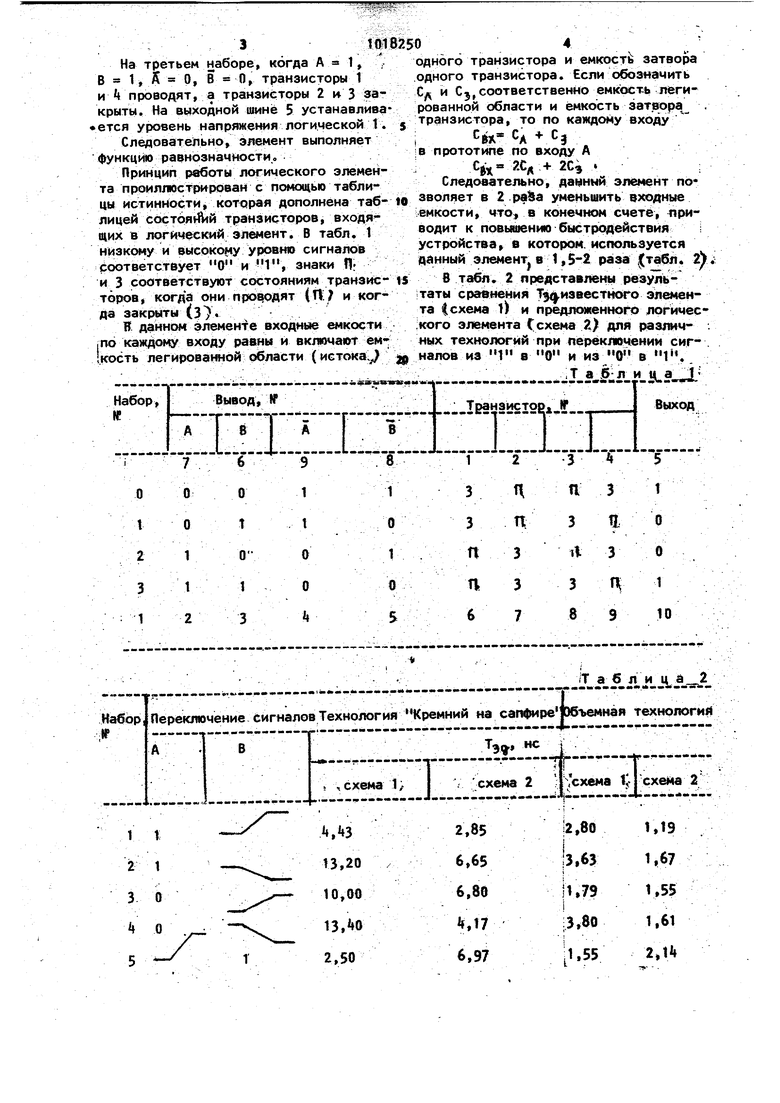

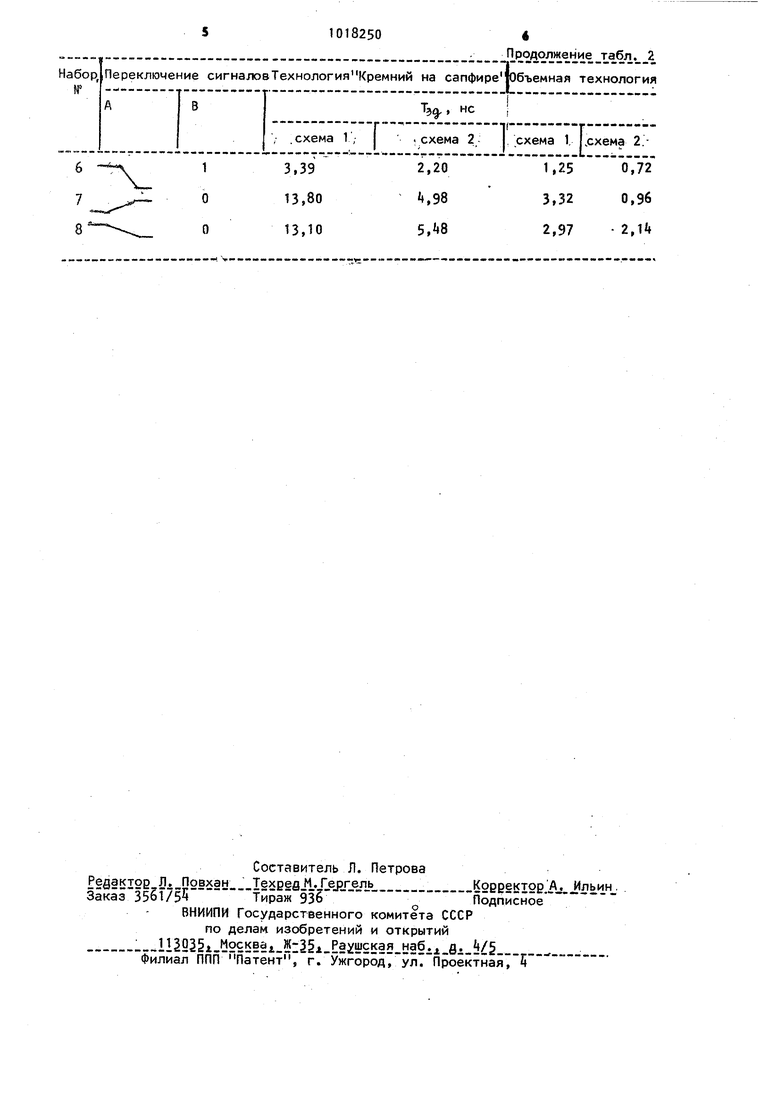

110 Изобретение относится к вычислительной технике, электронике, автома тике, в частности может быть использовано в интегральных микросхемах и БИС на дополняющих МДП-транзисторах. Известен логический элемент на до полняющих МДП-транзисторах, на выходе которого выполняются функции равнозначности С 1 3. Недостатком этого элемента являет ся его сложность. Логический элемент содержит большое число МДГ(-транзисто ров. Известен логический элемент, содержащий два М-канальных транзистора и два р-канальных транзистор, ст ки которых подключены к выходной шине, затвор первого И-канального тран зистора подключен ко входной шине первого логического сигнала, затвор первого р-канального транзистора подключен к входной шине второго логического сигнала, к входной шине первого логического сигнала подключе ны также истоки первого р-канального транзистора и второго i-канального транзистора, а также затвор второго р-канального транзистора., к входной шине второго логического сигнала под ключен исток второго р-канального У транзистора, а к входной шине инверсии второго логического сигнала подключен затвор второго п-канального транзистора и исток первого И-каналь ного транзистора 21. Недостаток известного элемента за ключается в низком быстродействии, различном при разных наборах входных переменных за счет неравномерно распределенной емкостной нагрузки на входных шинах логических сигналов. Емкостная нагрузка по входной шине первого логического сигнала превышае емкостную нагрузку по входным шинам других логических сигналов за счет того, что ко входной шине первого ло гического сигнала , подклочены две легированные области (истоки транзисторов р- и yi-типа и емкости затворов других транзисторов р- и И-типа. Целью изобретения является повышение и выравнивание быстродействия при фазных наборах входных переменных. Поставленная цель достигается тем что в логическом элементе, содержащем два И-канальных транзистора и .дваР-канальных транзистора, стоки к 0 торых подключены к выходной шине, затвор первого и-канального транзистора подк/вочен к входной шине первого . логического сигнала, а затвор первого р-канального транзистора подключен к входной шине второго логического сигнала,ко входной шине второго логического сигнала подключен исток первого и -канального транзистора, ко входной шине первого логического сигнала подключен исток.второго р-канального транзистора, ко входной не инверсии второго логического сигнй ла подключен исток второго vi-канального транзистора и затвор второго р-канального транзистора, а ко входной шине инверсии первого логического Сигнала подключен исток первого Р-канального транзистора и затвор второго И-канального транзистора. На чертеже представлена электрическая принципиальная схема устройства. Стоки двух h-канальных транзисторов 1 и 2 и двух р-канальных транзисторов 3 и подключены к выходной шине 5. Ко входной шине второго логического сигнала 8(6 подкш чен исток транзистора 1 и затвор транзистора 3, ко входной шине первого логического сигнала 1 (7) подключен исток транзистора 1, ко входной шине инверсии вто рого логического сигнала В (8) подключен ис:ток транзистора 2 и затвор транзистора , а ко входной шине инверсии первого логического сигнала А( 9 ) подключен исток транзистора 3 и затвор транзистора 2. Устройство работает следующим образом. На н; левом наборе, когда А О, В О, А 1, В - 1, транзисторы 2 и 3 проводят ji а транзисторы 1 и k закрыты. На выходной шине 5 устанавливается уровень напряжения логической t. На ngpBOM наборе, когда А 0, В 1 А 1, В 0, транзисторы 2 и Л проводят, а транзисторы 1 и 3 закрыты. На выходной шине 5 устанавливается уровень напряжения логического О. На втором , когда А i В О, Д О, В 1, транзисторы 1 и 3 проводят, а транзисторы 2 и k закрыты. На выходной шине 5 устанавливается уровень напряжения логического3101 На третьем наборе, когда А 1, В 1, R О, В 0 транзисторы 1 и проводят, а транзисторы 2 и 3 закрыты. На выходной шине 5 устанавлива .ется уровень напряжения логической 1. Следовательно, элемент выполняет функцию равнозначностио Принцип работы логического элемента проиллострнрован с помощью таблицы истинности, которая дополнена таблицей состряШ транзисторов, входящих в логический элемент, в табл. 1 низкому и высокому уровню сигналов соответствует О и М, знаки Лг и 3 соответствуют состояниям транзисторов, когда они проводят (П: J и когда закрыты (З}. В данном элементе входные емкости I по каждому входу равны и включают емкостьлегировадаой области (истока.. 04 одного транзистора и емкост затвора одного транзистора. Если обозмачить Сд и С соответственно емкость легированной области и ёмкость затвора, транзистора, то по каждому Bxcifly , С Са в прототипе по входу А С ЯСд + 2С : Следовательно, дачный элемент по зволяет в 2 paSa уменьшить входные емкости, что, в конечном счете, приводит к повышению быст(х действия устройства, а котором, используется данный элементов 1,5-2 . В табл. 2 представлены результаты сравнения Тзфизвестного элемента |схема t) и предложенного логического элемента Ссхема 2) для . ных технологий при переключении сиг-. налов из 1 в О и из О в 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1981 |

|

SU997252A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Логический элемент на КМДП-транзисторах | 1985 |

|

SU1262721A1 |

| Многофункциональный логический элемент | 1982 |

|

SU1016841A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| ЛОГИЧЕСКОЕ (МНОГОФУНКЦИОНАЛЬНОЕ) УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2081509C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Триггер на взаимодополняющих мдп-транзисторах | 1980 |

|

SU875596A1 |

| Устройство задержки импульсов | 1977 |

|

SU680163A1 |

t а б ли

..-

Л,43 13,20 10,00 13,0 2,50

|2,80

1,19 |3,63 1,67

П79 1,55

i

1,61

Продолжение табл. 2

3,39

1 О О 13,80

13,10

1,25 0,72 3,32 0,96 2,97 2,1i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Валиев К.А | |||

| и др | |||

| Цифровые интегральные схемы на МДП-транзисtopax | |||

| М., Советское радио, Т971, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

Авторы

Даты

1983-05-15—Публикация

1982-01-07—Подача