(54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ Изобретение относится к вычислительной техни.кву электронике, автоматике и, в частности, может быть использовано при разработке БИС на дополняняцих МДП-транзисторах. Известен логический элемент, содержащий пару п-канальных транзисторов с перекрестно соединенными стока ми и затворами, три р-канальных тран.зистора и инвертор, при этом первый р-канальный транзистор подключен параллельно первому п-канальному.транзистору, а второй и третий р-канальные транзисторы последовательно включены между шиной питания и истоками п-канальнйх транзисторов, подключенными к выходной шине, затвор первого р-канального транзистора подключен ;к выходу инвертора, затворы первого п-канальн.ого и третьего р-чанального транзисторов подключены К входу инвертора и к первой входной шине, а за творы второго р-канальнЗго и В5вр8Р8 п-канального транзисторов подключены ко второй входной . Недостатком известного устройства является реализация на выходе только одной функции, низкое быстродействие, а также то, что оно выполнено н большом числе МДП-транзисторов. Известен также логический элемент, выполненный на меньшем числе НДП-транзисторов и содержащий пару п-канальных транзисторов с перекрестно соединенными стоками и затворами, пару р-канальных транзисторов и инвертор, вход которого подключен к первой входной шине и к затвору первого пканального транзистора, а выход - к затвору первого р-канального транзистора, подключенного параллельно первому п-канальному транзистору, и к истоку второго р-канального транзистора, затвор которого подключен ко второй входной шине и к затвору второго п-канальногоI транзистора, а сток - к выходной шине и к истокам п-канальных транзисторов 2J . Недостатком известного логического эл&лекта является реализация на Выходе только одной функции, а также низкое быстродействие, обусловленное .подключением к выходной шине четырех транзисторов. Цель изобретения - расширение функциональных возможностей элемента и повышение его быстродействия. Цель достигается тем, что в логический элемент, содержащий пару

-канальных транзисторов с перекрест о соединенными стоками и затворами пару р-канальных транзисторов, ведена вторая пара р-канальйых ранзисторов, при этом истоки панальных транзисторов подключены к бщей шине,р-канальные транзисторы первой пары последовательно включены между первой и второй выходными шинами, подключенными, соответственно, к стоку первого и второго п-каналь- JQ ных транзисторов, затворы первого и второго р-канальных транзисторов первой пары подключены соответственно к первой, и второй входным шинам, первый р-канальный транзистор второй пары подключен между первой входной 5 шиной и.первой выходной, а второй между второй входной шиной и второй выходной ,з.а1воры р-канальных транзисторов второй пары подключены к третьей входной шине, к истоку пер- , 20 вого р-канального транзистора первой пары и к стоку второго р-канального транзистора этой же пары.

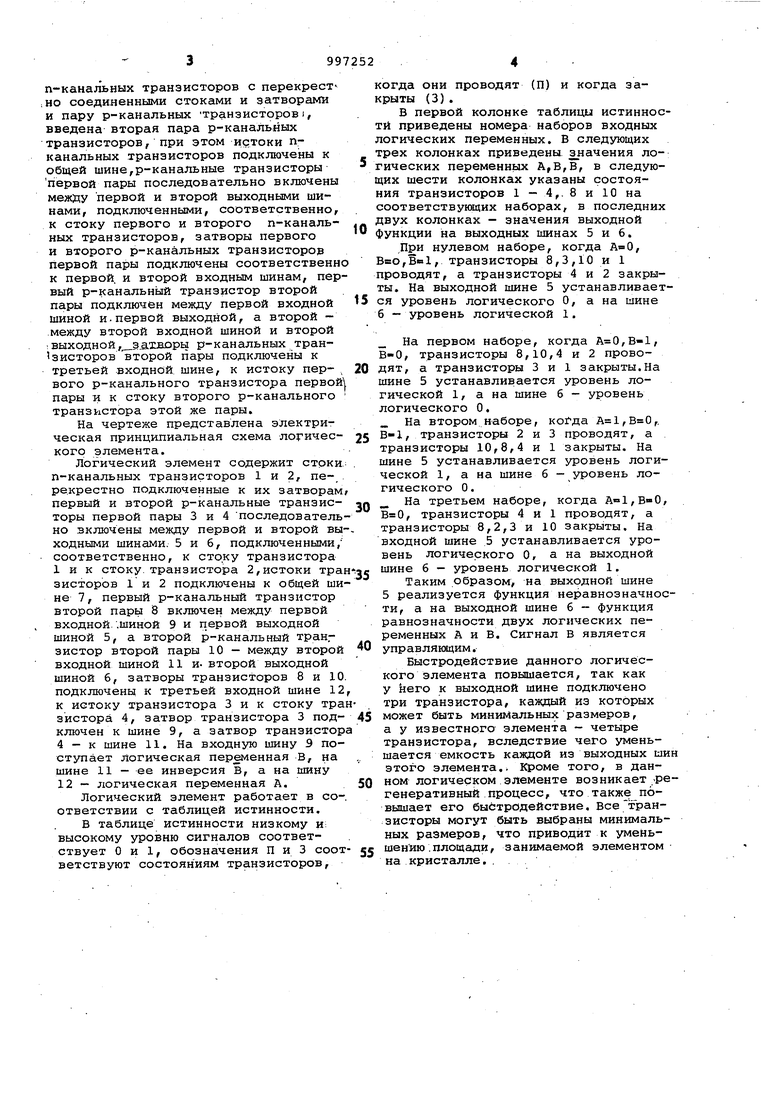

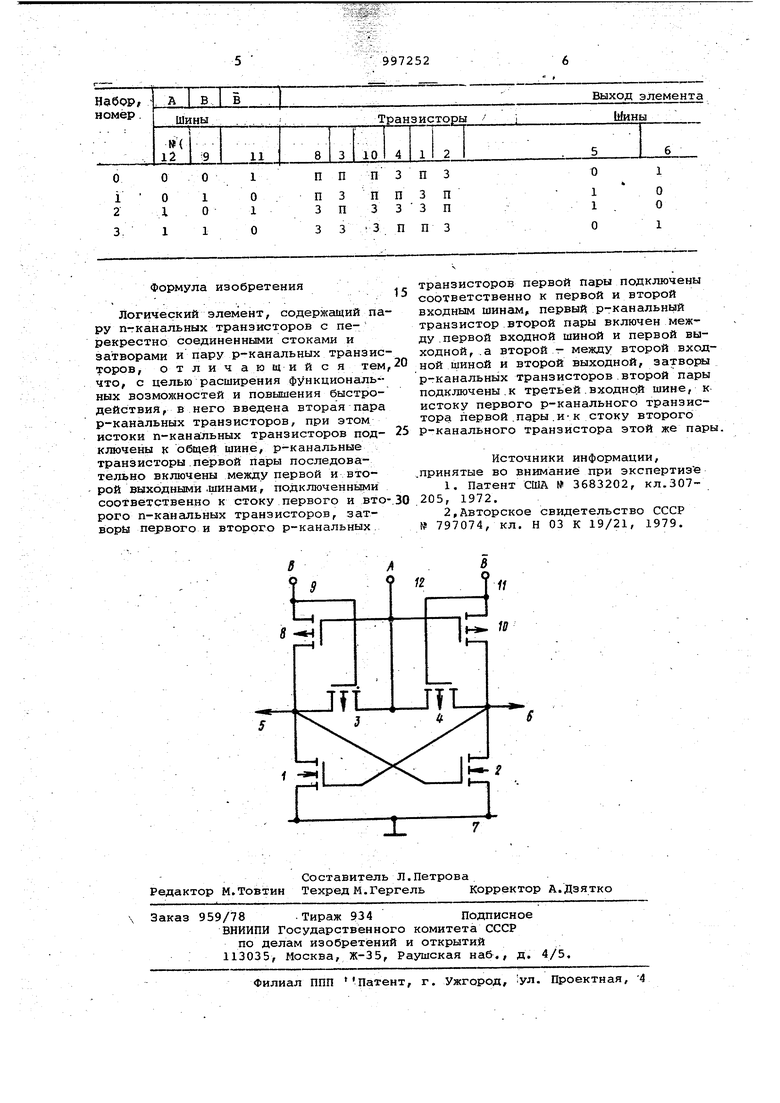

На чертеже представлена электрическая принципиальная схема логичес- 25 кого элемента.

Логический элемент содержит стоки.; п-канальных транзисторов 1 и 2, перекрестно подключенные к их затворам/ первый и второй р-канальные транзис- я торы первой пары 3 и 4 последовательно включены между первой и второй вы-ходными шинами. 5 и б, подключенными/ соответственно, к стоку транзистора 1 и к стоку, транзистора 2,истоки тран ас зисторов 1 и 2 подключены к общей шине 7, первый р-канальный транзистор второй пары 8 включен между первой входной, .шиной 9 и первой выходной шиной 5, а второй р-канальный тран,зистор второй пары 10 - между второй входной шиной 11 и- второй выходной шиной 6, затворы транзисторов 8 и 10. подключены к третьей входной шине 12, к истоку транзистора 3 и к стоку транзистора 4, затвор транзистора 3 под- 45 ключен к шине 9, а затвор транзистора 4 - к шине 11. На входную шину 9 поступает Логическая переменная В, на шине 11 - ее инверсия В, а на шину 12 - логическая переменная А, 50

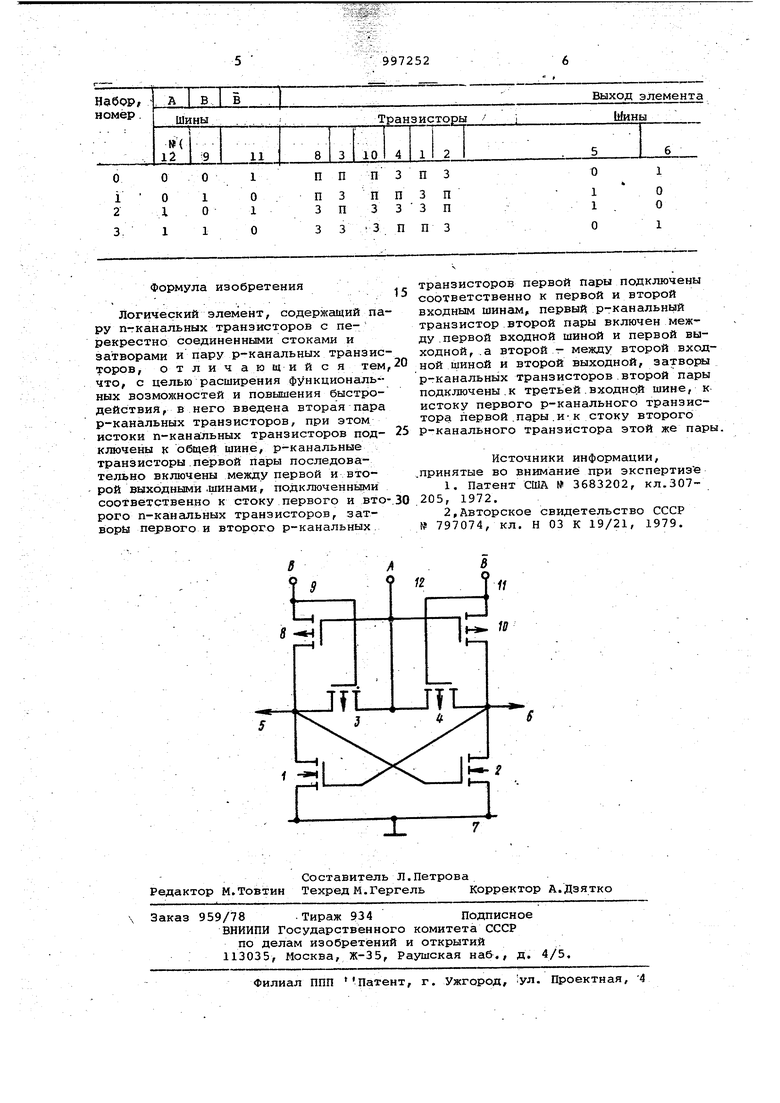

Логический элемент работает в со-. ответствии с таблицей истинности.

В таблице истинности низкому к. высокому уровню сигналов соответствует О и 1, обозначения П и 3 соот- 55 ветствуют состояниям транзисторов.

когда они проводят (П) и когда закрыты (3) .

В первой колонке таблицы истинности приведены номера наборов входных логических переменных. В следующих трех колонках приведены значения логических переменных А,В,В, в следующих шести колонках указаны состояния транзисторов 1 - 4,. 8 и 10 на соответствунвдих наборах, в последних двух колонках - значения выходной функции на выходных шинах 5 и 6.

,При нулевом наборе, когда , ,Вв1, транзисторы 8,3,10 и 1 проводят, а транзисторы 4 и 2 закрыты. На выходной шине 5 устанавливаеся уровень логического О, а на шине б - уровень логической 1.

На первом наборе, когда ,В-1, В-0, транзисторы 8,10,4 и 2 проводят, а транзисторы 3 и 1 закрыты.На шине 5 устанавливается уровень логической 1, а на шине б - уровень логического О.

На втором наборе, коГда ,,. В-1, транзисторы 2 и 3 проводят, а транзисторы 10,8,4 и 1 закрыты. На шине 5 устанавливается уровень логической 1, а на шине б - уровень логического О.

, На третьем наборе, когда ,В-0 , транзисторы 4 и 1 проводят, а транзисторы 8,2,3 и 10 закрыты. На входной шине 5 устанавливается уровень логического О, а на выходной шине б - уровень логической 1.

Таким образом, на выходной шине 5 реализуется функция неравнозначноти, а на выходной шине б - функция равнозначности двух логических переменных А и В. Сигнал В является управляющим.

Быстродействие данного логического элемента повышается, так как у него к выходной шине подключено три транзистора, каждый из которых может быть минимальных размеров, а у известного элемента - четыре транзистора, вследствие чего уменьшается емкость каждой из выходных ш этого элемента.. Кроме того, в данном логическом элементе возникает ргенеративный процесс, что также повышает его быстродействие. Все транзисторы могут быть выбраны минимальных размеров, что приводит к умеНьшению . площади, занимаемой элементомна кристалле..

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Логический элемент | 1982 |

|

SU1018250A1 |

| Логический элемент и-не | 1977 |

|

SU656213A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ УРОВНЯ СИГНАЛА В СХЕМАХ С ПРОГРАММИРУЕМОЙ КОММУТАЦИЕЙ | 2011 |

|

RU2469472C1 |

| Логический элемент или-не | 1977 |

|

SU656214A1 |

Авторы

Даты

1983-02-15—Публикация

1981-07-13—Подача