1

Изобретение относится к области запоминающих устройств.

Известно оперативное запоминающее устройство (ОЗУ), содержащее блок памяти, к которому подключены выходы дешифратора (входы дешифратора соединены с выходами датчика адреса кода), регистры числа, подключенные соответственно к входу и выходу блока памяти, выходы регистров числа, подсоединенные к входам блока обнаружения неисправных ячеек памяти.

Однако такие устройства сложны и недостаточно надежны в работе.

Предложенное устройство отличается от известного тем, что выход блока обнаружения неисправных ячеек памяти подключен к входу датчика кода адреса.

Это позволяет упростить устройство и повысить его падежность.

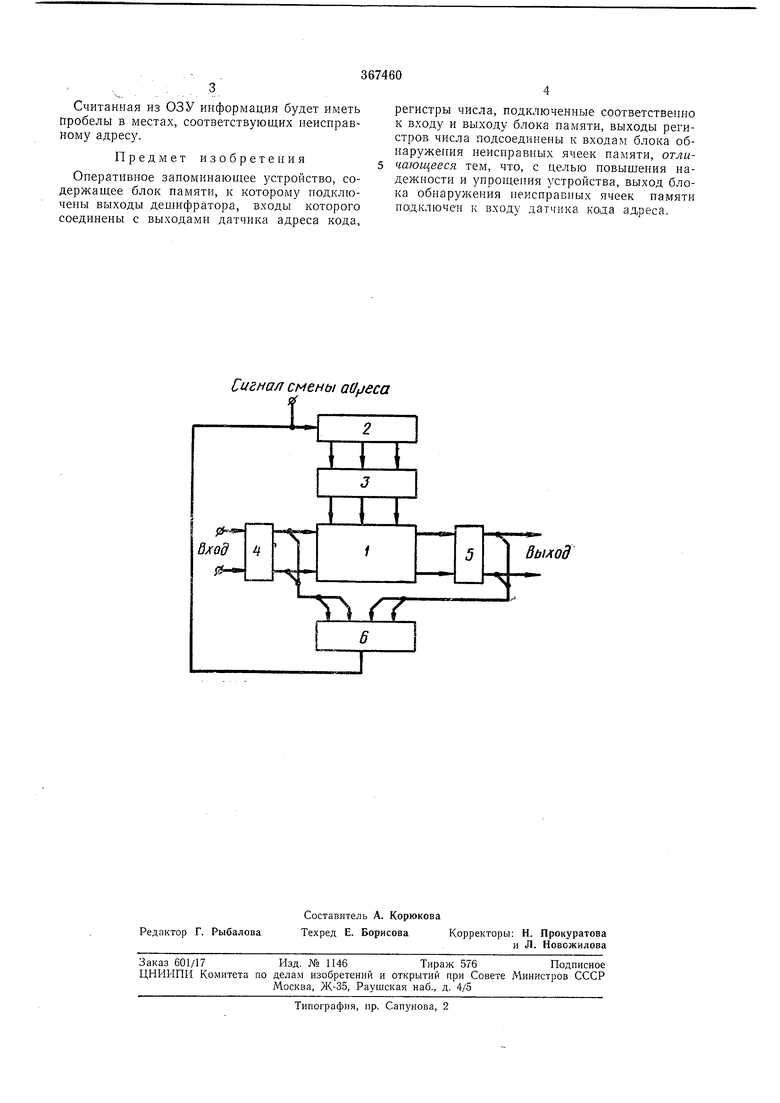

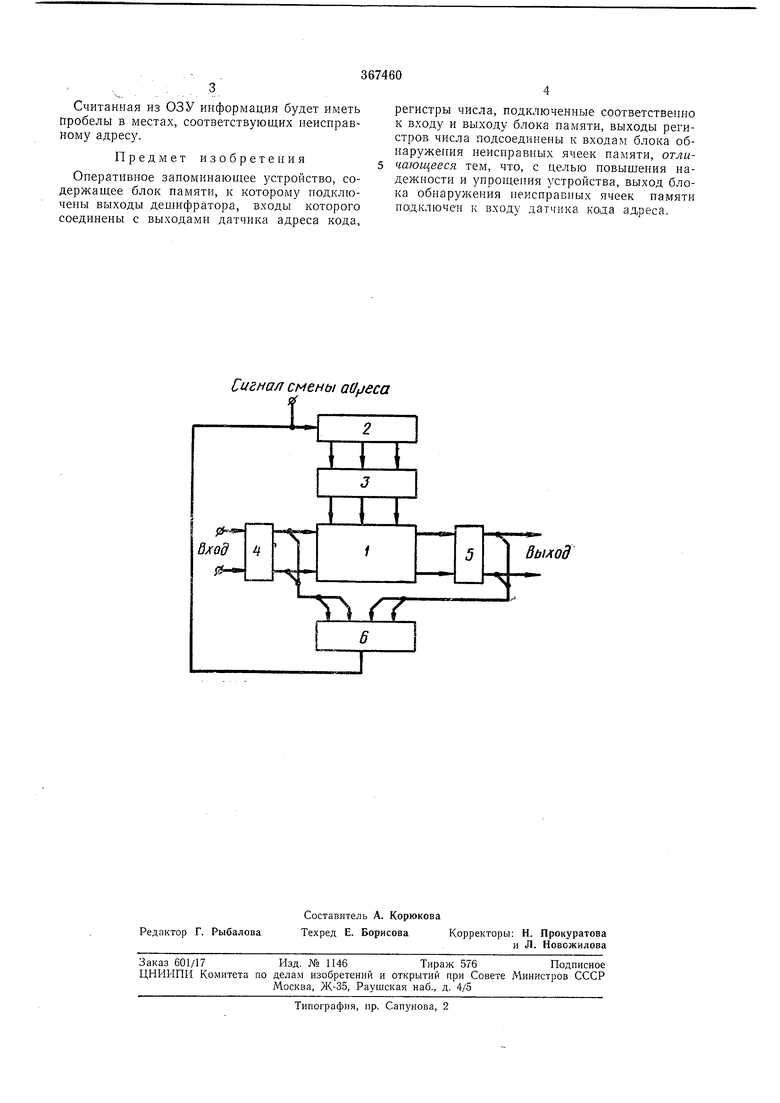

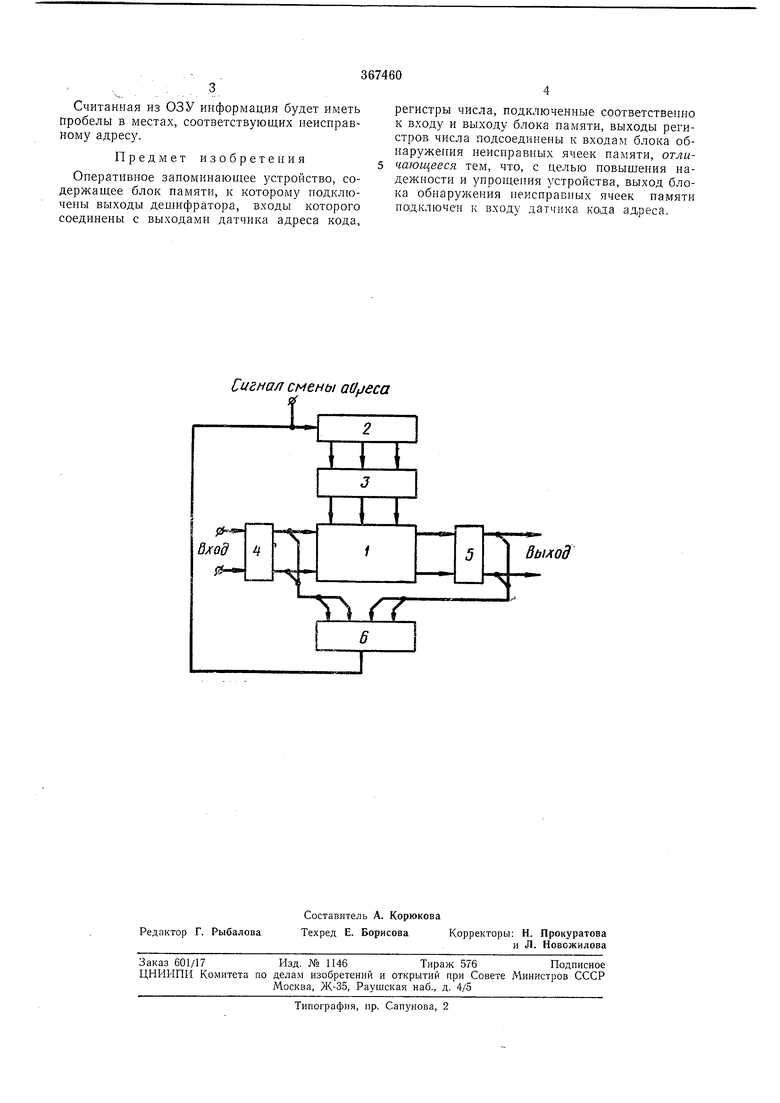

На чертеже показана блок-схема предложенного устройства.

Устройство содержит блок / памяти, датчик 2 кода адреса, к выходам которого подключены входы дешифратора 3, регистры 4 ti 5 числа, связанные соответственно с входом и выходом блока / памяти. Выходы регистров 4 и 5 подсоединены к входам блока 6 обнаружения неисправных ячеек памяти, выход которого подключен к-входу датчика 2 кода адреса.

Устройство работает следующим образом. При вводе информации в запоминающее устройство происходит двойное обращение к блоку памяти по выбранному адресу. При

первом обращении записывается вводимое число с регистра 4 в блок памяти /. При повторном обращении это число считывается и записывается на регистр 5. Блок 6 обнаружения неисправности сравнивает код па регистре 4 с кодом на регистре 5.

Если коды совпадают, код с регистра 4 вводится в блок памяти. Далее обращение осуществляется к последующему адресу.

В случае несовпадения кодов на регистрах

4 и 5, что свидетельствует о неисправности в выбранном адресе, блок обнаружения неисправности выдает сигнал, поступающий на вход датчика 2 кода адреса, в результате чего происходит смена адреса и обращение ведется к следующей по счету ячейке. Запись информации по новому адресу осуществляется в последовательности, изложенной выше.

Таким образом, в предложенном запоминающем устройстве каждая носледующая ячейка блока памяти является как бы резервной по отношению к предыдущей ячейке. Работа устройства не нарушается и в том случае, если две соседние ячейки откажут, обращение осуществляется к следующей третьей

ячейке и т. д.

Считанная из ОЗУ информация будет иметь Пробелы в местах, соответствующих неисправному адресу.

Предмет изобретения

Онеративное запоминающее устройство, содержащее блок памяти, к которому подключены выходы дешифратора, входы которого соединены с выходами датчика адреса кода,

регистры числа, подключенные соответственно к входу и выходу блока намяти, выходы регистров числа подсоединены к входам блока обнаружения неисправных ячеек памяти, отличающееся тем, что, с целью повышения надежности и упрощения устройства, выход блока обнаружения неисправных ячеек памяти подключен к входу датчика кода адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU262181A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841061A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

Сигнал смены

Авторы

Даты

1973-01-01—Публикация