ций первого регистра микрокоманд соединен с первым входом первого блока элементов ИЛИ, группа выходов которого является первым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго р1егистров микрокоманд соединены ,с .первыми информационнь1ми входами соответственно первого и второго коммутаторов адреса, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен с входом первого одновибратора, отличающеес тем, что, с целью повьшения быстродействия, устройство дополнительно содержит третий блок памяти микрокоманд, третий регистр микрокоманд седьмой, восьмой, девятьй, десятый одиннадцатый, двенадцать и тринадцатый элементы ИЛИ, второй блок эле ментов ИЛИ, первый и -второй блоки элементов И, второй, третий и четвертый одновибд)аторы, причем второй вход логических условий устройства соединен с вторым входом второго формирователя адреса, входы меток, управления синхронизацией первой и второй групп входов кода опера.ции устройства соединены соответственно с первым и вторым синхронизируемым входом блока синхронй зации, выход которого соединен с установочными входами первого, второго и третьего регистров микрокоманд, выход конца работы группы выходов, первого блока элементов ИЛИ соединен с вторым входом второго элемента ИЛИ, выход конца работы- группы выходов второго блока элементов ИЛИ соединен с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входом второго триггера пуска, выход первого Элемента И соединен с вторым входом шестого элемента ИЛИ и является выходом ошибки устройства, вторая группа входов входа кода операции устройства соединена с входом треть его элемента ИЛИ, выходы полей адреса первого и второго регистров .адреса соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединение входом третьего блока памяти микрокоманд, выход третье 10 го блока памяти микрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы полей адреса, кода логических условий и модифицируемого разряда адреса которого соединены с вторыми информационными входами первого и второго коммутаторов адреса, выход поля микрооперации третьего регистра микрокоманд соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с вторым входом первого блока элементов ИЛИ и с первым входом второго блока элементов ИЛИ, группа выходов второго блока элементов ИЛИ является вторым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены соответственно с входамиГ седьмого и восьмого элементов, ИЛИ, выходы которых соединены соответственно с прямыми входами второго и третьего элементов И, вы- ход третьего элемента И соединен с входом второго одновибратора, первый выход которого соединен с первым входом девятого элемента ИЛИ, второй выход второго одновибратора соединен с первыми входами пятого и десятого элементов ИЛИ,первьЙ1 выход первого одновибратора соединен с первым входом одиннадцатого элемента ИЛИ, второй выход первого одновибратора соединен с первыми входами четвертого и двенадцатого элементов ИЛИ, единичный выход первого триггера пуска соединен, с первым входом тринадцатого элемента ИЛИ, выход которого соединен с вторым входом пуска блока синхронизации и с нулевыми входами первого и второго триггеров управления, единичный выход второго триггера пуска соединен с вторьм входом тринадцато,го элемента ИЛИ, с третьим входом пуска блока синхронизации, выход поля метки управления синхронизацией первого регистра адреса соединен. с вторыми входами четвертого,одиннадцатого , двенадцатого элементов ИЛИ, выход поля метки управения синхронизацией второго регистра адреса соединен с вторыми входами пятого, девятого, десятого элементон ИЛИ, выход девятого элемента ИЛИ

соединен с первым входом первого элемента И и первым управляющим входом коммутатора, выход одиннадцатого элемента ИЛИ соединен с вторым входом первого элемента И и вторым управляющим входом коммутатора, первый и второй выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого и второго регистров адреса, третий ,четвертый, пятый выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего регистров микрокоманд, выход поля метки управления синхронизацией первого регистра микрокоманд соединен с инверсным входом второго элемента И, с первым входом четвертого элемента И, со счетным входом первого триггера управления и с первым входом разрешения выработки тактовых импульсов группы входов блока синхронизации, единичный и нулевой выходы первого триггера управления соединены соответственно с . вторым и третьим входами группы входов блока синхронизации, выход поля -метки управления синхронизацией второго регистра микрокоманд соединен с инверсным входом третьего элемента И, с вторым входом четвертого элемента И, со счетным входо второго триггера управления и с четвертым входом группЬ входов

10

1

блока син: ронизации, единичный и нулевой выходы второго триггера управления соединены соответственно с пятым и шестым входами группы входов бло.ка синхронизации, выход четвертого элемента И соединен с седьмым входом группы входов блока синхронизации, выход поля первой метки управления синхронизацией третьего регистра микрокоманд соединен с первым входом пятого элемента И и с прямым входом шестого элемента И, выход которого соединен с входом третьего одновибратора и с вторым входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход поля второй метки управления синхронизацией третьего регистра микрокоманд соединен с инверсным входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с входом четвертого одновибратора и с третьим входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход третьего одновибратора соединен с третьими входами пятого и десятого элементов ШШ, выход четвертого одновибратора соединен с третьими входами четвертого и двенадцатого элементов ИЛИ, выходы десятого и двенадцатого элементов ИЛИ соединены соответственно с вторыми входами первого и второго блоков элементов

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первьй и второй регистры адреса, первый и второй регистры микрокоманд, первый и второй формирователи адреса, первый и второй коммутаторы адреса, коммутатор, первый одновибратор, первый и второй триггеры пуска, первьй и второй триггеры управления, блок синхронизации, первый, второй, третий, четвертый, пятый, шестой элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой элементы И, первый блок элементов ИЛИ, первая группа входов кода операции устройства соединена с первым информационным входом первого регистра адреса и с входом первого элемента ИЛИ, выход которого соединен с единичным входом -первого триггера пуска, выход второго элемента ИЛИ соединен с нулевым входом первого триггера пуска, единичный выход которого соединен с первым входом пуска блока синхронизации, выход третьего элемента ИЛИ соединен с единичным входом второго триггера пуска, вторая группа входов кода операции устройства соединена с первым информационным входом второго регистра адреса, первый вход логических условий устройства соединен с первым входом первого формирователя адреса, выход которого соединен с вторым информационным входом первого регистра адреса, выход четвертого элемента ИЛИ соединен с прямым и инверсным управляншщми входами первого коммутатора адреса, выходы кода логических условий и немодифи(Л цируемых раэрядов адреса которого. соединены соответственно с вторым входом первого формирователя адреса и третьим информационным входом первого регистра адреса, выход второго формирователя адреса соединен с вторым информационным входом второго регистра алреса, выход пятого элемента ИЛИ соединен с пря05 Од мым и инверсным управляющими входами второго коммутатора адреса, выходы кода логических условий 4i немодифицируемых разрядов которого соединены соответственно с первым входом второго формирователя адреса, и третьим информационным входом второго формирователя адреса, выхода полей адреса первого и второго регистров адреса соединены соответственно с входами первого к второго блоков памяти микрокоманд , выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд, вькод поля микроопера

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке микропрограммных устройств управления параллельных вычислительных и управляющих систем,,

ИЗВЕСТНЫ микропрограммные устройства управления, содержащие первый и второй блоки памяти микрокоманд, регистры микрокоманд и адреса,формирователи адреса, триггеры, элементы И l и 2 .

Недостатками указанных устройств являются низкая производительность и узкая область применения, обусловлен

ные невозможностью управления параллельными процессами.

Известно также микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй коммутаторы блок синхронизации, первый и второй триггеры управления, элементы И, ИЛИ З.

Недостатками данного устройства являются кизкай производительность, обусловленная отсутствием технических средств для управления параллел ными процессами и перетактовкой

устройства при последовательном выполнении, двух четных (нечетных) микрокоманд, а также низкая достоверность функционирования.

Наиболее близким к изобретению по технической сущности и достигаемому результату является микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй регистры микрокоманд, первый и второй коммутаторы, формирователь такгтовых импульсов, первый и второй формирователи адреса, первый и второй триггеры управления, первьй и второй элементы И, блок эдемен- тов Р1ПИ, схема сравнения, третий, четвертый и пять1й триггеры управления, третий и четвертьй коммутаторы.третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый второй, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, первый и второй элементы И-НЕ и одновиб ратор, причем входы логических условий устройства соединены с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми вхо. дами соответственно первого и второг регистров адреса, вход кода операции устройства соединен с вторыми информационными входами первого и второго регистров адреса, выходы которых соединены с информационными входами соответственно первого и второго блоков памяти микрокоманд, выходы пе вого и второго элементов И соединены с управляющими входами соответственно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регистров микрокоманд, первые управляющие выходы первого и второго регистров микройоманд соединены с единичными входам соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, выход адреса первого регистра микрокоманд соединен с первыми информационными входами первого и второго коммутаторов, выход адреса второго

регистра микрокоманд соединен с вторь1ми информационными входами первого и второго коммутаторов, выходы которых соединены с вторыми информационными входами соответственно первого и второго формирователей адреса, вход кода операции устройства через первый элемент ИЛИ соединен с единичным входом третьего триггера управления, единичный выход которого соединен с входом формирователя тактовых импульсов, первый выход формирователя тактовых импульсов соединен с нулевыми входами триггеров полей микроопераций первого и второго регистров микрокоманд и с первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с первыми входами соответственно первого и второго элементов И, второй и третий выходы формирователя тактовых импульсов соединены Соответственно с вторыми и третьими информационными входами третьего и четвертого коммутаторов, единичньй выход четвертого триггера управления соединен с первыми управлякяцими входами третьего и четвертого коммутаторов, первыми входами третьего, четвертого и пятого элементов И,первого и второго элементов И-НЕ,. выходы которых соединены с вторыми входами соответственно первого и второго элементов И,

второй управляющий выход первого регистра микрокоманд соединен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управлякнцим входом первого коммутатора, второй управля(ощий выхо второго .регистра микрокоманд соединен с первым входом четвертого и вторым входом второго элемента ИЛИ, выход которого соединен с Т-входом пятого триггера управления, единичньй зыход которого соединен с вторыми управляющими входами третьего и четвертого коммутаторов, нулевой выход пятого триггера соединен с трет.ьими управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд через пятый элемент ИЛИ соединены с единичным входом четвертого триггера управлени нулевой выход которого соединен с вторым управляющим входом первого

.коммутатора и первым управляющим 5 входом второго коммутатора, нулевые выходы первого и второго триггеров управления соединены с вторыми входами соответственно третьего и пятого элементов И, выходы которых соединены с вторыми входами соответ ственно третьего и .четвертого элементов ИЛИ, выход которого соединен с вторь м управляющ входом второго коммутатора, третьи управляющие вхо ды первого и второго регистров микр команд соединены с третьими управляющими входами соответственно первого и второго коммутаторов, единич ньй выход первого триггера управления соединен с вторым входом первог элемента И-НЕ и первым входом шестого элемента И, единичный выход второго триггера управления соединен с вторым входом второго элемента И-НЕ и вторым входом шестого эле мента И, выход которого соединен с первыми входами седьмого и восьмого элементов И и через одновибратор с нулевыми входами первого, второго и четвертого триггеров управления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверс ный выходы которой соединены с вторыми входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ, выход восьмого элемента И соединен с первыми входами шестого и седьмого элементов ШТИ, выходы которых соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конца операции блока элементов ИЛИ сое динен с вторыми входами шестого эле мента ИЛИ и четвертого элемента И, выход которого соединен с входом седьмого элемента ИЛИ 4j . Недостатками известного устройства являются большой объем оборудования, вызванный избыточностью блоков памяти, и низкое быстродействие при реализации параллельных микроподпрограмм, обусловленное перестройкой устройства в одноплечеву структуру. Большой объем оборудования, вызванный избыточностью блоков памяти устройства, обусловлен двумя причинами: избыточностью блоков па- 106 . |мяти каждого плеча устройства из-за хранения многократно повторяющееся микроподпрограмм, выполняемых в последовательном и параллельном режимах для управления одним объектом (горизонтальная избыточность) и избыточностью блоков памяти устройства, которая вызвана большим количеством идентичных микроподпрограмм для управления параллельными каналами, хранимых в блоках памяти (вертикальная избыточность) . В последовательном режиме функционирования устройство представляет собой двухплечевую структуру в которой обращение к двум блокам памяти производится за счет двух последовательностей тактовых импульсов сдвинутых один относительно другого. Период следования тактовых импульсов устройства в данном режиме равен to. При переходе в параллельньй режим устройство перестраивается в одноплечевую структуру и период следования тактовых импульсов устройства становится равным 2to,что и обуславливает низкое быстродействие. I Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в параллельное микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй регистры микрокоманд, первый и второй формирователи адреса,первый и второй рой коммутаторы адреса, коммутатор, первый одновибратор, первый и второй триггеры пуска, первый и второй триггеры управления, блок синхронизации, первый, второй, третий, четвертьй, пятый, тестой элементы ИЛИ, первый, второй,, третий, четвертый, пятый, шестой элементы И, первьм блок элементов ИЛИ, причем первая группа входов кода операции устройства соединена с первым информационным входом первого регистра адреса и с входом первого элемента ИЛИ, выход которого соединен с единичным входом первого триггера пуска, выход второго элемента ШТИ соединен с нулевым входом первого триггера пуска, единичный выход которого соединен с первьм входом пуска блока синхронизация, выход третьего элемента ИЛИ соединен с 7 . единичным входом второго триггера пуска, .вторая группа входов кода операции устройства соединена с первым информационным входом второг регистра адреса,первый вход логичес ких условий устройства соединен с первым входом первого формирователя адреса, выход которого соединен с вторым информационным входом первого регистра адреса, выход четвертого элемента ИЛИ соединен с прямым н инверсным управляющими входами первого коммутатора адреса, выходы кода логических условий и немодифицируемых разрядов адреса которо го соединены соответственно с вторы входом первого формирователя адреса и третьим информационным входом первого регистра адреса, выход второго формирователя адреса соединен с вторым информационным входом второго регистра адреса, выход пятого элемента ИЛИ соединен с прямым и инверсным управляющими входами второго коммутатора адреса, выходы код логических условий и немодифихщруемых разрядов адреса которого соединены соответственно с первым входом второго формирователя адреса и третьим информационным входом второго формирователя адреса, выходы полей адреса первого и второго регистров адреса соединены соответственно -с входами первого и второго блоков памяти микрокоманд, выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд,выход поля микроопераций первого регистр микрокоманд соединен с первым входом первого блока элементов Р1ПИ, группа выходов которого является пе вым выходом микроопераций устройств выходы полей адреса, кода логически условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены с первыми ( информационными входами соответственно первого и второго коммутаторов адреса, выход первого элемен та И соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен с входом первого одновибратора, дополнительно введен третий блок памяти микрокоманд, третий регистр микрокоманд, седьмой, восьмой, девятый, десятый одиннадцать, двенадцатый и тринад 10 ,.8 цатый элементы ИЛИ, второй блок элементов ИЛИ, первьй и второй блоки элементов И, второй, третий и четвертый одновибра торы, причем второй вход Логических условий устройства соединен с вторым входом второго формирователя адреса, входы меток управления синхронизацией первой и второй групп входов кода операции устройства соединены соответственно с первым и вторым синхронизируемым входом блока синхронизации, выход которого соединен с установочными входами первого, второго и третьего регистров микрокоманд, выход конца работы группы выходов первого блока элементов РШИ соединен с вторым входом второго элемента ИЛИ, выход конца работы группы выходов второго. блока элементов ИЛИ соединен с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входбм второго триггера пуска, выход первого элемента И соединен с вторым входом шестого элемента ИЛИ и является выходом ошибки устройства, вторая группа входов входа кода операции устройства соединена с входом третьего элемента ИЛИ, выходы полей адреса первого и второго регистров адреса соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с входом третьего блока памяти микрокоманд, выход третьего блока памяти микрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы полей адреса, коды логических условий и модифицируемого разряда адреса которого соединены с вторыми информационными входами первого и второго комму таторов адреса, вьпсод поля микроопераций третьего регистра микрокоманд, соединен с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с вторым входом первого блока элементов ИЛИ и с первым входом второго блока элементов ИЛИ, группа выходов второго блока элементов ИЛИ является вторым выходом микроопераций устройства, выходы полей адреса, кода логических условий и модифицируемого разряда адреса первого и второго регистров микрокоманд соединены соответственно с входами сельмого и восьмого элеме тов ИЛИ, выходы которых соединены соответственно с прямыми входами второго и третьего элементов И, выход третьего элемента И соединен с входом второго одновибратора, пер вый выход которого соединен с первы входом девятого элемента ИЛИ, второй выход второго одновибратора сое динен с первь1ми входами пятого и де сятого элементов ИЛИ, первьй выход первого одновибратора соединен с первым входом одиннадцатого ,элемента ИЛИ, второй выход первого однови ратора соединен с первыми входами четвертого и двенадцатого элементов ШШ, единичный выход первого триггера пуска соединен с первым входом тринадцатого элемента ИЛИ, выход ко торого соединен с вторым входом пуска блока синхронизации и с нулевым входами первого и второго триггеров управления,единичный выход второго триггера пуска соединен с вторым входом тринадцатого элемента ИЛИ, с третьим входом пуска блок синхронизации, выход поля метки управления синхронизацией первого регистра адреса соединен с вторыми входами четвертого, одиннадцатого, двенадцатого элементов ИЛИ, выход поля метки управления синхронизацией второго регистра адреса соединен с вторымиВходами пятого, девятого, десятого элементов ИЛИ, выход девятого элемента ИЛИ соединён с первым входом первого элемента И и первым управляющим входом коммутатора, выход одиннадцатого элемента ИЛИ соединен с вторым входом первого элемента И и вторым управляющим входом коммутатора, .первый и второй выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого и второго регистров адреса, третий, четвертый, пятый выходы группы выходов блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего регистров микрокоманд, выход поля мет управления синхронизацией первого регистра микрокоманд соединен с инверсным входом второго элемента И, с первым входом четвертого элемента И, со счетным входом первого триггера управления и с первым входом разрешения выработки тактовы импульсов группы входов блок синхронизации, единичньй и нулевой вы ходы первого триггера управления соединены соответственно.с вторым и третьим входами группы входов блока синхронизации, выход поля метки управления синхронизацией второго регистра.микрокоманд соединен с инверсным входом третьего элемента И, с вторым входом четвертого элемента И, со счетным входом второго триггера управления и с четвертым входом группы входов блока синхронизации, единичный и нулевой выходы второго триггера управления соединены соответственно с пятым и шестым входами группы входов блока синхронизации, выход четвертого элемента И соединен с седьмым входом группы входов блока с.инхронизации, выход поля первой метки управления синхронизацией третьего регистра микрокоманд соединен с первым входом пятого элемента И и с прямым входом шестого элемента И, выход которого соединен с входом третьего одновибратора и с вторым входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход поля второй метки управления синхронизацией третьего регистра микрокоманд соединен с инверсным входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с входом четвертого одновибратора и третьим входом разрешения выработки тактовых импульсов группы входов блока синхронизации, выход третьего одновибратора соединен с третьими входами пятого и десятого элементов ШШ, выход четвертого одновибратора соединен с третьими входами четвертого и двенадцатого элементов ИЛИ, выходы десяГтогб и двенадцатого элементов ШШ соединены соответственно с вторыми входами первого и второго блоков элементов И. Сущность изобретения состоит в повьштении быстродействия устройства за счет введения специального блока памяти,в котором бесповторно хранятся микроподпрограммы и который позволяет сохранить двуплечевую структуру устройства для каждого объекта управления в параллельном ежиме функционирования.

11

Введение третьего блока памяти микрокоманд, третьего регистра микрокоманд, седьмого, восьмого, девятого, одиннадцатого и тринадцатого элементов ИЛИ и обусловленных ими связей позволяет обеспечивать двуплечевую структуру устройства для каждого объекта -управления .. Введение десятого и двенадцатого элементов ИЛИ, второго, третьего и четвёртого блоков элементов ИЛИ и обусловленных ими связей позволяет обеспечить выдачу сигналов микроопераций, считьшаемы Из третьего блока памяти микрокоманд, попеременно на два объекта управления.

Введение третьего и четвертого одновибраторов и обусловленных ими связей позволяет обеспечить считывание подряд двух четных (нечетных микрокоманд из третьего блока памя микрокоманд при управлении одним объектом..

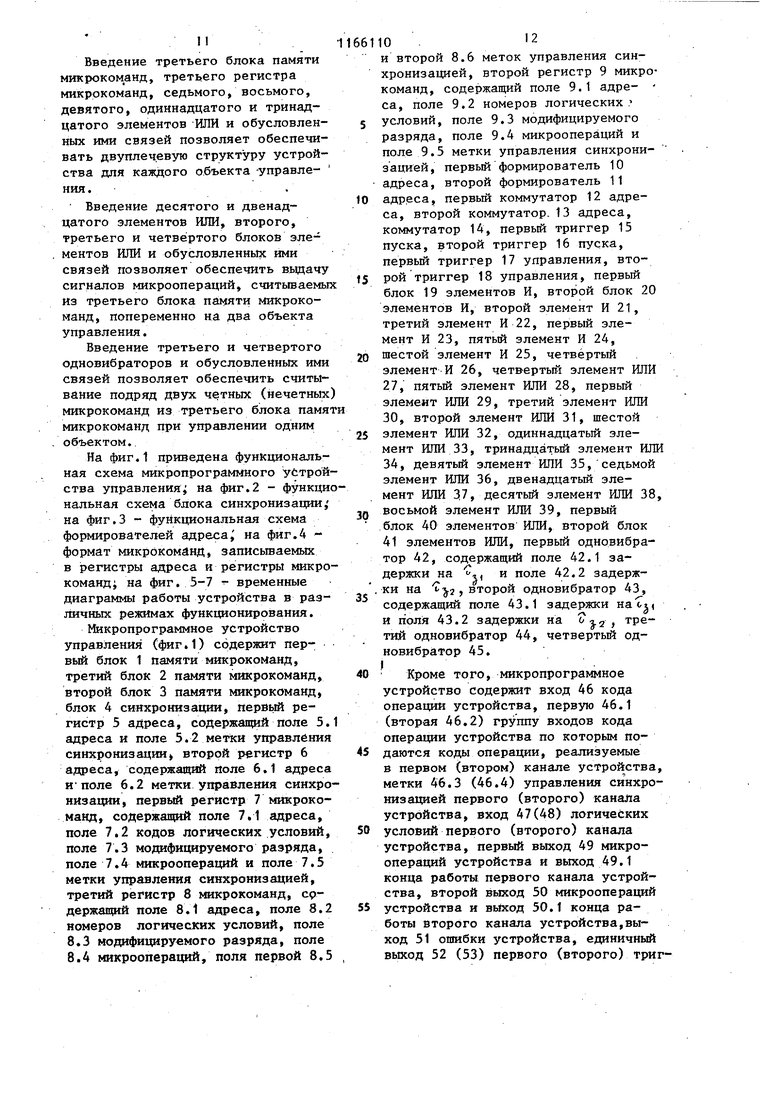

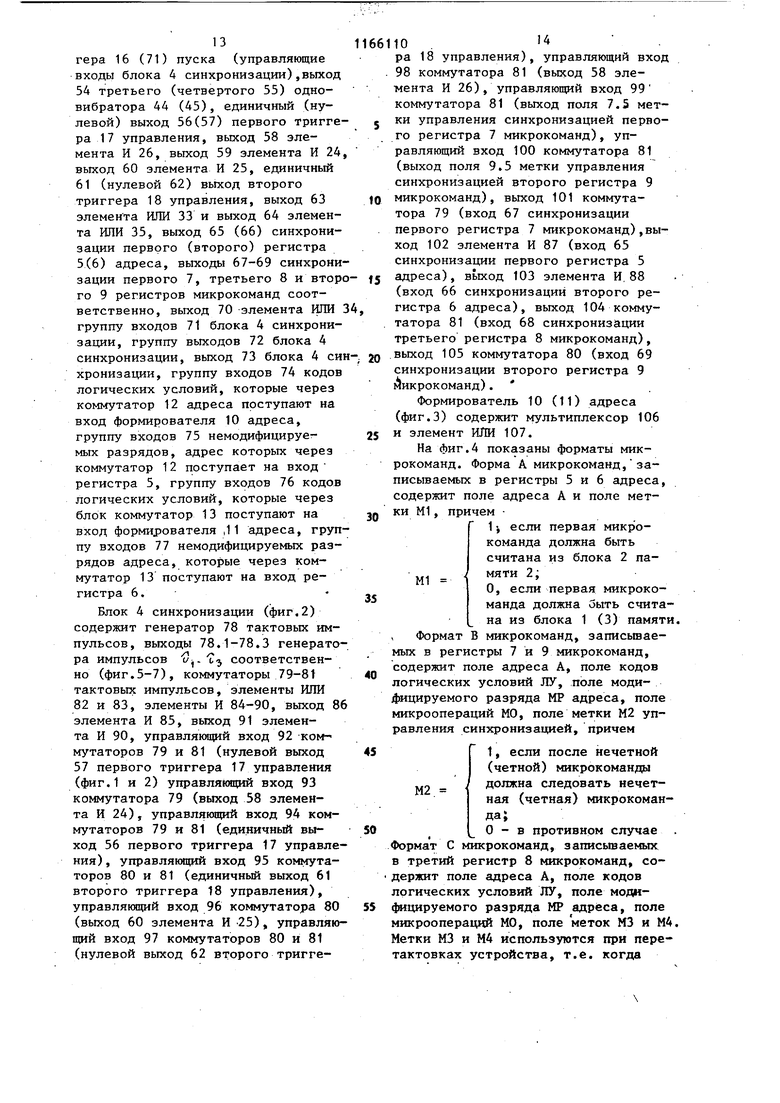

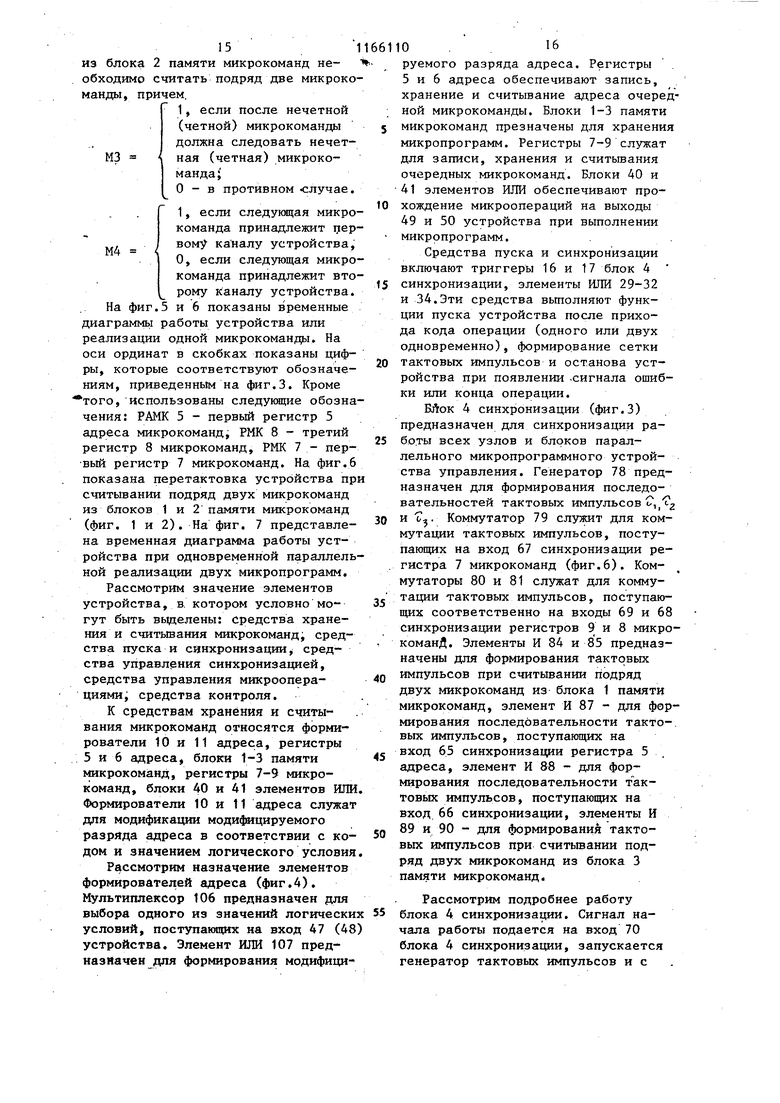

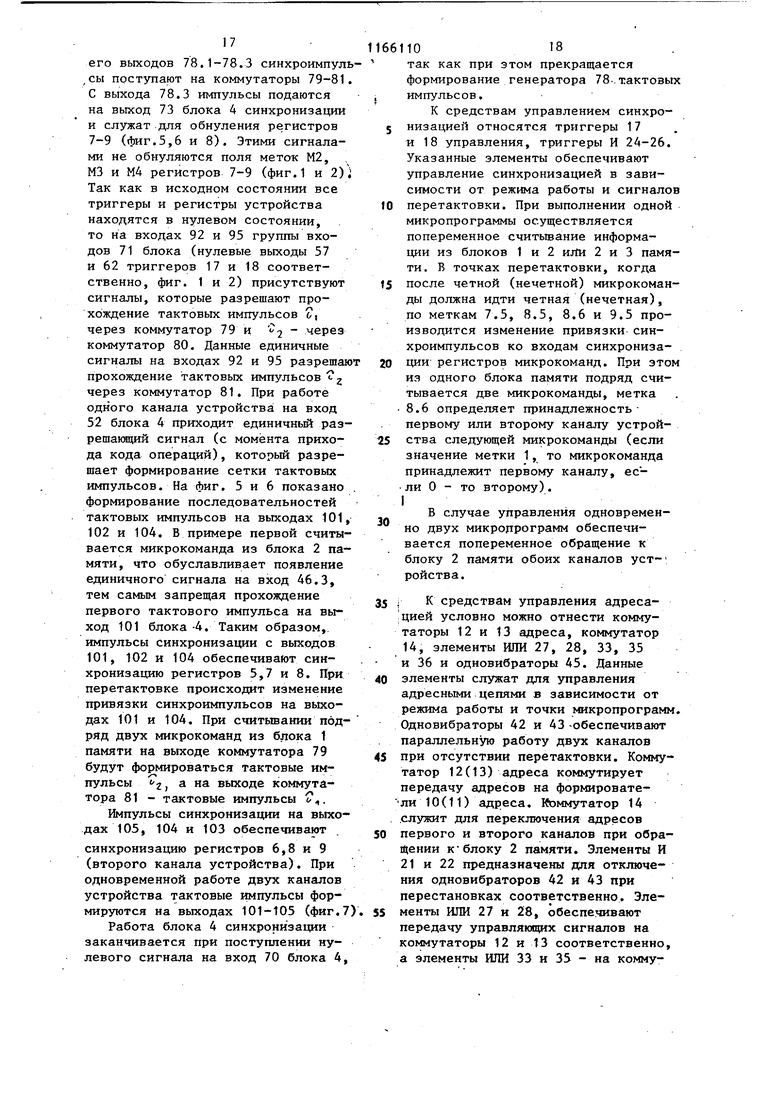

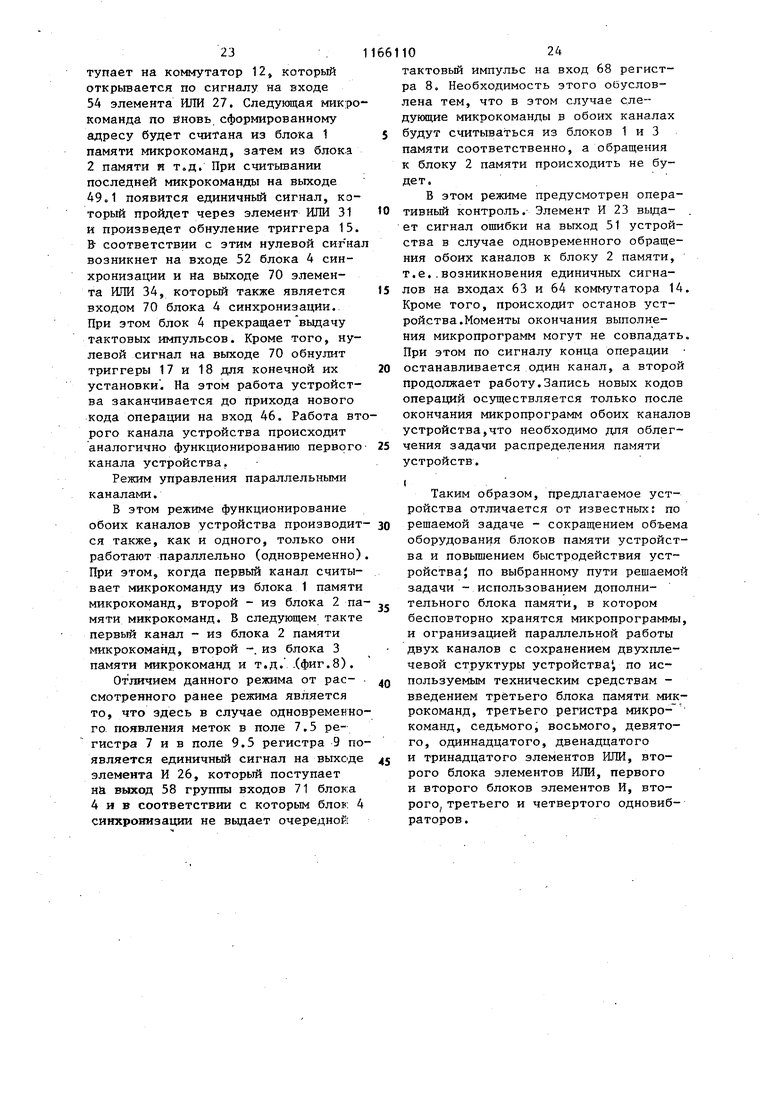

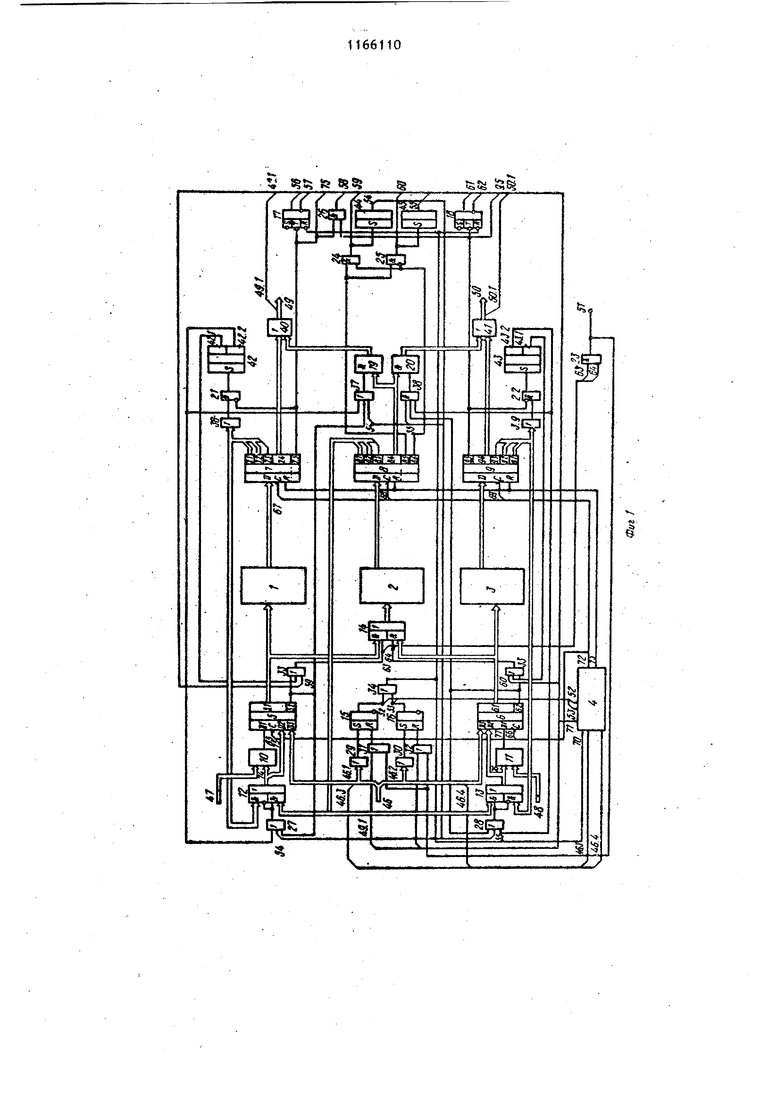

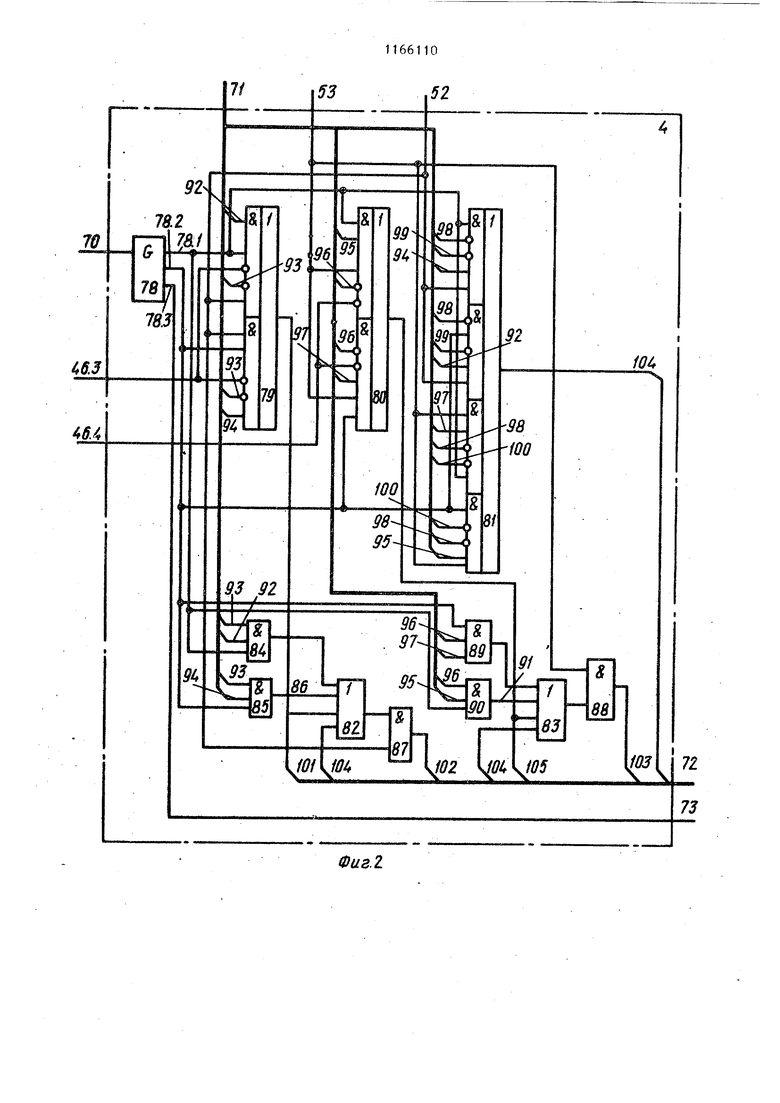

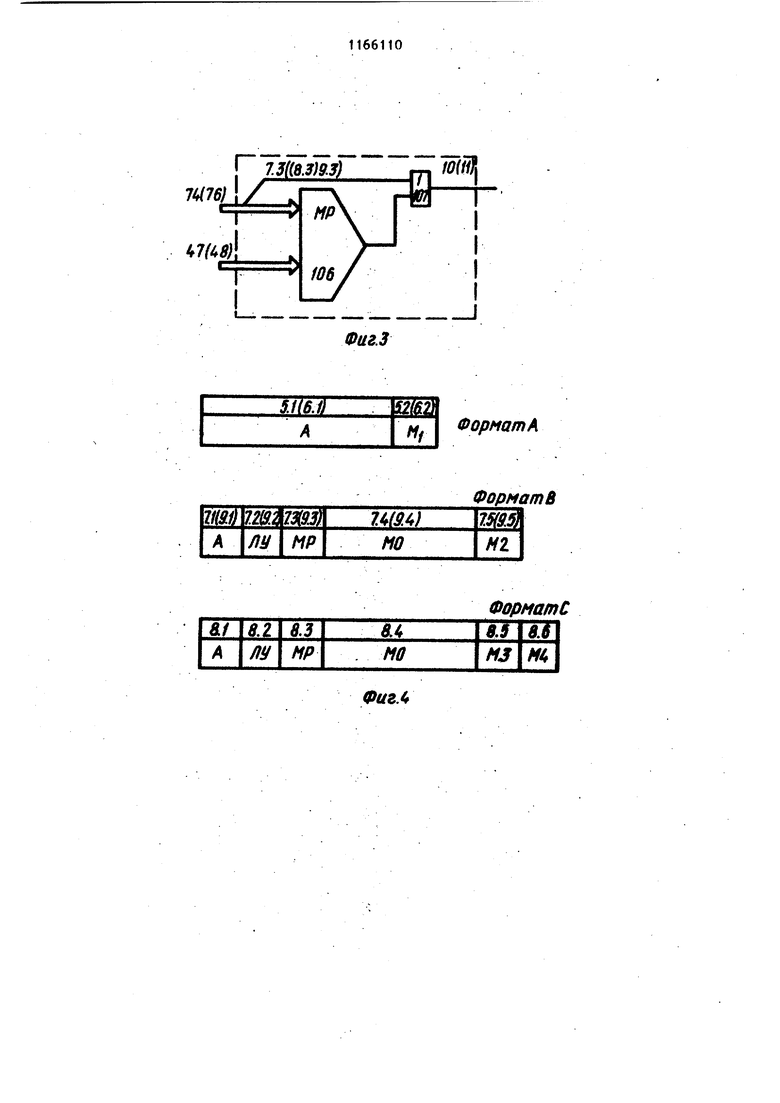

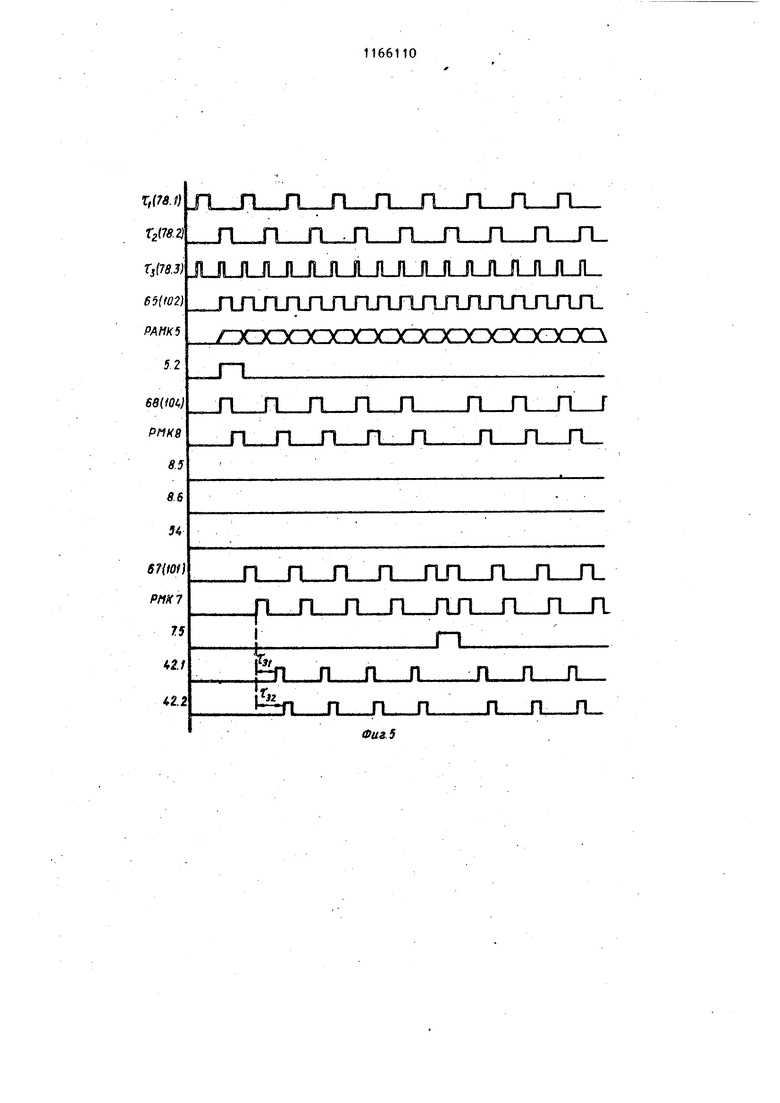

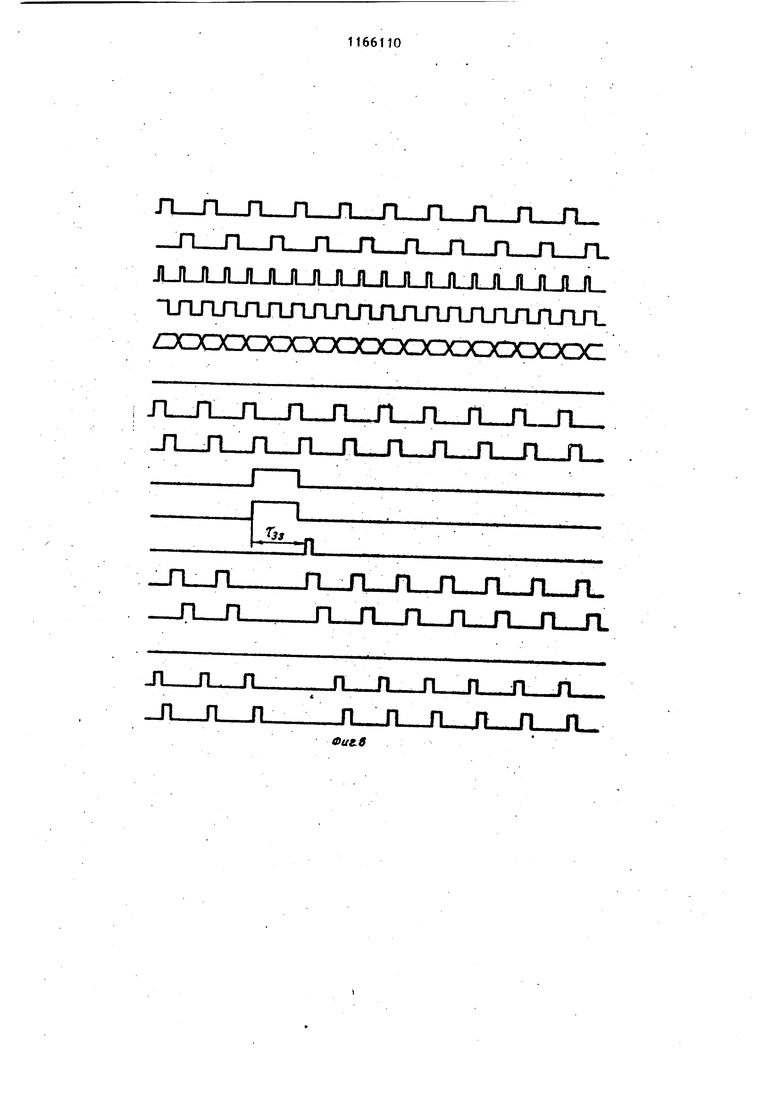

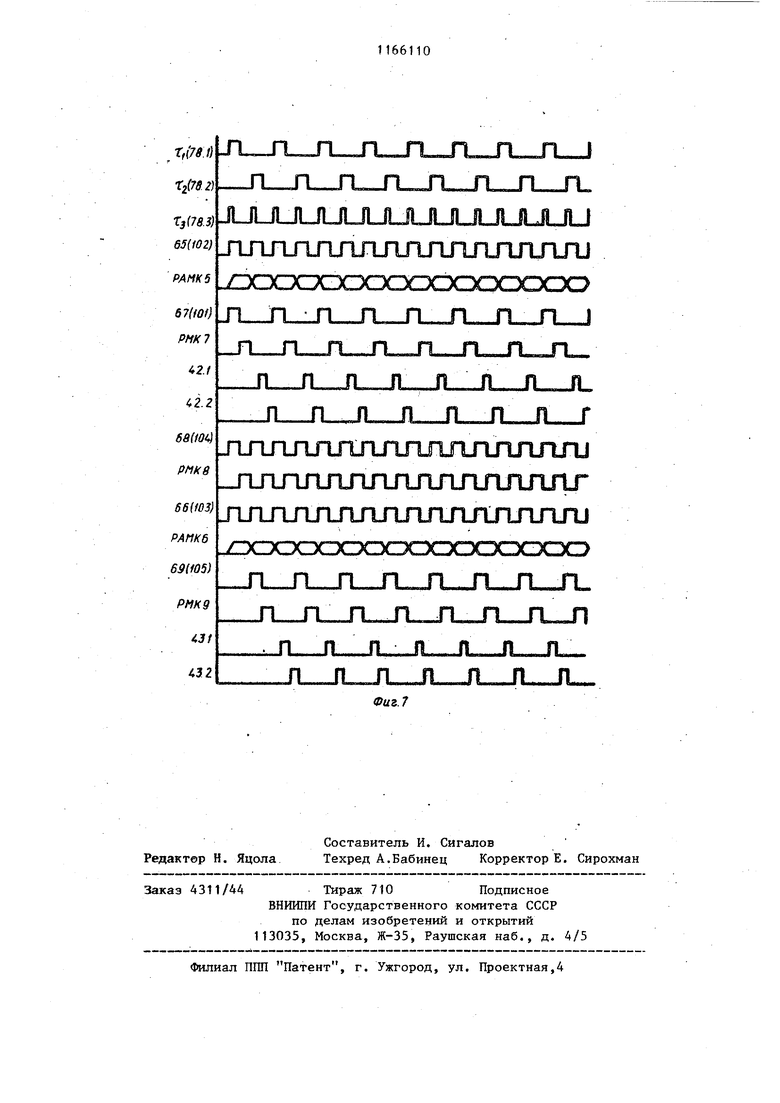

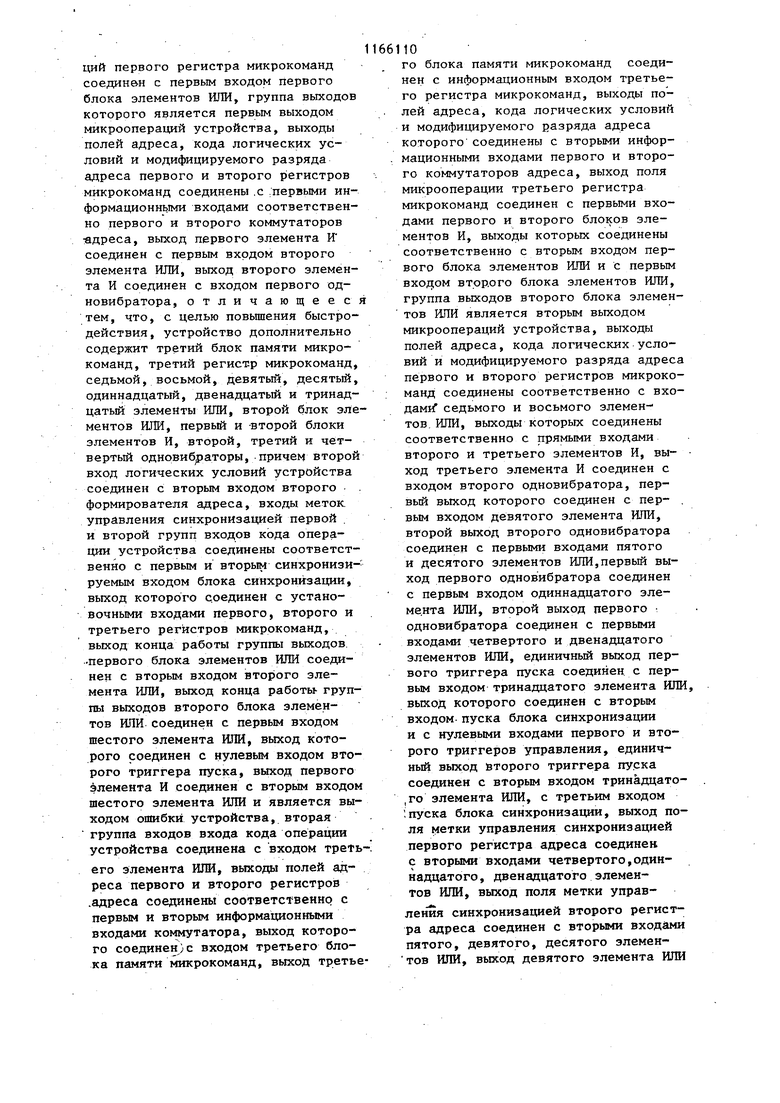

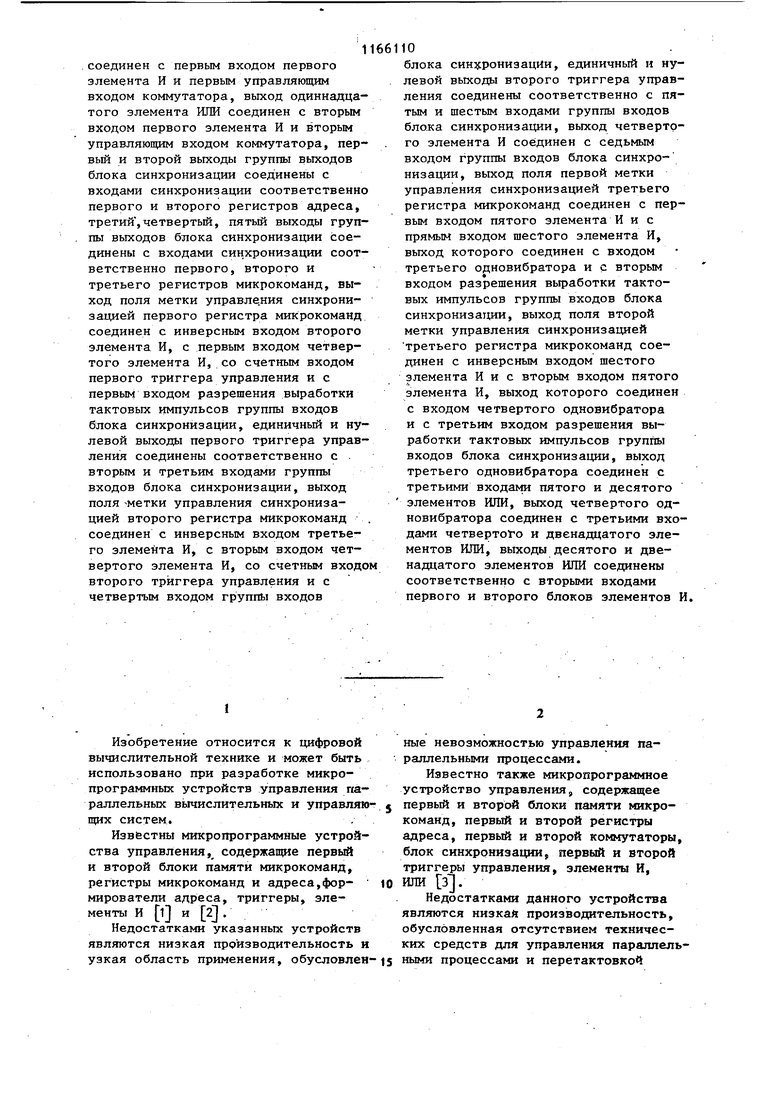

На фиг.1 приведена функциональная схема микропрограммного устройства управления на фиг.2 - функцинальная схема блока синхронизации, на фиг.3 - функциональная схема формирователей адреса, на фиг.4 формат микрокоманд, записьгааемых в регистры адреса и регистры микрокоманд; на фиг. 5-7 - временные диаграммы работы устройства в различных режимах функционирования.

Микропрограммное устройство управления (фиг.1) содержит первый блок 1 памяти микрокоманд, третий блок 2 памяти микрокоманд, второй блок 3 памяти микрокоманд, блок 4 синхронизации, нервьй регистр 5 адреса, содержащий поле 5. адреса и поле 5.2 метки управления синхронизации второй регистр 6 адреса, содержащий поле 6.1 адреса Иполе 6.2 метки управления синхронизации, первый регистр 7 микрокоманд, содержапщй поле 7.1 адреса, поле 7,2 кодов логических условий, поле 7.3 модифицируемого разряда, поле 7.4 микроопераций и поле 7.5 метки управления синхронизацией, третий регистр 8 микрокоманд, срдержащий поле 8.1 адреса, поле 8.2 номеров логических условий, поле

661102

и второй 8.6 меток управления синхронизацией, второй регистр 9 микрокоманд, содержащий поле 9.1 адре- са, поле 9.2 номеров логических.

5 условий, поле 9.3 модифицируемого разряда, поле 9.4 микроопераций и поле 9.5 метки управления синхронизацией, первый формирователь 10 адреса, второй формирователь 11

10 адреса, первый коммутатор 12 адреса, второй коммутатор. 13 адреса, коммутатор 14, первый триггер 15 пуска, второй триггер 16 пуска, первый триггер 17 управления, второй триггер 18 управления, первый блок 19 элементов И, второй блок 20 элементов И, второй элемент И 21, третий элемент И 22, первый элемент И 23, пятый элемент И 24,

20 шестой элемент И 25, четвёртый

элемент И 26, четвертый элемент ИЛИ 27, пятый элемент ИЛИ 28, первый элемент ИЛИ 29, третий элемент ИЛИ 30, второй элемент ИЛИ 31, шестой

25 элемент ИЛИ 32, одиннадцатый элемент ИЛИ 33, тринадцатый элемент ИЛИ 34, девятый элемент ИЛИ 35,седьмой элемент ИЛИ 36, двенадцатый элемент ИЛИ 37, десятый элемент ИЛИ 38,

JQ восьмой элемент ИЛИ 39, первый

блок 40 элементов ИЛИ, второй блок 41 элементов ИЛИ, первый одновибратор 42, содержащий поле 42.1 задержки на j, и поле 42.2 задерж, ки на второй одновибратор 43, содержащий поле 43.1 задержки на с., и поля 43.2 задержки на -iy , третий одновибратор 44, четвертый одновибратор 45.

40 Кроме того, микропрограммное устройство содержит вход 46 кода операции устройства, первую 46.1 (вторая 46.2) группу входов кода операции устройства по которым подаются коды операции, реализуемые в первом (втором) канале устройства, метки 46.3 (46.4) управления синхронизацией первого (второго) канала устройства, вход 47(48) логических

50 условий первого (второго) канала устройства, первый выход 49 микроопераций устройства и выход 49.1 конца работы первого канала устройства, второй выход 50 микроопераций

55 устройства и вьйсод 50.1 конца работы второго канала устройства,выход 51 ошибки устройства, единичный выход 52 (53) первого (второго) триггера 16 (71) пуска (управляющие входы блока 4 синхронизации),выход 54 третьего (четвертого 55) одновибратора 44 (45), единичный (нулевой) выход 56(57) первого тригге ра 1 7 управления, выход 58 элемента И 26, выход 59 элемента И 24 выход 60 элемента И 25, единичный 61 (нулевой 62) выход второго триггера 18 управления, выход 63 элемента ИЛИ 33 и выход 64 элемента ИЛИ 35, выход 65 (66) синхронизации первого (второго) регистра 5(6) адреса, выходы 67-69 синхрони зации первого 7, третьего 8 и втор го 9 регистров микрокоманд соответственно, выход 70 элемента РШИ группу входов 71 блока 4 синхронизации, группу выходов 72 блока 4 синхронизации, выход 73 блока 4 си хронизации, группу входов 74 кодов логических условий, которые через коммутатор 12 адреса поступают на вход формирователя 10 адреса, группу входов 75 немодифицируемых разрядов, адрес которых через коммутатор 12 поступает на вход регистра 5, группу входов 76 кодов логических условий, которые через блок коммутатор 13 поступают на вход формирователя ,11 адреса, груп пу входов 77 немодифицируемых разрядов адреса, которые через коммутатор 13 поступают на вход регистра 6. Блок 4 синхронизации (фиг.2) содержит генератор 78 тактовых импульсов, выходы 78.1-78.3 генерато ра импульсов u.i соответственно (фиг.5-7), коммутаторы 79-81 тактовых импульсов, элементы ИЛИ 82 и 83, элементы И 84-90, выход 8 элемента И 85, выход 91 элемента И 90, управляклций вход 92 коммутаторов 79 и 81 (нулевой выход 57 первого триггера 17 управления (фиг.1 и 2) управляющий вход 93 коммутатора 79 (выход 58 элемента И 24), управляющий вход 94 коммутаторов 79 и 81 (единичный выход 56 первого триггера 17 управле ния) , управляющий вход 95 коммутаторов 80 и 81 (единичный выход 61 второго триггера 18 управления), управляющий вход 96 коммутатора 80 (выход 60 элемента И 25), управляю щий вход 97 коммутаторов 80 и 81 (нулевой выход 62 второго тригге10 .14 . ра 18 управления), управляющий вход 98 коммутатора 81 (выход 58 элемента И 26), управляющий вход 99 коммутатора 81 (выход поля 7.5 метки управления синхронизацией первого регистра 7 микрокоманд), управляющий вход 100 коммутатора 81 (выход поля 9.5 метки управления синхронизацией второго регистра 9 микрокоманд), выход 101 коммутатора 79 (вход 67 синхронизации первого регистра 7 микрокоманд),выход 102 элемента И 87 (вход 65 синхронизации первого регистра 5 адреса), выход 103 элемента И,88 (вход 66 синхронизации второго регистра 6 адреса), выход 104 коммутатора 81 (вход 68 синхронизации третьего регистра 8 микрокоманд), выход 105 коммутатора 80 (вход 69 синхронизации второго регистра 9 1 }икрокоманд). Формирователь 10 (11) адреса (фиг.З) содержит мультиплексор 106 и элемент ИЛИ 107. На фиг.4 показаны форматы микрокоманд. Форма А микрокоманд,записьгоаемых в регистры 5 и 6 адреса, содержит поле адреса А и поле метки Ml , причем 1 -f если первая микрокоманда должна быть считана из блока 2 памяти 2; О, если первая микрокоманда должна быть считана из блока 1 (3) памяти. Формат В микрокоманд, записьшаемых в регистры 7 и 9 микрокоманд, содержит поле адреса А, поле кодов логических условий ЛУ, поле модифицируемого разряда МР адреса, поле микроопераций МО, поле метки М2 управления синхронизацией, причем 1, если после нечетной (четной) микрокоманды должна следовать нечетная (четная) микрокоманда;О-в противном случае ормат С микрокоманд, записьюаемых в третий регистр 8 микрокоманд, содержит поле адреса А, поле кодов логических условий ЛУ, поле модифицируемого разряда МР адреса, поле микроопераций МО, поле меток МЗ и М4. Метки МЗ и М4 используются при перетактовках устройства, т.е. когда из блока 2 памяти микрокоманд необходимо считать подряд две микроко манды, причем. 1, если после нечетной (четной) микрокоманды должна следовать нечетМЗ { ная (четная) микрокоманда;О-в противном -случае. 1, если следукщая микро команда принадлежит пер вому каналу устройства, М4 О, если следующая микро команда принадлежит вто рому каналу устройства. На фиг.5 и 6 показаны временные диаграммь работы устройства или реализации одной микрокоманды. На оси ординат в скобках показаны цифры, которые соответствуют обозначениям, приведенным на фиг.З. Кроме того, использованы следуклцие обозна чения: РАМК 5 - первый регистр 5 адреса микрокоманд; РМК 8 - третий регистр 8 микрокоманд, РМК 7 - первый регистр 7 микрокоманд. На фиг.6 показана перетактовка устройства пр считывании подряд двух микрокоманд из блоков 1 и 2 памяти микрокоманд (фиг. 1 и 2). На фиг. 7 представлена временная диаграмма работы устройства при одновременной параллель ной реализации двух микропрограмм. Рассмотрим значение элементов устройства, в. котором условно могут быть вьщелены: средства хранения и считьшания микрокоманд; средства пуска и синхронизации средства управления синхронизацией, средства управления микрооперациями; средства контроля. К средствам хранения и считывания микрокоманд относятся формирователи 10 и 11 адреса, регистры 5 и 6 адреса, блоки 1-3 памяти икpoкoмaнд, регистры 7-9 микрокоманд, блоки 40 и 41 элементов РШИ Формирователи 10 и 11 адреса служат дпя модификации модифицируемого разряда адреса в соответствии с кодом и значением логического условия Рассмотрим назначение элементов формирователей адреса (фиг.4). Мультиплексор 106 предназначен для выбора одного из значений логически условий, поступаняцих на вход 47 (48 устройства. Элемент ИЛИ 107 предназначен для формирования модифици0 .. 16 руемого разряда адреса. Регистры 5 и 6 адреса обеспечивают запись, хранение и считывание адреса очередной микрокоманды. Блоки 1-3 памяти микрокоманд презначены для хранения микропрограмм. Регистры 7-9 служат для записи, хранения и считьшания очередных микрокоманд. Блоки 40 и 41 элементов ИЛИ обеспечивают прохождение микроопераций на выходы 49 и 50 устройства при выполнении микропрограмм. Средства пуска и синхронизации включают триггеры 16 и 17 блок 4 синхронизации, элементы ИЛИ 29-32 и 34.Эти средства вьтолняют функции пуска устройства после прихода кода операции (одного или двух одновременно), формирование сетки тактовых импульсов и останова устройства при появлении -сигнала ошибки или конца операции. ВЛок 4 синхронизации (фиг.З) предназначен для синхронизации работы всех узлов и блоков параллельного микропрограммного устройства управления. Генератор 78 предназначен для формирования последовательностей тактовых импульсов С, с2 и Т,. Коммутатор 79 служит для коммутации тактовых импульсов, поступающих на вход 67 синхронизации регистра 7 микрокоманд (фиг.6). Коммутаторы 80 и 81 служат для коммутации тактовых импульсов, поступающих соответственно на входы 69 и 68 синхронизации регистров 9 и 8 микрокоманд. Элементы И 84 и 85 предназначены для формирования тактовых импульсов при считывании подряд двух микрокоманд из блока 1 памяти микрокоманд, элемент И 87 - для формирования последовательности такто-. вых импульсов, поступающих на вход 65 синхронизации регистра 5 адреса, элемент И 88 - для формирования последовательности т актовых импульсов, поступающих на вход 66 синхронизации, элементы И 89 и 90 - для формирования тактовых импульсов при считьюании подряд двух микрокоманд из блока 3 памяти микрокоманд. Рассмотрим подробнее работу блока 4 синхронизации. Сигнал начала работы подается на вход 70 блока 4 синхронизации, запускается генератор тактовых импульсов и с его выходов 78.1-78.3 синхроимпул ,сы поступают на коммутаторы 79-81 С выхода 78.3 импульсы подаются на выход 73 блока 4 синхронизации и служат для обнуления регистров 7-9 (фиг.5,6 и 8). Этими сигналами не обнуляются поля меток М2, МЗ и М4 регистров 7-9 (фиг.1 и 2) Так как в исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии, то на входах 92 и 95 группы входов 71 блока (нулевые выходы 57 и 62 триггеров 17 и 18 соответственно, фиг. 1 и 2) присутствуют сигналы, которые разрешают прохождение тактовых импульсов о, через коммутатор 79 и через коммутатор 80. Данные единичные сигналы на входах 92 и 95 разреша прохождение тактовых импульсов tj через коммутатор 81. При работе одного канала устройства; на вход 52 блока 4 приходит единичный раз решакщий сигнал (с момента прихо да кода операций), который разрешает формирование сетки тактовых импульсов. На фиг. 5 и 6 показано формирование последовательностей тактовых импульсов на выходах 101 102 и 104. В примере первой считы вается микрокоманда из блока 2 па мяти, что обуславливает появление единичного сигнала на вход 46.3, тем самым запрещая прохождение первого тактового импульса на выход 101 блока-4. Таким образом, импульсы синхронизации с выходов 101, 102 и 104 обеспечивайт синхронизацию регистров 5,7 и 8. При перетактрвке происходит изменение привязки синхроимпульсов на выходах 101 и 104. При считывании под ряд двух микрокоманд из блока 1 памяти на выходе коммутатора 79 будут формироваться тактовые импульсы г, а на выходе коммутатора 81 - тактовые импульсы С . Импульсы синхронизации на выхо дах 105, 104 и 103 обеспечивают синхронизацию регистров 6,8 и 9 (второго канала устройства). При одновременной работе двух каналов устройства тактовые импульсы формируются на выходах 101-105 (фиг. Работа блока 4 синхронизации заканчивается при поступлении нулевого сигнала на вход 70 блока 4 1018 так как при этом прекращается формирование генератора 78-. тактовых импульсов. К средствам управлением синхронизацией относятся триггеры 17 и 18 управления, триггеры И 24-26. Указанные элементы обеспечивают управление синхронизацией в зависимости от режима работы и сигналов перетактовки. При выполнении одной микропрограммы осуществляется попеременное считьгоание информации из блоков 1 и 2 или 2 и 3 памяти. В точках перетактовки, когда после четной (нечетной) микрокоманды должна идти четная (нечетная), по меткам 7.5, 8.5, 8.6 и 9.5 производится изменение привязки синхроимпульсов ко входам синхронизации регистров микрокоманд. При этом из одного блока памяти подряд считывается две микрокоманды, метка 8.6 определяет принадлежностьпервому или второму каналу устройства следующей микрокоманды (если значение метки 1, то микрокоманда принадлежит первому каналу, если О - то второму). В случае управления одновременно двух микропрограмм обеспечивается попеременное обращение к блоку 2 памяти обоих каналов устройства. К средствам управления адресацией условно можно отнести коммутаторы 12 и 13 адреса, коммутатор 14, элементы ИЛИ 27, 28, 33, 35 и 36 и одновибраторы 45. Данные элементы служат для управления адресными цепями в зависимости от режима работы и точки микропрограмм. Одновибраторы 42 и 43 -обеспечивают параллельную работу двух каналов при отсутствии перетактовки. Коммутатор 12(13) адреса коммутирует передачу адресов на формирователи 10(11) адреса. Коммутатор 14 .служит для переключения адресов первого и второго каналов при обращении кблоку 2 памяти. Элементы И 21 и 22 предназначены для отключения одновибраторов 42 и 43 при перестановках соответственно. Элементы ИЛИ 27 и 28, обеспечивают передачу управляющих сигналов на KOhiMyTaTopu 12 и 13 соответственно, а элементы ИЛИ 33 и 35 - иа комму9

татор 14. К средствам управления микрооперациями относятся элементы ИЛИ 37 и 38 и блоки 19 и 20 элементов И. Они обеспечивают управление передачей микроопераций на первый и второй входы микроопераций устройства.

К средствам контроля принадлежи элемент И 23, который формирует сигнал ошибки в случае одновременного обращения двух каналов к блоку 2 памяти. При этом происходит останов устройства, и сигнал ошибки поступает на выход 51 ошибки устройства.

Предлагаемое устройство функционирует в следующих режимах: режме реализации управления одним каналом, режиме управления параллельными каналами.

Режим реализации управления одним каналом.

В исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии. Вход 46 кода операции устройства состоит из дву групп входов: первой группы входов 46.1 предназначенной для первогоканала устройства, и второй группы входов 46.2, предна.значенной для второго канала устройства. После прихода кода операций на вхо 46.1 первой группы входов кода операций устройства сигнал с выхода элемента ИПИ 29 устанавливает триггер 15 в единичное состояние, при этом на выходе 70 элемента ИЛИ 34 появляется единичный сигнал, который подается на вход 70 схемы 4 синхронизации и разрешает последней формирование тактовых импульсо Перед считьгеанием очередной микрокоманды по переднему фронту тактового импульса Г. с выхода 73 блока 4 синхронизации происходит обнуление всех полей регистров 7-9 за исключением полей меток М2, МЗ и М4.

Пусть при этом на выходе 46.3 появится единичный сигнал. По переднему фронту первого тактового импульса, поданного на синхровход 65 (66) регистра 5, в регистр 5 запишется начальный адрес микропрограммы, хранящейся в блоке 2 памяти При этом на выходе регистра 5 в поле 5,1 (6.1) устанавливается начальный адрес

11020

микропрограмм, а в поле 5.2 - значение сигнала метки управления Ml, которое соответствует сигналу на

входе 46.3 (фиг. 6 и 7). Этот сигнал проходит через элемент ШШ 33 на вход 63 коммутатора 14, разрешая подачу на вход блока 2 памяти микрокоманд. Одновременно, в соответствии с сигналом на входе 52, блок 4 синхронизации выдает в группу выходов 72 на вход 68 синхронизации регистра 8 синхроимпульс, по заднему фронту которого производится запись микрокоманды в регистр 8 из блока 2 памяти микрокоманд. В то же время сигнал метки с поля 5.2 регистра 5 подается на вход элемента ШШ 37, обуславливая появление единичного потенциала на его выходе, поступая на вход блока

19 элементов И, разрешает прохождение микроопераций с поля 8.4 регистра 8 через блок 19 элементов И и блок 40 элементов ИЛИ на выход 49 микроопераций устройства. Одновременно тот же сигнал с поля 5.2 регистра 5 подается на вход элемента ИПИ 27, с выхода.которого единичный сигнал поступает на выход комму- татора 12 адреса, разрешая прохождение адреса с выхода регистра 8 на . выход формирователя 10 адреса. По переднему фронту очередного тактового импульса производится запись сформированного адреса в регистр 5, а в поле 5.2 (6.2) записьшается 0. С выхода регистра 5 поля 5.1 адрес поступает на вход блока 1 памяти

Микрокоманд. По заднему фронту очередного импульса на входе 67 регистра 7 произойдет считьгоание очередной микрокоманды из блока 2 памяти микрокоманд. Микрооперации с поля 7.4 регистра 7 поступают через блок 40 элементов ИПИ на выход 49 устройства. Одновременно с полей 7.1-7.3 адресная часть микрокоманды поступает на вход коммутатора 12 адреса и на вход элемента ИЛИ 36. С его выхода единичный сигнал проходит через элемент И 21 на вход одновибратора 42. Адрес очередной микрокоманды через коммутатор 12 поступает на вход формирователя 10 адреса, где будет сформирован исполнительный адрес очередной микрокоманды, который запишется, по переднему фронту очередного тактового 21 . импульса в регистр 5 адреса. Одновременно единичный сигнал возникае на выходе 42.1 одновибратора 42 (задержка осуществляется на Г, фиг. 6 и.7), который, пройдя через элемент ИЛИ 33, открьгеает коммута- тор 14 для прохождения адреса на вход блока 2 памяти микрокоманд. После этого по заднему фронту тактового импульса (вход 68) происходит запись очередной микрокоманды в регистр 8. Одновременно появляет ся импульс на выходе 42.2 одновиб ратора 42 (фиг. 6 и 7, задержка на tsg который, пройдя через эле мент ИЛИ 37, разрешит прохождение микроопераций через блок 19 элемен тов И и блок 40 элементов ИЛИ на выход устройства 49. Кроме того, {этот сигнал, пройдя через элемент ИЛИ 27, разрешит прохождение адреса через коммутатор 12 с полей .8.1-8.3 регистра 8; Далее работа устройства будет происходить анало гично, описанным тактам функциониро вания устройства. Микрокоманда будет считана из блока 1 памяти микрокоманд, так как управляющие сигналы на входах коммутатора 14 отсутствуют и блок 4 синхронизации вьщает тактовый импульс на вход 67 регистра 7. Пусть при считьгоании микрокоманды из регистра 7 в поле метки 7,5 появился единичный сигнал, который свидетельствует о том, что следующую микрокоманду необходимо считать из того же блока памяти. Этот сигнал закрывает элемент И 21 и единичный сигнал с выхода элемента ИЛИ 36 не проходит на вход одновибратора 42, а также переключает триггер 17 в единичное состоя ние, что обуславливает появление единичного сигнала на выходе 56 группы входов 71 и нулевого потенциала - на входе 5.7. Кроме того, сигнал метки подается яа вход 7.5 группы входов 71. Сформированные таким образом сигналы управления по группе входов 71 поступают в блок 4 синхронизации, который производит перетактовку (изменение привязки) тактовых импульсов к каналам. Так как управляющие сигна лы на входах элемента ИЛИ 27 отсут ствуют, то коммутатор 12 адреса разрешит прохождение адреса с по022лей 7.1-7.3 регистра 7 в формирователь 10 адреса и на вход регистра 5. Далее произойдет считывание очередной микрокоманды из блока 1 памяти микрокоманд и т.д. В случае, если метка 7.5 появляется снова, то произойдет еще раз считьшание микрокоманд из того же блока памяти, если эта метка не появляется, то считывание очередной микрокоманды будет происходить из блока 2 микрокоманд аналогично ранее описанным тактам работы устройства. Рассмотрим функционирование устройства при считьшании подряд двух микрокоманд из блока 2 памяти,при этом в поле меток 8.5 и 8.6 появится единичный сигнал. Это свидетельствует о том, что следующая микрокоманда должна быть считана из блока 2 памяти микрокоманд. Сиг-, НсШы меток МЗ и М4 поступают на вхо- ДЫ элементов И 24 и 25. . На выходе элемента И 24 формируется единичный сигнал, а на выводе элемента И 25 нулевой сигнал, которые поступают на вход одновибраторов 44 и 45 и входы 59 и 60 соответственно. Сигнал с выхода 59 поступает на вход элемента ИЛИ 33. На выходе элемента ИЛИ 33 будет единичный сигнал. В соответствии с единичным сигналом на выходе 42.2 одновибратора 42 (задержка на )f которь|й пройдет через элемент ИЛИ 27 и откроет коммутатор 12 для прохождения адреса очередной микрокоманды из регистра 8, в соответ- . ствии с которым сформируется исполнительный адрес микрокоманды в регистре 5 по очередному тактовому импульсу. Далее через открытый коммутатор 14 по единичному сигналу с выхода элемента ИЛИ 33 произойдет обращение к блоку 2 памяти микрокоманд, с которого по заднему фронту очередного тактового импульса будет считана микрокоманда в регистр 8. Одновременно появляется импульс на выходе одновибратора 44 (фиг.7, задержка tj который, проходя через элемент ИЛИ 37, OTKptOBaer блок19 элементов И для прохождения Ш1кроопераций с поля 8.4 регистра 8 через блок 40 элементов ИЛИ на выход 49 устройства. Адресная информация с полей 8.1-8.3 регистра 8 пос23.

тупает на коммутатор 12, который открьгаается по сигналу на входе 54 элемента ИЛИ 27. Следующая микрокоманда по йновь сформированному адресу будет считана из блока 1 памяти микрокоманд, затем из блока 2 памяти я т.д. При считьгоании последней микрокоманды на выходе А9.1 появится единичный сигнал, который пройдет через элемент ИЛИ 31 и произведет обнуление триггера 15. & соответствии с этим нулевой сигна возникнет на входе 52 блока 4 синхронизации и на выходе 70 элемента ИЛИ 34, который также является входом 70 блока 4 синхронизации. При этом блок 4 прекращает выдачу тактовых импульсов. Кроме того, нулевой сигнал на выходе 70 обнулит триггеры 17 и 18 для конечной их установки. На этом работа устройства заканчивается до прихода нового кода операции на вход 46. Работа вт рого канала устройства происходит аналогично функционированию первого канала устройства.

Режим управления параллельными каналами.

В этом режиме функционирование обоих каналов устройства производится также, как и одного, только они работают параллельно (одновременно) При этом, когда первый канал считывает микрокоманду из блока 1 памяти микрокоманд, второй - из блока 2 памяти микрокоманд. В следующем такте первый канал - из блока 2 памяти микрокоманд, второй -. из блока 3 памяти микрокоманд и т.д. .(фиг.8) .

Отличием данного реясима от рассмотренного ранее режима является то, что здесь в случае одновременного появления меток в поле 7.5 регистра 7 и в поле 9.5 регистра 9 появляется единичный сигнал на выходе элемеита И 26, который поступает на выход 58 группы входов 71 блока 4 и в соответствии с которым блок 4 синхронизации не вьздает очередной

6611024

тактовьй импульс на вход 68 регистра 8, Необходимость этого обусловлена тем, что в этом случае следующие микрокоманды в обоих каналах 5 будут считываться из блоков 1 и 3 памяти соответственно, а обращения к блоку 2 памяти происходить не будет.

В этом режиме предусмотрен оперативный контроль. Элемент И 23 вьща- . ет сигнал ошибки на выход 51 устройства в случае одновременного обращения обоих каналов к блоку 2 памяти, т.е..возникновения единичных сигналов на входах 63 и 64 коммутатора 14. Кроме того, происходит останов устройства.Моменты окончания выполнения микропрограмм могут не совпадать. При этом по сигналу конца операции

0 останавливается один канал, а второй продолжает работу.Запись новых кодов операций осуществляется только после окончания микропрограмм обоих каналов устройства,что необходимо для облегчения задачи распределения памяти устройств.

Таким образом, предлагаемое устройства отличается от известных: по

0 решаемой задаче - сокращением объема оборудования блоков памяти устройства и повышением быстродействия устройства; по выбранному пути решаемой задачи - использованием дополни5 тельного блока памяти, в котором

бесповторно хранятся микропрограммы, и огранизацией параллельной работы двух каналов с сохранением двухгшечевой структуры устройства , по используемым техническим средствам введением третьего блока памяти микрокоманд, третьего регистра микро- команд, седьмого, восьмого, девятого, одиннадцатого, двенадцатого

5 и тринадцатого элементов ИЛИ, второго блока элементов ИЛИ, первого и второго блоков элементов И, второго третьего и четвертого одновибраторов.

V te 83S5 7

- NJ Ct4

t«a (

Фиг.1

Ш8.тю

74/7g; /

I

А

Фаг.З

Формат А.

Формате

ШЩ

UiM

мг

Формате

Фиг4 Т,(78.}) Г2(7ЙД| JULJUUIJUUL Гз(7в.З) 65((02) ....,.JЛJlJlnЛJ Г РАНК5 (DOaCXDC)OOCXDO S8(iOQ Р/1К8 S7(fOn РНК 7 XD

JUULJUUULJIJI

aлJ JглJггlЛJггlrlJггLГl

ZIXDOOCXIOCXIXDCXDOCX

Г,(7в.1

JULJUUIJUULJU

Гз(78.3) 65(102)

JглJ J J JтnJlЛJ

jCDCDCXiXDOCXXDCXDC

РАМК6

67(fOf} РНК 7

«2.2

лJi

68(10

JггLГlЛJlЛJ JггlгaJгrгл

PMk8

.JгRЛЛJ JlЛJгJгrгnJlл

66(103)

JглJ JlЛJглJгплJглJ J АНК6

XDCZXIXDCXDOCXXDCOCXDCDO 9(105}

РНК9 J/

n n n n n n

n n Д n л n n 432

n n n n n n П П П n r

JT

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1985-07-07—Публикация

1983-11-03—Подача