1

Изобретение относится к области вычислительной техники и, в частности, к устройствам микропрограммного управления цифровых вычислительных машин.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, соединенных с регистрами адреса, два блока проверки условий, две схемы И, выход каждой схемы И соединен со входом соотвегствующего запоминающего блока, первый выход которого соединен с первым входом соответствующего блока проверки условий, один вход каждой схемы И соединен с соответствующим входом устройства, управляющие входы которой соединены со вторыми входами блоков проверки условий, первый выход одного блока проверки условий соединен со входом другого регистра адреса, вторые выходы каждого запоминающего блока соединены с соответствующими выходами устройства.

Однако необходимость введения двух «пустых микрокоманд при реализации режима ожидания приводит к увеличению объема запоминающих блоков, а наличие двух отдельных групп разрядов в микрокоманде: для проверки условий выхода из режима ожидания и для проверки условий ветвления - увеличивает разрядность микрокоманд.

Цель изобретения - сократить объем оборудования устройства.

Это достигается тем. что устройство содержит два триггера блокировки, нулевой вход

каждого триггера блокировки соединен с третьим выходом соответствующего запоминающего блока, единичный выход соединен с другим входом соответствующей схемы И, второй выход одного блока проверки условий

соединен с единичным входом другого триггера блокировки, а единичные выходы триггеров блокировки соединены с третьими входами других блоков проверки условий.

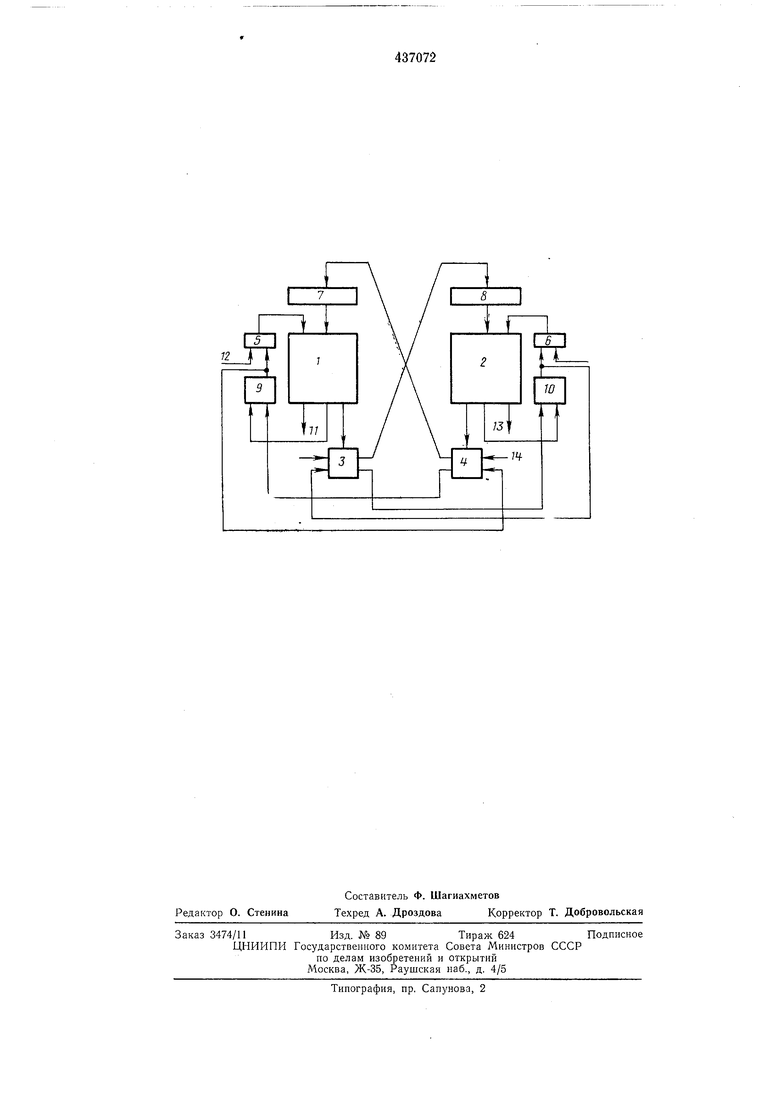

Блок-схема предлагаемого устройства приведена на чертеже.

Микропрограммное устройство управления содержит запоминающие блоки 1 и 2, блоки проверки условий 3 и 4, схемы И 5 и 6, регистры адреса 7 и 8, триггеры блокировки 9 и 10.

Когда отсутствует необходимость реализации условий ожидания, микропрограммное устройство управления работает аналогично известному устройству, т. е. производится попеременное считывание микроко.манд импульсами двух фаз то с одного, то с другого запоминающего блока. В режиме ожидания устройство работает

следующим образом.

Пусть на регистре адреса 7 находится адрес «а микрокоманды, с выполнения которой начинается режим ожидания. Сигналы с выхода регистра адреса 7 ноступают на запоминающий блок 1, где выбирают в соответствии с адресом «а микрокоманду, нодлежащую считыванию. Считывание производится тактовым сигналом, поступающим с выхода схемы И 5 на запоминающий блок 1. Считанная по адресу «а микрокоманда реализует управляющие микрооперации (по выходу 11); устанавливает в регистре адреса 8 адрес «б следующей микрокоманды, считываемой из запоминающего блока 2; сигналом соответствующей микрооперации дополнительного выхода запоминающего блока 1 устанавливает триггер блокировки 9 в нулевое состояние.

При этом сигнал с выхода триггера блокировки 9 поступает на схему И 5, блокируя прохождение в дальнейшем тактовых импульсов, поступающих по щине 12.

В следующем такте происходит считывание микрокоманды но адресу «б со второго, незаблокированного запоминающего блока 2. Сигналы выходов регистра адреса 8 поступают на запоминающий блок 2, где выбирают в соответствии с адресом «б микрокоманду, нодлежащую считыванию. Тактовые имнульсы, поступающие на схему П 6, пропускаются схемой, так как триггер блокировки 10 находится в единичном состоянии. Сигнал считывания поступает на запоминающий блок 2, производя считывание выбранной микрокоманды.

Считанная но адресу «б микрокоманда реализует управляющие микрооперации (по выходу 13) и устанавливает в регистре адреса 7 адрес микрокоманды, следующей после точки ожидания. Па блок проверки условий 4 по шине 14 поступает сигнал логических условий, определяющих выход из режима ожидания или ветвления микропрограммы. При ложности логического условия, определяющего выход из ожидания, сигнал установки триггера блокировки 9 в единицу с выхода блока проверки условий 4 не подается. Считывание микрокоманд из запоминающего блока 1 остается заблокированным. Очередной тактовый импульс пропускается, и в следующем такте снова считывается микрокомапда по адресу «б с незаблокированного запоминающего блока 2.

При истинности проверяемого логического условия, определяющего выход из ожидания, сигнал соответствующей микрооперации проверки проходит с выхода блока проверки условий 4 на триггер блокировки 9 и устанавливает его в единичное состояние. Происходит разблокировка считывания запоминающего блока 1. При поступлении на схему П 5 очередного тактового импульса из запоминающего блока 1 считывается первая после точки 5 ожидания микрокоманда.

Аналогично описанному реализуется ожпдание и выход из него нри считывании микрокоманды с адресом «а из запоминающего блока 2. В этом случае блокируется триггер 10 блокировки 10 и проверяется условие выхода из ожидания, поступающее на блок проверки условий 3.

Таким образом, в предлагаемо.м устройстве в режиме ожидания нериодически считывается только одна микрокоманда (а не две, как в известном устройстве), что позволяет сократить емкость запоминающего блока.

Кроме того, в предлагаемом устройстве нет необходимости нроизводить условную адресацию в режиме ожидания, и этот режим может быть идентифицирован по состоянию триггеров блокировки. Это позволяет использовать одни и те же разряды микрокоманды как для микроопераций проверки логических 5 условий, определяющих ветвления, так и для микроопераций, определяющих выход из ожидания, что снижает разрядность микрокоман

ДЫ.

0Предмет изобретения

Микропрограммное устройство управления, содержащее два запоминающих блока, соединенных с соответствующими регистрами адреса, два блока проверки условий, две схемы И,

5 выход каждой схемы И соединен со входом соответствующего запоминающего блока, первый выход которого соединен с первым входом соответствующего блока проверки условий, один вход каждой схемы И соединен с

0 соответствующим входом устройства, упраг.ляющие входы которого соединены со вторыми входами блоков проверки условий, первый выход одного блока проверки условий соединен со входом другого регистра адреса, вторые выходы каждого запоминающего блока соединены с соответствующими выходами устройства, отличающееся тем, что, с целью сокращения оборудования, устройство содержит два триггера блокировки, нулевой

0 вход каждого триггера блокировки соединен с третьим выходом соответствующего запоминающего блока, единичный выход соединен с другим входом соответствующей схемы И, второй выход одного блока проверки условий

соединен с единичным входом другого триггера блокировки, а единичные выходы триггеров блокировки соединены с третьими входами других блоков проверки условий.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления | 1979 |

|

SU881749A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU830384A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

Авторы

Даты

1974-07-25—Публикация

1972-12-06—Подача