первого блока памяти, выход третьего элемента И соединен с входом заие,сения счетмика микрокоманд, счетный вход которого соединен со счетным входом сметчика адреса и выходом четвертого элемента И, вход которого соединен с инверсным выходом триггера, вход начальной уста.новки устройства соединен с входами сброса счетчика микрокоманд, триггера , регистра логичес:ких условий и буферного регистра,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1981 |

|

SU985790A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Устройство микропрограммного управления | 1980 |

|

SU960814A1 |

1, Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин.

Известно микропрограммное устройство управления, содержащее два блока памяти, два дешифратора, регистр адреса и счетчик адреса, буферный регистр,регистр логических условий, счетчик микрокоманд, шифратор, элементы И и элементы задержки l.

Недостатком данного устройства является низкая производительность, обусловленная тбм, что при каждом переходе от одной последовательност микрокоманд к другой непроиёводительно используется микрокомандный цикл.

Наиболее близким к предлагаемому по технической сущности является микропрограммное устройство управления, содержащее первую группу элементов И, выходы которых соединены с первыми входами буферного регистра, выходом соединенного с первыми входами элементов И группы, выходы которых соединены с первыми входами регистра адреса. Выход регистра адреса подключен к первому входу первого дешифратора, выходом соединенного с адресным входом первого блока памяти, первый выход которого соединен с вторым входом буферного регистра, а второй выход - с первым входом счетчика микрокоманд. Выход счетчика микрокоманд через первый элемент И соединен с первым входом второго элемента И, выход которого соединен с вторыми входами элементов И второй группы. Третий выход первого блока

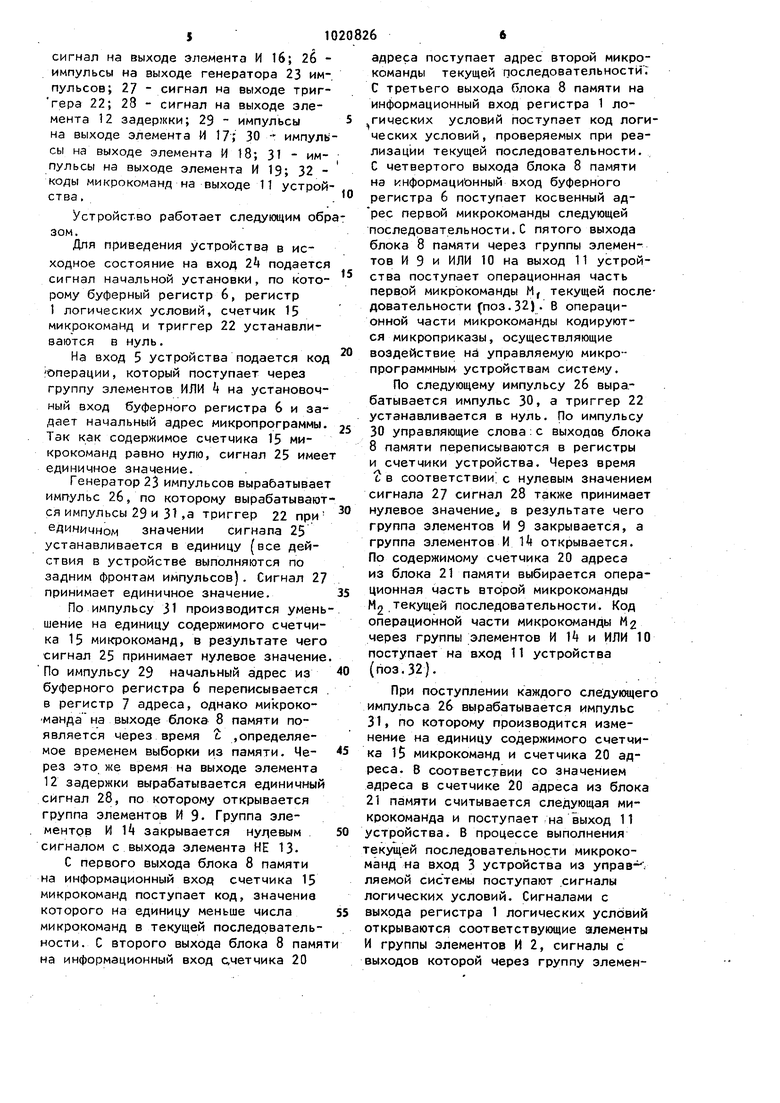

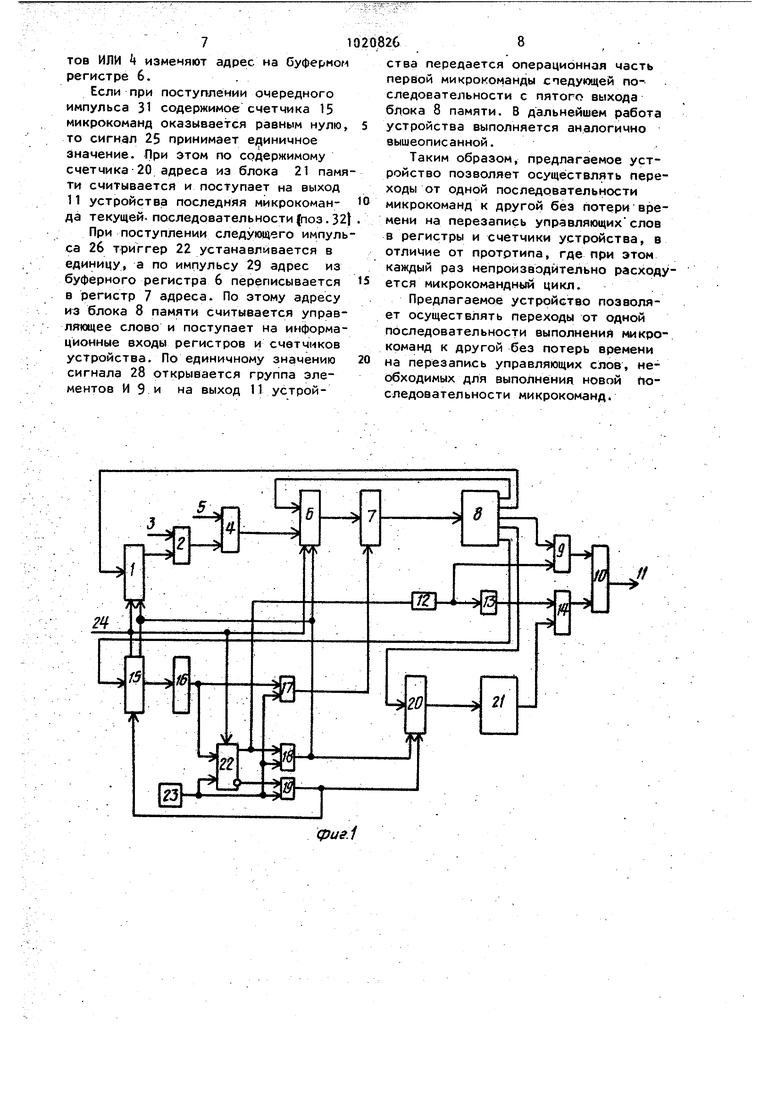

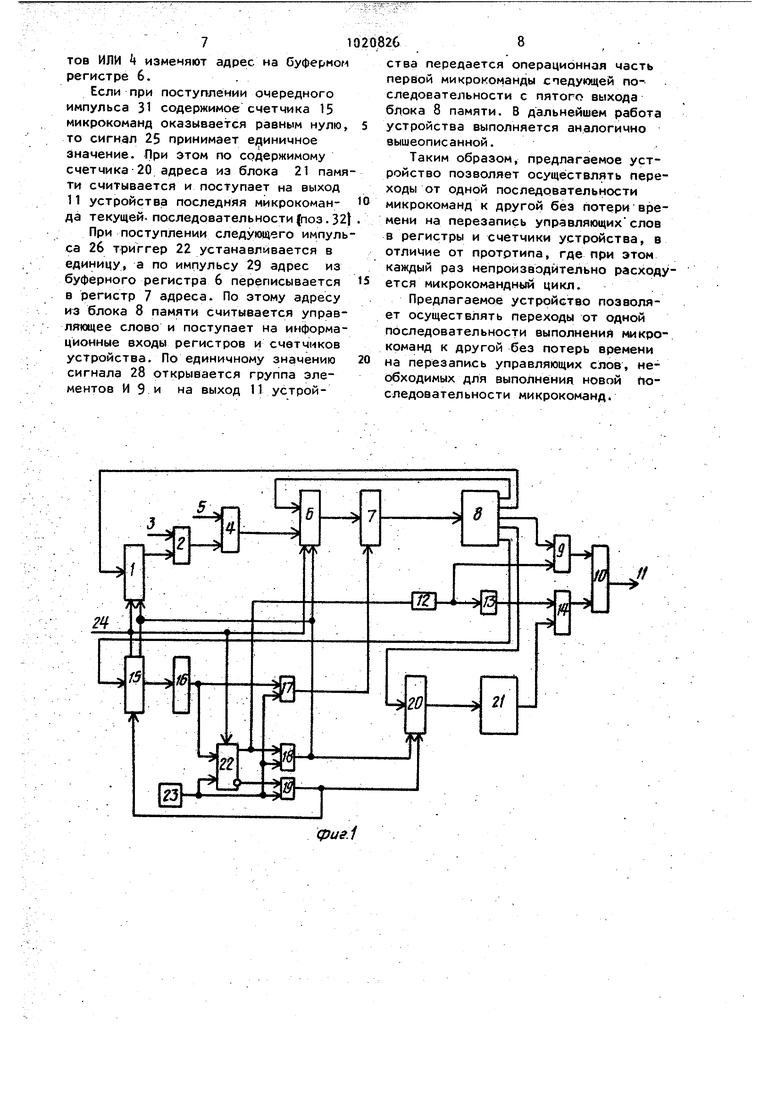

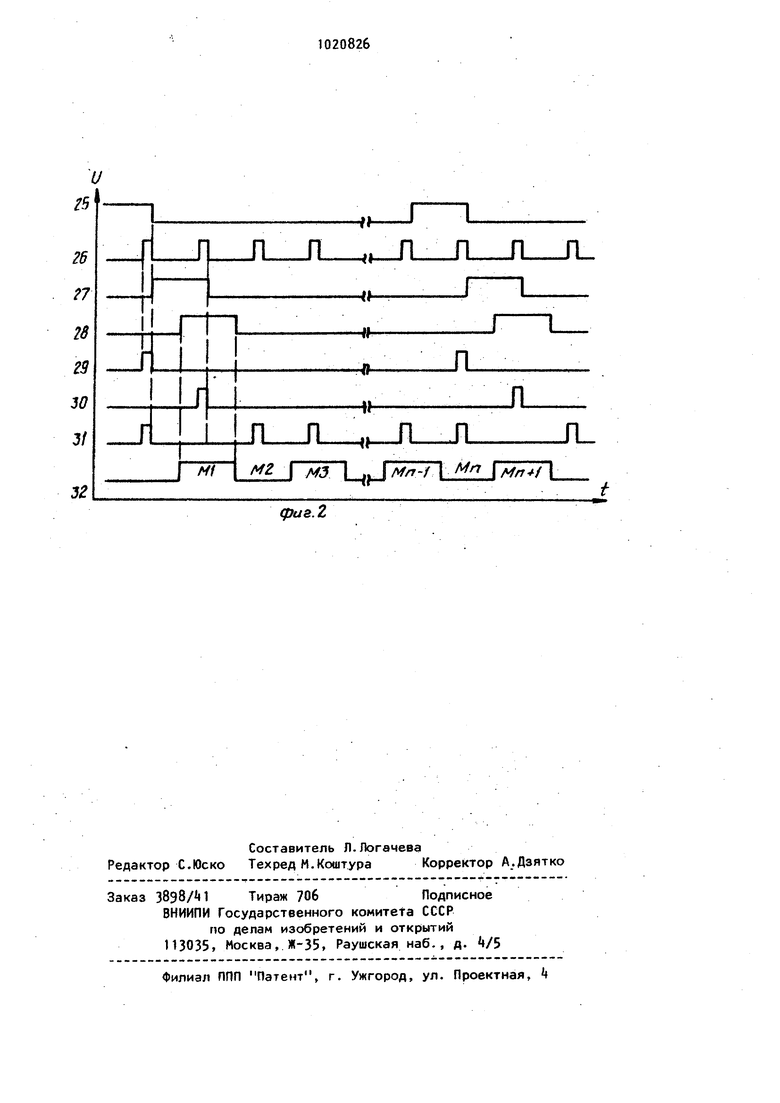

iпамяти подключен к первому входу счетчика адреса, выход которого через второй дешифратор соединен с адресным входом второго блока памяти, первый выход которого является выходом устройства, а второй выход соединен с вторым входом счетчика микрокоманд и вторым входом счетчика адреса, вход установки нуля которого соединен с вторым входом первого дешифратора, входом установки нуля буферного регистра и выходом третьего элемента. И, первый вход которого подключен к выходу первого элемента И и через элемент НЕ к первому входу четвертого элемента И при этом второй вход второго элемента И соединен через элемент задержки с вторым входом третьего элемента И и выходом второго элемента задержки, вход которого подключен к выходу генератора тактовых импульсов и второму входу четвертого элемента И, выходом соединенного с вторым входом второго дешифратора. Четвертый выход пе|эвого блока памяти соединен с входом установки нуля регистра адреса, второй вход которого является входом кода операций устройства, первые входы элементов И первой группы являются входами логических условий устройства. Вход установки в нуль регистра логических условий соединен с выходом третьего элемента И, информационный вход с выходом дешифратора логических условий, входы которого соединены с вторым и третьим выходами первого блока памяти, при этом выходы регистра логических условий соединены с вторыми входами элементов И первой группы 2. Недостатком известного устройства является низкая производитель.ность. Это обусловлено тем, что при каждом переходе от одной последовательности выполнения микрокоманд к другой производится перезапись управляющих слов из первого блока памяти в регистры и счетчики устройства. При этом каждый раз непроизво дительно расходуется мйкрокомандный ЦИКЛ. Цель изобретения - повышение про изйодительности устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее первый и второй блоки памяти, регистр адре са, буферный регистр, регистр логических условий,счетчик адреса, счет чик микрокоманд, первую и вторую группы элементов И, группу элементов ИЛИ, перйый, второй, третий и ;четвертый элементы И, элемент НЕ, элемент задержки и генератор тактовых .импульсов, причем выход числа микрокоманд первого блока памяти соединен с информационным входом счетчика микрокоманд, выход которого через первый элемент И соединен с первым входом второго элемента И, второй вход которого соединен с пер выми входами третьего и четвертого элементов И и с выходом генератора тактовых импульсов, адресный выход первого блока памяти соединен с ийформационным входом счетчика адреса выход которого соединен с/адресным входом второго блока памяти, выход логических условий первого блока па мяти соединен с информационным вход регистра логических условий, выход которого соединен с первыми входами элементов И первой группы, вtopыe входы которых соединены с входом условий устройства, а выходы соединены с первыми входами элементов ИЛ группы, вторые входы которых соедин ны с входом кода операций устройств а выходы соединены с установочным входом буферного регистра, выход ко торого соединен с информационным вх дом регистра адреса, выход которого соединен с адресным входом первого блока памяти, выход косвенного адре KOTdporo соединен с информационным входом буферного регистра, выход вт рого элемента И соединен с вход занесения регистра адреса, выход третьего элемента И соединен с входами занесения счетчика адреса, буфер- . ного регистра и регистра логических условий, дополнительно введены третья группа элементов И, вторая группа элементов ИЛИ и триггер,информационный вход которого соединен с выходом первого элемента И, вход занесения - с выходом генератора такTOBbJX импульсов, а прямой выход - с вторым входом третьего элемента И и с входом элемента задержки, выход которого соединен с первыми входами элементов И второй группы ичерез элемент НЕ соединен с первыми входами элементов И третьей группы,вторые входы которых соединены с выходом второго блока памяти, а выходы с первыми входами элементов ИЛИ второй группы, выходы которых являются операционным выходом устрсйства,вторые входы элементов ИЛИ второй группы , соединены с выходами элементов И второй группы, вторые входы которых соединены с операционным выходом первого блока памя1ти, ийход третьего элемента И соединен с входом занесения счетчика микрокоманд, счетный вход которого соединен со счетным входом счетчика адреса и выходом четвертого элемента И, вход которого соединен с инверсным выходом три1- гера, вход начальной установки устройства соединен с вх:одами сброса счетчика микрокоманд, триггера, регистра логических условий и буферного регистра. На фиг.1 представлена схема устройства; на фиг. 2 - временная диаграмма работы устройства. Микропрограммное устройство управления содержит регистр 1 логических условий, группу элементов И2, вход 3 которой является входом условий устройства, группу элементов ИЛИ k, вход 5 которой является входом кода операций устройства,буферный регистр 6,регистр 7 адреса, блок 8 памяти, группу элементов И 9, группу элементов ИЛИ 10, выход 11 которой является операционным выходом устройства, элемент 12 задержки, элемент НЕ 13, группу элементов И И, счетчик 15 микрокоманд, элементы И 16-19, счетчик 20 адреса, блок 21 памяти, триггер 22, генератор 23 импульсов и вход 2 начальной установки. На фиг.2 показана временная диаграмма работы устройства, где 25 сигнал на выходе элемента И 16; 26 импульсы на выходе генератора 23 импульсов; 27 - сигнал на выходе тригVepa 22; 28 - сигнал на выходе элемента 12 задержки; 29 - импульсы на выходе элемента И 17; 30 импульсы на выходе элемента И 18; 31 - импульсы на выходе элемента И 19; 32 коды микрокоманд на выходе 11 устройtoства .

Устройство работает следуклцим образом.

Для приведения устройства в исходное состояние на вход 2 подается

ts сигнал начальной установки, по которому буферный регистр 6, регистр 1 логических условий, счетчик 15 микрокоманд и триггер 22 устанавливаются в нуль.

20

На вход 5 устройства подается код операции, который поступает через группу элементов ИЛИ k на установочный вход буферного регистра 6 и задает начальный адрес микропрограммы.

25 Так как содержимое счетчика 15 микрокоманд равно нулю, сигнал 25 имеет единичное значение.

Генератор 23 импульсов вырабатывает импульс 26, по которому вырабатываются импульсы 29 и 31 ,а триггер 22 при ° единичном значении сигнала 25 устанавливается в единицу (все действия в устройстве выполняются по задним фронтам импульсов). Сигнал 27 принимает единичное значение. 35

По импульсу 31 производится уменьшение на единицу содержимого счетчика 15 ми1фокоманд, в результате чего сигнал 25 принимает нулевое значение

40 По импульсу 29 начальный адрес из буферного регистра 6 переписывается в регистр 7 адреса, однако микрокомандана выходе блока 8 памяти появляется через время t ,определяе45мое временем выборки из памяти. Через это же время на выходе элемента 12 задержки вырабатывается единичный сигнал 28, по которому открывается группа элементов И 9- Группа элементрв И Ц закрывается

50 сигналом с выхода элемента НЕ 13С первого выхода блока 8 памяти на информационный вход счетчика 15 микрокоманд поступает код, значение

55 которого на единицу меньше числа микрокоманд в текущей последовательности. С второго выхода блока 8 памяти на информационный вход с,четчика 20

адреса поступает адрес второй микрокоманды текущей последовательности: С третьего выхода блока 8 памяти на информационный вход регистра 1 ло.гических условий поступает код логических условий, проверяемых при реализации текущей последовательности. С четвертого выхода блока 8 памяти на информациЬнный вход буферного регистра 6 поступает косвенный адрес первой микрокоманды следующей последовательности.С пятого выхода блока 8 памяти через группы элементов И 9 и ИЛИ 10 на выход 11 устройства поступает операционная часть первой микрокоманды М, текущей последовательности (поз.32). В операционной части микрокоманды кодируются микроприказы, осуществляющие воздействие не управляемую микропрограммным устройствам систему.

По следующему импульсу 26 вырабатывается импульс 30, а триггер 22 устанавливается в нуль. По импульсу 30 управляющие слова:с выходов блока 8 памяти переписываются в регистры и счетчики устройства. Через время б в соответствии, с нулевым значением сигнала 27 сигнал 28 также принимает нулевое значение в результате чего группа элементов И 9 закрывается, а группа элементов И Ik открывается. По содержимому счетчика 20 адреса из блока 21 памяти выбирается операционная часть второй микрокоманды М2.текущей последовательности. Код операционной части микрокоманды М2 через группы элементов И И и ИЛИ 10 поступает на вход 11 устройства (поз.32).

При поступлении каждого следующег импульса 26 вырабатывается импульс 31, по которому производится изменение на единицу содержимого счетчика 15 микрокоманд и счетчика 20 адреса. В соответствии со значением адреса s счетчике 20 адреса из блока 21 памяти считывается следующая микрокоманда и поступает на выход 11 устройства. В процессе выполнения текущей последовательности микрокоманд на вход 3 устройства из ynpas- v ляемой системы поступают сигналы логических условий. Сигналами с выхода регистра 1 логических условий открываются соответствующие элементы И группы элементов И 2, сигналы с выходов которой через группу элемен7тов или k изменяют адрес, на буферном регистре 6. . Если при поступлении очередного импульса 31 содержимое счетчика 15 микрокоманд оказывается равным нулю то сигнал 25 принимает единичное значение. При этом по содержимому счетчика-20 адреса из блока 21 памя ти считывается и поступает на выход 11 устройства последняя микрокоманда текущей, последовательности(поз. 32 При поступлении следукэдего импуль са 26 триггер 22 устанавливается в единицу, а по импульсу 29 адрес из буферного регистра 6 переписывается в регистр 7 адреса. По этому адресу из блока 8 памяти считывается управляющее слово и поступает на информационные входы регистров и счетчиков устройства. По единичному значению сигнала 28 открывается группа элементов И 9 и на выход II устройПJ Л- 1-

фиг1

7/ Ч. ТРк 26 ства передается операционная часть первой микрокоманды спедующей последовательности с пятого выхода блока 8 памяти. В дальнейшем работа устройства выполняется аналогично вышеописанной. Таким образом, предлагаемое устройство позволяет осуществлять переходы от одной последовательности микрокоманд к другой без потери времени на перезапись управляющихслов в регистры и счетчики устройства, в отличие от протртипа, где при этом каждый раз непроизводительно расходуется микрокомандный цикл. Предлагаемое устройство позволяет осуществлять переходы от одной последовательности выполнения микрокоманд к другой без потерь времени на перезапись управляющих слов, необходимых для выполнения новой последовательности микрокоманд. П п п п п „ п П I 1 1 iii« 1 1 I Ml мг мз мп-1 f

(J}U8.2 пл л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1978 |

|

SU763898A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1977 |

|

SU703811A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-17—Подача