Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управления ЭВМ. Известно микропрограммное устрой ство управления, содержащее два блока памяти, регистры, логические элементы И и НЕ, элементы задержки, счетчики, дешифраторы и генератор тактовых импульсов 1 . Недостатком известного устройства является низкая экономичность, которая Обусловлена большим объемом блоков памяти и большой разрядностью счетчика микрокоманд. Большой объем запоминающих блоков приводит к ограничению функциональных возмож ностей устройства за счет снижения объема реализуемых микропрограмм. . Большая разрядность счетчика микрокоманд приводит к усложнению схемы устройства и снижению его функциональной надежности за счет большого числа переключений .элемен тов памяти в каждом состоянии. Наиболее близким по технической сущности и достигаемому поло:житель ному эффекту из известных микропро раммных устройств является устройство микропрограммного управления р, содержащее последовательно соединенные регистр логических условий, первую группу элементов и, буферный регистр, вторую группу элементов И, регистр адреса, первый дешифратор и первый блок памяти, первый выход которого соединен со вторьлм входом буферного регистра, второй выход соединен со входом шифратора, четвертый выход соединен со входом установки в нуль регистра адреса; вторые входы первой группы элементов И соединены со входом устройства, а вторые входы второй группы элементов И соединены через последовательно включенные первый элемент И, первый и второй элементы задержки к выходу генератора тактовых импульсов, который соединен со вторьлм элементом И, второй вход которого через элемент НЕ соединен с выходом третьего элемента И, вторым входом первого элемента И и со входом четвертого элемента И, второй вход которого соединен с выходом второго элемента задержки, а выход подключен ко второму входу первого дешифратора, входу установки в нуль

буферного регистра и входу установки в нуль регистра логических условий, а также через последовательно соединенные счетчик адресов, второй .дешифратор, управляемый выходом четвертого элемента И, ко входу второго блока памяти, первый выход которого соединен с выходом устройства, второй выход соединен со вторым входом счетчика адресов, а выход счетчика микрокоманд соединен со входом третьего элемента И.

Недостатком этого устройства является низкая экономичность, котора обусловлена большим объемом запоминающих блоков и большой разрядностью счетчика микрокоманд.

Большой объем запоминающих блоко связан с увеличенным форматом адресных микрокоманд.

Большая разряд«ость счетчика микрокоманд обусловлена тем, что чило разрядов счетчика п. должно быть не менее числа ячеек во втором блоке памяти. Это приводит к увеличению сложности счетчика и, следовательно, снижению экономичности устройства.

Цель изобретения - сокращение оборудования.

Эта цель достигается тем, что в микропрограммном устройстве управления, содержащем регистр адреса, первый вход которого является первы входом устройства, и вход установки в нуль соединен с первым выходом первого блока памяти, выход - с первым входом первого дешифратора, выход которого соединен со входом первого блока памяти, второй выход которого соединен с первьм входом буферного регистра, третий выход со входом шифратора, первые входы элементов И первой группы являются группой входов устройства, вторая группа входов соединена с выходом регистра логических условий, а группа выходов - со второй входов буферного регистра, выход которого соединен с первылш входами элементов и второй группы, вторые входы которых соединены с выходом первого элемента И, выходы элементов И второй группы соединены с третьим входом регистра адреса, выход генератора тактовых импульсов соединен с первым входом второго .элемента И, через первый элемент задержки с первцм входом третьего элемента И и cqik входом второго элемента задержки выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом четвертого элемента И, со вторым входом третьего элемента И и через первый элемент НЕ соединен со вторым входом второго элемента И, выход которого соединен с первым входом второго дешифратора, первый

-ВХОД которого соединен с выходом счетчика адресов, а выход - со входом второго блока памяти, первый выход которого является выходом устройства; группа входов четверто элемента И соединена с группой выходов счетчика микрокоманд, выход третьего элемента И соединен с первым входом счетчика адресов, со вторым входом первого дешифратора, со входом установки в нуль буферного регистра и входом установки в нуль регистра логических условий; второй выход второго блока памяти соединен со вторым входом счетчика адресов, первый выход шифратора соединен с третьим входом счетчика адресов, второй выход - с первым входом счетчика микрокоманд, второй вход которого через второй элемент НЕ соединен со вторым выходом второго блока памяти, а четвертый выход первого блока памяти соединен со вторым входом регистра логических условий.

Сущность изобретения состоит в повышении экономичности устройства за счет снижения объема запоминающих блоков и уменьшения разрядности счетчика микрокоманд.

Снижение объема запоминающих блоков достигается заданием в формате адресной микрокоманды кода номера текущей последовательности, кода номера следующей последователности и кода логических условий. Поскольку разрядность кода номера последовательности меньше кода адреса первой микрокоманды последовательности, то это позволяет уменьшить формат адресной части микрокоманды, а следовательно, повысить экономичность устройства.

Уменьшение разрядности счетчика микрокоманд достигается за счет соединения второго выхода блока памяти через второй элемент НЕ со вторым входом счетчика микрокоманд.

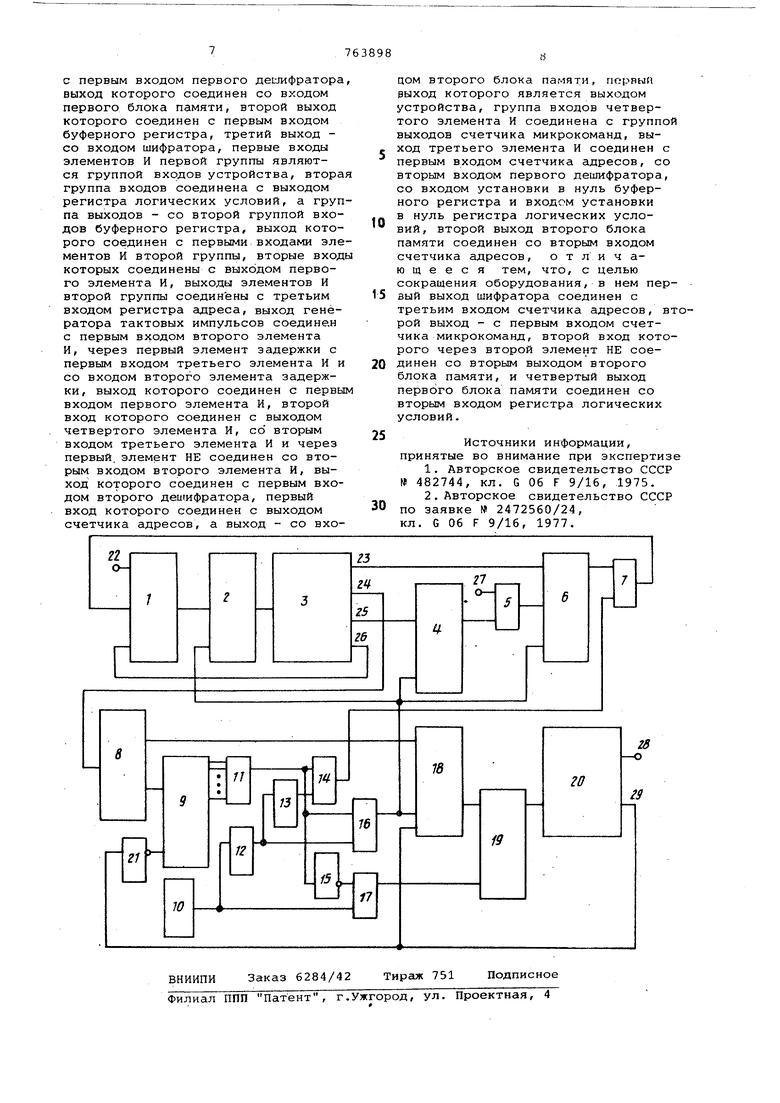

На чертеже представлена схема микропрограммного устройства управления .

Устройство содержит регистр адреса 1, первый дещифратор 2, первы блок памяти 3, регистр -логических условий 4, первую группу элементов И 5, буферный регистр 6, вторую группу элементов И 7, шифратор 8, счетчик микрокоманд И, генератор тактовых импульсов 10, первый элемент И 11, первый элемент задержки 12, второй элемент задержки 13, второй элемент И 14, первый элемент НЕ 15, третий элемент И 16 четвертый элемент И 17, счетчик адреса 18, второй дешифратор 19, второй блок памяти 20 и второй элемент НЕ 21.

Символом 22 обозначен вход установки кода (номера) Ьперации; 23, 24, 25, 26 - первый, второй,- трети и четвертый выходы первого блока памяти соответственно; 27 - вход логических условий; 28, 29 - первый и второй выходы второго блока памяти соответственно.

Рассмотрим работу устройства,

В исходном состоянии все элементы памяти находятся в нулевом состоянии.

Код (номер) операции через вход 22 поступает на регистр адреса 1 и задает адрес соответствующей ячейки в первом блоке памяти 3.

Генератор 10 через элемент задерки 12 и элемент И 16 при наличии сигнала разрешения с выхода элемента И 17, соответствующего показанию счетчика микрокомандг равного нулю, производит установку в нуль счетчика адреса 18, регистра логических условий 4 и буферного регистра 6, а также осуществляет пуск дешифратора 2. По сигналу дешифратора 2 с блока 3 считывается адресная. часть микрокоманды. С выхода 23 в регистр б записывается косвенный номер следующей последовательности микрокоманд. С выхода 25 и регистра 4 записывается код проверяемых логических условий. Сигнал с выхода 26 устанавливает в исходное состояние регистр 1. Одновременно сигнал с выхода 24, соответствующий номеру текущей последовательности, поступает на вход шифратора 8, с выходов которого в счетчик микрокоманд 9 записывается признак длины последовательности, а в счетчик адресов 18 - адрес первой микрокоманды текущей последовательности.

После считывания из первого блока Пс1Мяти 3 импульс генератора 10 через элементы задержки 12 и 13, элемент И 11 открывает вторую группу элементов И 7 и разрешает перезапись информации с регистра б на регистр 1.

После считывания адресной части микрокоманды и записи в счетчик 9 кода числа микрокоманд показания счетчика 9 отличны .от нуля. Сигнал на выходе элемента И 17 принимает нулевое значение и через элемент НЕ 15 открывает элемент И 14. Через элемент И 14 следующий тактовый импульс генератора 10 запускает деишфратор 19. Далее по каждому тактовому импульсу в соответствии с адресом, записанным в счетчике 18, из блока памяти 20 считывается операционная микрокоманда. С выхода 28 блока 20 считываются сигналы микроопераций, а с выхода 29 считывается сигнал, который осуществляет увеличение (уменьшение) на единицу содержимого счетчика адреса 18 (счетчика микрокоманд 9). При показаниях счетчика 9, отличных от нуля, следующий тактовый импульс аналогично описанному {осуществляет считывание операционной микрокоманды из блока 20,

В процессе работы устройства.сигналы с выходов элементов И первой группы 5 изменяют показания регистра б .

0

Если показания счетчика 9 равны нулю, то импульс генератора 10 через элементы задержки 12 и 13, элемент И 11 и вторую группу элементов К 7 передает адрес следующей адрес5ной дакpoкoмaнды с регистра 6 на регистр 1.

Следукщий импульс генератора 10 через элемент задержки 12 и элемент И 16 устанавливает в исходное

0 состоя.ние счетчик 18, регистр логических условий 4 и буферный регистр 6. Кроме того, осуществляется запуск дешифратора 2, считывается микрокоманда из блока 3 и работа устройства осуществляется аналогично ойисанном вьпие.

Соединение первого выхода шифратора с третьим входом счетчика адресов, второго выхода - с первым

0 входом счетчика микрокоманд, второй вход которого через второй элемент НЕ соединен со вторым выходом второго запоминакяцего блока, а также подключение четвертого выхода первого запоминающего блока ко входу регистра логических условий позволяет повысить эконогличность устройства. Это позволяет расширить функциональные возможности устройства за счет реализации микропрограмм большего объема.

Соединение второго входа счетчика микрокоманд через второй элемент НЕ со вторым выходом второго запоминающего блока позволяет существен5но уменьшить разрядность счетчика микрокоманд за счет записи в счетчик кода признака длины последовательности микрокоманд, а на коде числа микрокоманд в последователь0ности. Это следует из того, что возможное значение кода числа микрокоманд в последовательности значительно превосходит возможное зн-ачение кода признака длины последо5вательности микрокоманд.

Формула изобретения

MKKponporpaMN5Hoe устройство управления, содержащее регистр адреса, первый вход которого является первым входом устройства, а вход установки в нуль соединен с первым выходом первого блока памяти, выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1977 |

|

SU703811A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

| Устройство микропрограммного управления | 1980 |

|

SU960814A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

Авторы

Даты

1980-09-15—Публикация

1978-06-23—Подача