I

Изобретение относится к области вычиспитепьной техники и может быть использовано при построении цифровых вычислительных машин.

Известно микропрограммное устройство управления, содержащее два блока памяти, регистры, триггеры, элементы И, блоки проверки условий ll . Недостатками этого устройства являются низкие экркомичность и эксплуатационные качества, обусловленные большой разрядностью блоко памяти...

Наиболее близким к изобретению техническим решением является микропрЬ ПpaMNraoe устройство управления, содержащее первую группу элементов И, выходы которых соединены с первыми входйми буферного регистра, выходом соединенного с первыми входами элементов И второй группы, выходы которых соединены с первыми входами регистра адреса. Причем выход регистра апреса подключен к первому входу первого дешифратора, выходом соединенного с входом первого

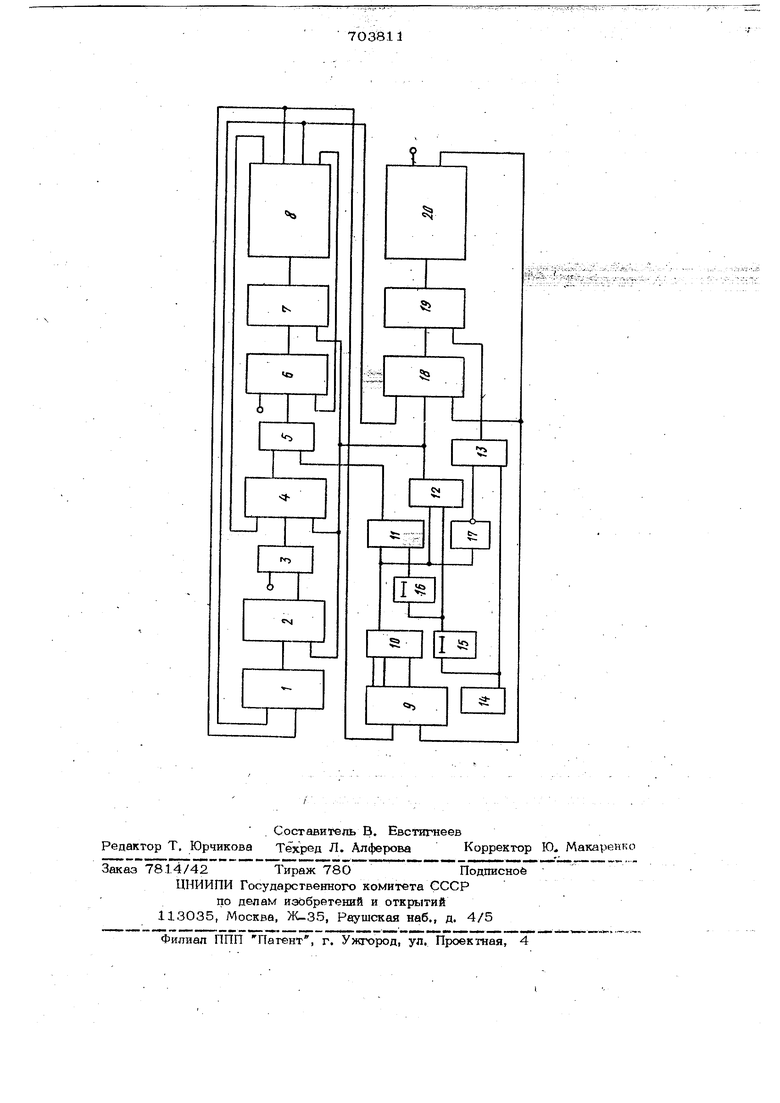

блока памяти, первый выход которого соединен с вторым в;ходом буферного регистра, второй выход - с входом счеть. чика микрокоманд,ваходы счетчика микрокомард через первый адемент И соединены с первым входом второго элемента И, выходом соединенного с вторыми входами элементов И второй группы, третий BJЬIXoд первого блока памяти подключен к первому входу ечетчнка адреса, выходкоторого через второй дешифратор соединен с входом второго блока памяти, первый эыход последнего является выходом устройства, а второй выход соединен с вторым входом счетчика микрокоманд и вторым входом счетчика адреса, вход новки нуля которого соединен с BTOIM IM входом пепвого децщ ратора, входом установки нуля буферного регистра и выходом третьего элемента И. При этом первый вход третьего элемента И соединен с выходом первого элемента И и через элемент НЕ с первым входом четвертого элемента И, второй вход второ1х эл мрнта И соединен через элемент задержки с вторым входом гретьегх) элемента И и выходом второго элемента задержки, вход которого подключен к выходу генератора тактовых импульсов и второму входу четвертогЬ элемента И, выходом соединенного с вторым входом второго дешифратора, четвертый выход первого блока памяти соединен с входом установки нуля регистр ра адреса, второй вход которого является входом кода бпёраций устройства, первые входы элементов И первой группы являются входами логических условий устройства 2 . Недостатком этого устройства являет ся низкая экономичность, обусловленная значительной разрядностью слов второго блока памяти, в котором хранятс операционные части микрокоманд.. Разрядность второго блока памяти Пд, определяется следующим выражением: ,; где h. - разрядность ttona операционной части, задающего сигналы микроопераций управления; h - разрядность поля операционной части, задающего коды проверяемых логических усло „я Задание в слове второго блока памяти кода логических условий приводит к снижению .гибкости микропрограммирования и ограничению мощности микрокоманд, определяемой количеством микроопераций управления, задаваемых в одной микрокоман де.. Кроме, того, моди4йкация алгоритмов работы устройства (микропрограмм) можёт потребовать, чтобы при наборе микроопераций управления проверялись другие логические условия/ этом случае в данном устройстве кроме смены первого блока памяти задающегю ащюса требуется замена и второго (операционного) блока памяти. Это снижает гибкост устройства, приспособлещюсть к модернизайии, ухудщая тем самым его эксплуатаЮгонные качества. Целью изобретения является повышени гибкости и уменьшение аппаратурных затрат. Поставленная цель достигается тем, что устройство дополнительно содержит дешифратор логических условий и регистр логических условий, вход установки в eyjib кртбрс(го oeдинeн с выходом третье го элемента И, 1нф0рманионный вход - с ВЫХОДОМ дешифратора логических условий, при этом входы последнего соединены с вторым и третьим выходами первого блока памяти, выходы регистра логических условий соединены с вторыми входами элементов И первой группы. На чертеже представлена блок-схема устройства, которое содержит дешифра тор 1 логических условий, регистр 2 логических условий, первую группу элементов И 3, буферный регистр 4, вторую группу элементов И 5, регистр 6 адреса, дешифратор 7, блок памяти 8, счетчик-. 9 микрокоманд, элементы 10-13; генератор 14 тактовых импульсов, элементы задержки 15 и 16, элемент НЕ 17, счетчик 18 адреса, дешифратор 19, блок памяти 20. Сущность изобретения состоит в осуществлении идентификации проверяемых логических условий по адресу первой микрокоманды и количеству микрокоманд и текущей последовательности. Знание этих двух признаков позволяет однозначно определить условия, которые должны проверяться при реализации данной последовательности микрокоманд. Соединение второго и третьего выходов блока памяти с входами дешифратора логических условий позволяет сформиро- вать признак логических условий.на основании анализа сочетания кодов адреса первой микрокоманды и количества микрокоманд в последовательности. Соединение выходов дешифратора с входами регист ра логических условий предназначено для передачи признака логических условий на регистр логических .условий. Регистр логических условий запоминает указанный признак на время реализации данной последовательности микрокоманд и передает его для анализа выполнения на входы элементов И первой группы. Соединение входа установки нуля регистра логических условий с выхода третьего элемента И предназначено для установки в нуль регистра логических условий перед считыванием новой микрокоманды из первого блока памяти. В первом блоке памяти устройства запоминается адрес операционной части первой микрюкоманды текущей последовательности, косвенный адрес первой микрокоманды следу- ющей последовательности и количество микрокоманд в текущей последовательности. Один разряд микрокоманды из блока ггамяти по четвертому выходу осз-ществляет сброс регистра адреса. Во втором блоке памяти записаны опе рационные части микрокоманд, которые могут выбираться в любой последователь кости и выполняются подряд в количестве задаваемом микрокомандой из первого блока памяти. Один разряд из второго блока памяти осуществляет прибавление единицы к содержимому счетчика адреса второго блока памяти и вычитание из счетчика микрокоманд. Введение регистра и дешифратора логических условий, .а также указанных связей позволяет сократить разрядность микрокомавиы, повысить такие эксплуатационные качества микропрограммного устройства управления, как гибкость и приспособленность к модернизации. Устройство работает следующим образом, В исходном состоянии все элементы памяти находятся в нулевом состоящий. Код операции лрступает на второй вхо регистра 6 адреса и задает адрес соотве ствующей ячейки в блоке памяти 8. I Генератор 14 через элемент задержки 15 и элемент И 12 при разрешения с элемента И 10 (при показании счетчика 9 микрокоманд, равном нулю) производит установку в нуль счетчика 18 адреса буферного регистра 4, регистра 2 логических условий и, кроме того, произво дят пуск дешифратора 7. Тем самым считывается соответствующее слово из блока 8. С первого выхода блока 8 в буферный регистр записывается косвенный адрес первой микрокоманды следующей последовательности, С второго выхода блока 8 в счетчик 9 микрокоманд записывается код количества микрокоманд в текущей после.довательнОсти. С третьего выхода блока 8 в счетчик 18 адреса записывается адрес первой микрокоманды теку Шей последовательности. Одновременно сигналы с второго и третьего выходов блока 8 поступают на входы дешифратора 1, который формирует признак логических условий, проверяемых при реализации данной последовательности микрокоманд, и записывает его в регистр 2 логических условий Сигнал с четвертого выхода блока 8 уста навливает регистр 6 адреса в нуль. После считывания из блока 8 импульс генератора. 14 через элементы задержки 15 и 16, элемент И 11 и вторую групп элементов И 5 передает адрес из буферного регистра 4 на регистр адреса. Поскольку после считывания из блока б и записи в счетчик 9 микрокоманд кода количества микрокоманд Показание счетчика 9 уже не равно нулю, то выход ным сигналом элемента И 10 «iepes але. мент НЕ 17 открывается элемент И 13. Следующий импульс генератора 14 зб пускает дешифратор 19 и в соответствии с адресом на счетчике 18 из ,блока памяти 20 считывается первая М1жрок6ман да. С первого выхода блока 2 О считываются сигналы микроопераций управления, а с второго выхода - единичный сигнал. Этим сигналом осуществляется увеличение (уменьшение) на единицу содержимого счетчика 18 адреса (счетчика 9 микрокоманд). Бели при этом показания счетчика микрокоманд отличны от нуля, то следую щий импульс генератора 1 4 снова запускает через элемент И 13 дешифратор 19 и аналогично считывается мшсрокоманда из блока 20. Если же пока-, зания счетчика микрокоманд равны нулю, то импульс генератора14 через элементы гдержки 15 и 16 передает адрес из буферного регистра 4 через группу элементов И 5 в регистр 6 адреса. Тем самым подготавливается считывание из блока 8. При показании счетчика микрокоманд, равном нулю, следующий импульс генератора 14 через элемент задержки 15 и; элемент И 12 устанавливает в нунь счет чик 18 адреса, регистр 2 логических условий и буферный регистр 4 и осуществляет пуск дешифратора 7. При этом считы вается микрокоманда из блока 8 и работа устройства осуществляется аналогично описанному выше. Для проведения условных переходов на входы группы элементов И 3 подключень выходы регистра,логических условий, сигналы свыходов которого опрашивают соответствующие логические условия, поступающие в процессе функционирования устройства на входы 21 элемента И первойгруппы. Сигналы с выходов элементов И первой группы изменяют адрес на буферном регистре 4. Использование новых элементов - дешифратора и регистра логических условий позволяет уменьшить аппаратурные затраты йа уртройстгео, что обусловлено снижением разрядности блока памяти операционных микрокоманд. Разрядность второго блока памяти И 2 .определяется следующим выражением: В устройстве все разряды слова, кроме одного, могут быть испопьзораны в . . 7 --.,-.-.....-..-...,..... , качестве упрйвляюашх, что способствует повышению гибкости микропрограммированй й и мощности операШюнных микрокоманд.; Кроме гогчэ, устройство имеет более высойие эксплуатационные характеристики за счет лучшей приспособленности к модернизации и большей гибкости. Формула изобретенияМикропрограммное устройство управления; содержащее первую труппу эле-1 ментов И, выходы которых соединены с первыми входами буферного регисГрй, вы ™ШЗДййГШ%)5тёйнб1 д1C первй элементов И второй группы, выходы которык соединены с пё рвыми, входами регистра адреса, причем выход регистра адреса подключен к первому nepekjго дешифратора, выходом соединённого с адресным вз ;одом первого блока памяти, первый выход которого соединен с вторым входом .буферного i регистра, второй }fXftt Viit рокоманд, выходы которого через первый элемент И соединены с первым входом 1(Торог) Элемента И, бйяэдбм CoeflEf|tH№ го с вторыми входами элементов И второ группь, третий выход первого блока памяти по арключен к первому входу счётчика 1адр1еса,вы:йод к6т6ро1 ёрЪ ; вто шифратор соединен с входом второго блока памяти, первый выход которотчэ является выходом устройства, а втЪрой выхо Ш|ЙШШё;вТбры1М входом счетчика мин: рокоманд и вторым входом , мЬд у соединен с вторым входом первого дешифраi8тора, входом установки 1гуля буферного регистра и выходом третьего элемента И, первый вход которого подключен к выходу первого элемента И и через элемент НЕ к первому входу четвертого элемента И, при Э.ТОМ второй вход второго элемента И соединен через элемент задержки с вторым входом третьего элемента И и выходом второго элемента задержки, вхой которого подключен к выходу генератора тактовых импульсов и второму входу четвертого элемента И, выходом соединенного с BTOptfM Входом второго дешифратора, четвертый выход первого блока памяти соединен с входом установки нуля регистра адреса, второй вход которого является входом кода операций устройства, первые входы элементов И первой fpyrtnibiv являются входами логических условий устройства, отпичаюшее с я тем, что, с целью повышения гибкортй и уменьшения аппаратурных затрат, оно дополнительно содержит дешифратор логических условий и регистр логических условий, установки в нуль которого соединен сВЫХОДОМ третьего элемента И, информационный вход - с выходом де-. шифратора пбгичёских условий, входы которого соёдйнёнЬ с вторым и третьим выходами первого блока памяти, при этом выходы регистра логических условий соеЙйнеш свторыми входами элементов И первой групйы. ,.:. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 43707Й, кл. Q 06 F 9/12, 1974. 2.Авторское свидетельство СССР № 482744, кл. Q 06 F 9/16, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1978 |

|

SU763898A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Устройство микропрограммного управления | 1980 |

|

SU960814A1 |

s nffyf kiSKfftv

iibSSJE,- Z-S - йгл- л «V :

Авторы

Даты

1979-12-15—Публикация

1977-04-04—Подача