(5)МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров ЭВМ.

Известно микропрограммное устройство управления, содержащее два блока памяти, буферной и адресный регистрь, счетчик микрокоманд, дешифраторы, генератор импульсов, элементы задержки и логические элементы И, НЕ 1.

Недостатком указанного устройства является сложность, низкая универсальность, отсутствие контроля правильности работы.

Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является микропрограммное уст|эойство управления, содержаицее регистр логических условий, первый блок элементов И, буферный регистр, второй блок элементов И, первый регистр адреса, первый и второй дешифраторы, первый и

второй блоки памяти, счетчик адреса счетчик микрокоманд, генератор тактовых импульсов, первый, второй и третий элементы И, элемент НЕ, первый и второй элементы задержки, причем выход генератора импульсов соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом- элемента. НЕ, вход ко10торого соединен с выходом третьего элемента И и вторым входом первого элемента И, выход первого элемента задержки соединен с входом второго элемента задержки, установочный вход

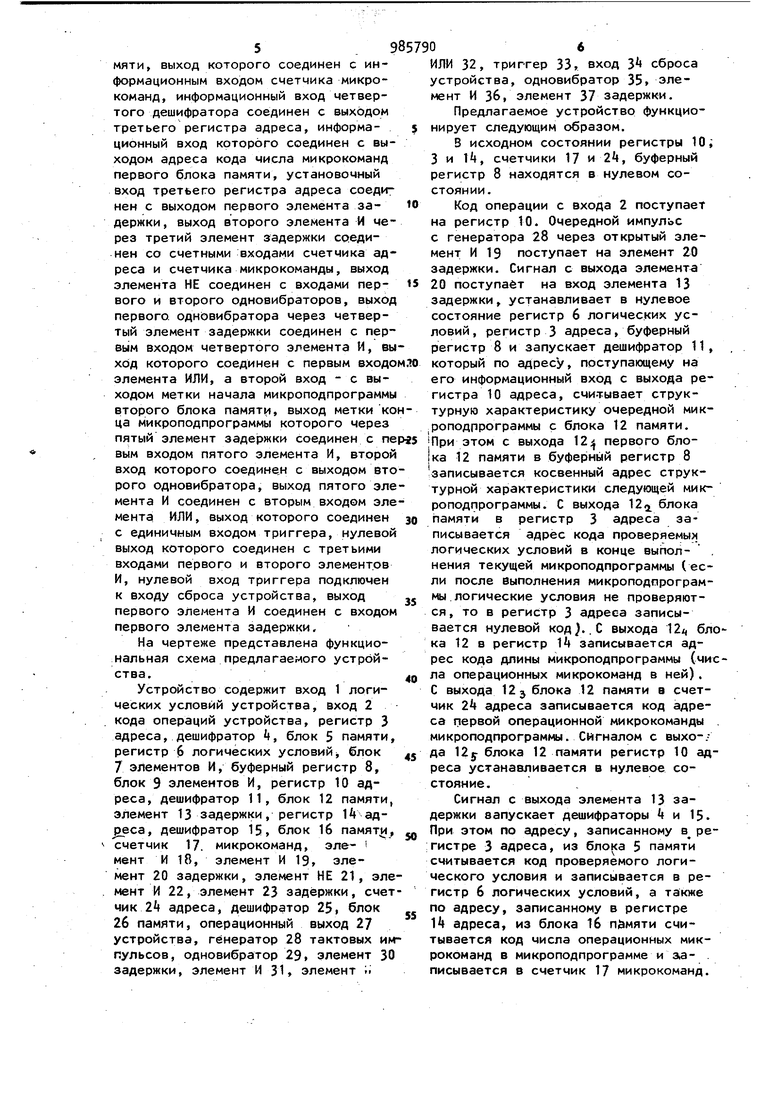

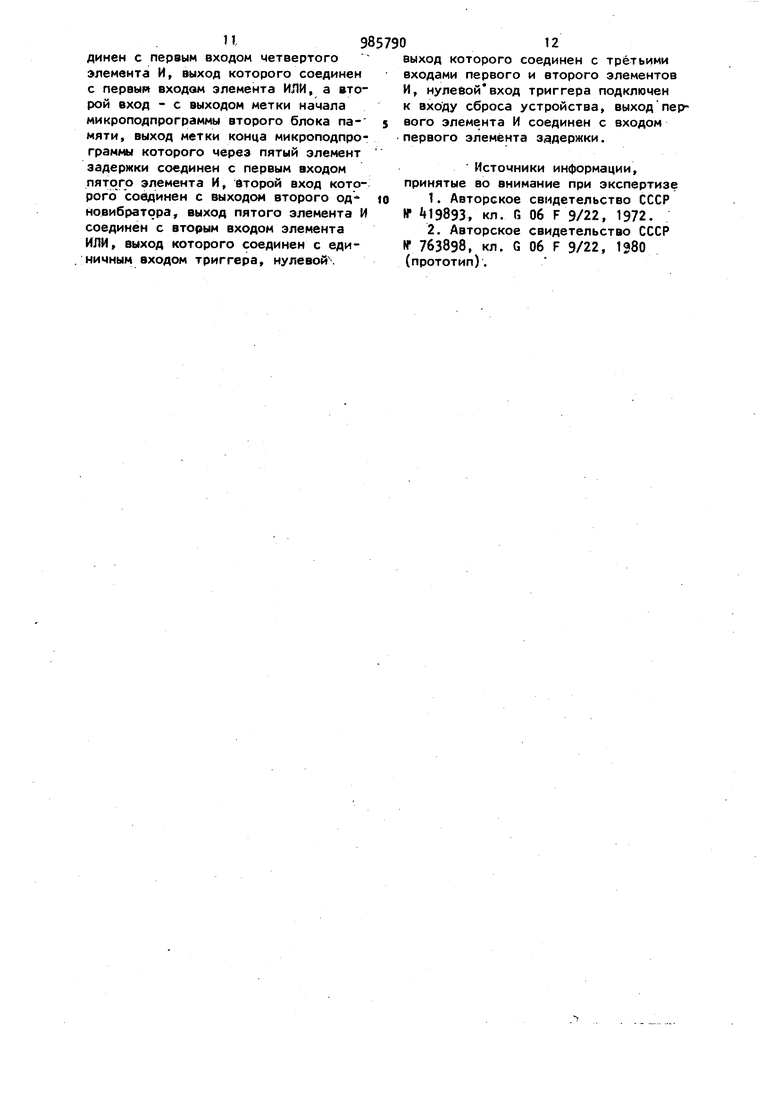

15 счетчика адреса соединен с первым входом первого блоки элементов И, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с первым ин20формационным входом первого регистра адреса, второй информационный вход которого является внешним входом устройства, установочный вход соединен с первым выходом первого блока памят а выход - с информационным входом пе вого Дешифратора, выход которого сое динен с входом первого блока памяти, второй выход которого соединен с пер вым информационным входом буферного регистра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход котор го является входом кода логических условий,.а второй вход соединен с вы ходом регистра логических условий, установочный вход которого соединен с установочным входом буферного регистра и управляющим входом первого дешифратора, третий вход первого блока памяти соединен с информационным входом счётчика адреса, выход которого соединен с информационным входом второго дешифратора, управляющий вход которого соединен с выходом второго элемента И, а выход с входом второго блока памяти, выход которого является выходом устройства, выходы счетчика микрокоманд соединены с входами третьего элемента И fz Недостатками этого устройства являются низкая универсальность, которая обусловливает неудобство эксплуатации и низкую приспособленность к модернизации,и отсутствие контроля пр вильности функционирования устройства Цель изобретения - повышение достоверности функционирования микропрограммного устройства управления. Поставленная цель достигается тем что микропрограммное устройство управления, содержащее регистр логичес ких условий, первый и второй блоки элементов И,буферный регистр, первый регистр адреса, первый и второй дешифраторы, первый и второй блоки памяти, счетчик адреса, счетчик микрокоманд, генератор тактовых импульсов первый, второй и третий элементы И, элемен-т НЕ, первый и второй элементы задержки, причем выход генератора импульсов соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом третьего элемента И и вторым входом первого элемента И,выход первого элемента задержки соединен с входом второго эле мента задержкиj установочный вход счетчика адреса соединен с первым входом первого блока элементов И, ВЫХОД которого соединен с первым информационным входом первого регистра адреса ,второй информационный вход которс5го соединен с входом ко да операции, устройства, установочный вход - с выходом метки первого блока памяти, а выход - с информационным входом первого дешифратора, выход которого соединен с адресным входом первого блока памяти, выход косвенного адреса характеристик следующей микроподпрограммы которого соединен с первым информационным входом буферного регистра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход которого подключен к входу логических условий устройства, второй вход -- к выходу регистра логических условий, установочный вход которого соединен с установочным входом буферного регистра и управляющим входом первого дешифратора,выход начального адреса текущей микроподпрограммы первого блока памяти соединен с информационным входом счетчика адреса , выход которого соединен с информационным входом второго дешифратора, управляЮ1ций вход которого соединен с выходом второго элемента И, а выход - с адресным входом второго блока памяти, операционный выход которого подключен к выходу устройства, выходы счетчика микрокоманд соединены с входами третьего элемента И, дополнительно содержит третий ичетвертый блоки памяти,третий и четвертый дешифраторы, второй и третий регистры адреса, триггер, первый и второй одновибраторы, третий, четвертый и пятый элементы задержки, четвертый и пятый элементы И, элемент ИЛИ, причем информационный вход второго регистра адреса соединен с выходом адреса кода логических условий первого блока памяти, установочный вход - с выходом первого элемента задержки, а выход - с информационным входом третьего дешифратора, выход которого подключен к-адресному входу третьего блока памяти, выход кoтopo o соединен с информационным входом регистра логических условий, управляющий вход третьего дешифратора соединен с выходом второго элемента задержки и управляющим входом четвертого дешиф ратора, выход которого соединен с адресным входом четвертого блока памяти, выход которого соединен с информационным входом счетчика микрокоманд, информационный вход четвертого дешифратора соединен с выходом третьего регистра адреса, информационный вход которого соединен с выходом адреса кода числа микрокоманд первого блока памяти, установочный вход третьего регистра адреса соединен с выходом первого элемента задержки, выход второго элемента И через третий элемент задержки соединен со счетными входами счетчика адреса и счетчика микрокоманды, выход элемента НЕ соединен с входами первого и второго одновибраторов, выход первого, одновибратора через четвертый элемент задержки соединен с первым входом четвертого элемента И, вы ход которого соединен с первым входо элемента ИЛИ, а второй вход - с выходом метки начала микроподпрограммы второго блока памяти, выход метки ко ца микроподпрограммы которого через пятый элемент задержки соединен с ne вым входом пятого элемента И, второй вход которого соединен с выходом вто рого одновибратора, выход пятого эле мента И соединен с вторым входом эле мента ИЛИ, выход которого соединен с единичным входом триггера, нулевой выход которого соединен с третьими входами первого и второго элементов И, нулевой вход триггера подключен к входу сброса устройства, выход первого элемента И соединен с входом первого элемента задержки. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит вход 1 логических условий устройства, вход 2 кода операций устройства, регистр 3 адреса, дешифратор 4, блок 5 памяти, регистр 6 логических условий блок 7 элементов И, буферный регистр 8, блок 9 элементов И, регистр 10 адреса, дешифратор 11, блок 12 памяти, элемент 13 задержки, регистр 14 , дешифратор 15, блок 16 памяти, счетчик 17. микрокоманд, элемент И 18, элемент И 19, элемент 20 задержки, элемент НЕ 21, эле . мент И 22, элемент 23 задержки, счет чик 2 адреса, дешифратор 25 блок 26 памяти, операционный выход 27 устройства, генератор 28 тактовых им пульсов, одновибратор 29 элемент 30 задержки, элемент И 31, элемент ИЛИ 32, триггер 33, вход 3 сброса устройства, одновибратор 35, элемент И Зб элемент 37 задержки. Предлагаемое устройство функционирует следующим образом. В исходном состоянии регистры 10; 3 и k, счетчики 17 и 24, буферный регистр 8 находятся в нулевом состоянии. Код операции с входа 2 поступает на регистр 10. Очередной импульс с генератора 28 через открытый элемент И 19 поступает на элемент 20 задержки. Сигнал с выхода элемента 20 поступает на вход элемента 13 задержки, устанавливает в нулевое состояние регистр 6 логических условий , регистр 3 адреса, буферный регистр 8 и запускает дешифратор 11, который по адресу, поступающему на его информационный вход с выхода регистра 10 адреса, считывает структурную характеристику очередной микроподпрограммы с блока 12 памяти. При этом с выхода 12; первого 12 памяти в буферный регистр 8 записывается косвенный адрес структурной характеристики следующей микроподпрограммы. С выхода 12 2 блока памяти в регистр 3 адреса записывается адрес кода проверяемы} логических условий в конце выпол- , нения текущей микроподпрограммы (если после Выполнения микроподпрограмNj логические условия не проверяются, то в регистр 3 адреса записывается нулевой код}.. С выхода 2ц блока 12 в регистр 14 записывается адрес кода длины микроподпрограммы (числа операционных микрокоманд в ней). С выхода 12J блока 12 памяти в счетчик 24 адреса записывается код адреса первой операционной микрокоманды . микроподпрограммы. Сигналом с выхо-; да 125- блока 12 памяти регистр 10 адреса устанавливается в нулевое состояние. , Сигнал с выхода элемента 13 задержки запускает дешифраторы 4 и 15. При этом по адресу, записанному в регистре 3 адреса, из блока 5 памяти считывается код проверяемого логического условия и записывается в регистр 6 логических условий, а также по адресу, записанному в регистре 14 адреса, из блока 16 пймяти считывается код числа операционных микрокоманд в микроподпрограмме и аа- . писывается в счетчик 17 микрокоманд. При этом сигнал на выходе элемента И 18 становится равным нулю, а на выходе элемента НЕ 21 - единице. В данном случае возбуждается одновибратор 29 и выдает сигнал на вход элемента 30 задержки. Следующий тактовый импульс с выхода генератора 28 через открытый элемент И 22 поступает на элемент 23 задержки и на управ ляющий вход дешифратора 25. При этом происходит считывание с блока 26 памяти по адресу, записанному в счетчике 2 адреса, первой операционной микрокоманды микроподпрограммы. С вы хода 26 первое поле операционной микрокоманды (код микрооперацийj поступает на 27 устройства, сигнал с поля операционной микрокоманды (метка начала микроподпрограммы) .через выход 26 блока 2б памяти поступает на инверсный, вход элемента И 31 .Причем на первый вход элемента И 31 в это же время поступает сигнал с вы хода элемента 30. При этом на выходе элемента И 31, а следовательно, и на единичном входе триггера 33 сигнал отсутствует. Это соответствует исправному состоянию устройства. Если сигнал с выхода 262 блока 2б памяти отсутствует (что соответствует неисправному функционированию управляющей системы ), то сигнал с выхода элемента И 31 поступает через элемен ИЛИ 32 на единичный вход триггера 33 устанавливает его в единичное состоя ние. , При этом элементы И 19 и 22 закрываются по первому входу, тактовые импульсы с выхода генератора 28 на систему не поступают. После устранения отказа триггер 33 устанавливается в нулевое состояние сигналом на его нулевой вход с входа 3. Функционирование устройства продолжается. После считывания первой операционной микрокоманды при правильном функционировании системы импульс с выхода элемента 23 воздействует на счетный вход счетчика 2k адреса, увеличивая его содержимое на единицу и формируя таким образом адрес следующей операционной микроко.манды,и на счетный вход счетчика 17 микрокоманд. При этом его содержимое уменьшается на единицу и формируется код числа микрокоманд, оставшихся невыполненными. По следующему импульсу генератора 28 производится считывание следующей операционной микрокоманды текущей микроподпрограммы из блока 2б памяти. При выполнении всех остальных операционных микрокоманд система функционирует аналогично. При выполнении последней операционной микрокоманды текущей ми к ро под г программы с ее третьего поля через выход 263 блока 26 памяти считывается метка конца микроподпрограммы и поступает на элемент 37 задержки. После считывания последней микрокоманды счетчик 17 микрокоманд устанавливается в нуль. При этом на выходе элемента И 18 формируется сигнал, который открывает элемент И 19 и запускает через элемент НЕ 21 одновибратор 35. Если считывание микрокоманды происходит правильно (на выходе элемента И 36 Сигнал отсутствует ), то система переходит к выпол-нению следующей микроподпрограммы. Очередной тактовый импульс с генератора 28 через открытый элемент И 19 открывает блок 9 элементов И, через который адрес структурной характеристики следующей микроподпрограммы с буферного регистра 8 поступает в регистр 10 адреса. На .блоке 7 .элементов И происходит проверка значения логических условий, код которых записан в регистре 6 логических условий. Сигналы логических условий поступают с входа 1 устройства на второй вход блока 7 элементов И. Сигналы с выхода блока 7 элементов И модифицируют адрес структурной характеристики i-и микгч роподпрограммы, хранящейся в буферном регистре 8, в соответствии со зна чениями поступающих сигналов логических условий. Далее импульс выхода элемента 20 задержки запускает дешифратор 1 1 , который по адресу, записанному в регистре 10 адреса, считывает с блока 12 памяти структурную характеристику i-и микроподпрограммы. Далее устройство функционирует аналогично описанному выше алгоритму. Изменение одной из структурных характеристик микропрограммы требует замены только одного блока памяти что повышает универсальность, уменьшает стоимость модернизации и повышаг ет гибкость микропрограммирования. Раздельная запись параметров микропрограммы без повторений увеличивает степень информативного заполнения каждого блока памяти до единицы, что повышает экономичность си стемы. Неправильное считывание, передача или запись начального адреса линейной последовательности, числа микрокоманд в линейной последовательности, пропуск одной или нескольких микрокоманд, ложное считывание нескольких микрокомандфиксируются схемой контроля, и дальнейшее неправиль ное функционирование устройства прек ращается. Это повьпиает достоверность функционирования устройства. Формула изобретения Микропрограммное устройство управ ления, содержащее регистр логических условий, первый и второй блоки элементов И, буферный регистрi первый регистр адреса, первый и второй дешифраторы, первый и второй блоки памяти, счетчик адреса, счетчик микрокоманд, генератор тактовых импульсов первый, второй и третий элементы И, элемент НЕ, первый и второй элементы задержки, причем выход генератора тактовых импульсов соединен с пер вым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом третьего элемента И и вторым входом первого элемента И, выход первого элемента задержки соединен с входом второго элемента за|держки, установочный вход счетчика адреса соединен с первым входом первого блока элементов И, выход которого соединен с первым информационным входом первого регистра адреса, второй информационный вход которого .соединен с входом кода операции устройства, установочный вход - с выходом метки первого блока памяти, а выход - с информационным входом первого дешифратора, выход которого сое динен с адресным входом первого блока памяти, выход косвенного адреса характеристик следующей микроподпрограммы которого соединен с первым ин формационным входом буферного регист ра, второй информационный вход которого соединен с выходом второго блока элементов И, первый вход которого подключен к входу логических условий устройства, второй вход - к выходу регистра логических условии, установочный вход которого соединен с установочным входом буферного регистра и .управляющим входом первого дешифрато ра, выход начального адреса текущей микроподпрограммы первого блока памяти соединен с информационным входом счетчика адреса, выход которого соединен с информационным входом второго .дешифратора, управляющий вход которого соединен с выходом второго элемента И,а выход- с адресным входом второго блока памяти, операционный выход которого подключен к выходу устройства, выходы счетчика микрокоманд соединены с входами третьего элемента И, отличающееся тем, что, с целью повышения достоверности функционирования, она дополнительно содержит третий и четвертый блоки памяти, третий и четвертый дешифраторы, второй и третий регистры адреса, триг гер, первый и второй одновибраторы, третий, четвертый и пятый элементы задержки, четвертый и пятый элементы И, элемент ИЛИ, причем информационный вход второго регистра адреса соединен с выходом адреса кода логических условий первого блока памяти, установочный вход - с выходом первого. элемента задержки, а выход - с информационным входом третьего дешифратора, выход которого подключен к адресному входу третьего блока памяти, выход которого соединен с информационным входом регистра логических условий, управляющий вход третьего дешифратора соединен с выходом второго элемента задержки и управляющим входом четвертого дешифратора,.выход которого соединен с адресным входом четвертого блока памяти, выход которого соединен с информационным входом счетчика микрокоманд, информационный вход четвертого дешифратора соединен с выходом третьего регистра, адреса, ,информационный вход которого- соединен с выходом адреса кода числа микрокоманд первого блока памяти, установочный вход третьего регистра адреса соединен с выходом первого элемента задержки, выход второго элемента И через третий элемент задержки соединен со счетными входами счетчика адреса и счетчика микрокод-; манды, выход элемента НЕ. соединен с входами первого и второго одновиб раторов, выход первого одновибратора через четвертый элемент задержки соединен с первым входом четвертого элемента И, выход которого соединен с первый входом элемента ИЛИ, а второй вход - с выходом метки начала микроподпрограммы второго блока памяти, выход метки конца микроподпрограммы которого через пятый элемент задержки соединен с первым входом пятого элемента И, второй вход которого соединен с выходом второго одновибратора, выход пятого элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с единичным входом триггера, нулевойч

выход которого соединен с третьими входами первого и второго элементов И, нулевой вход триггера подключен к вхойу сброса устройства, выходпервого элемента И соединен с входом первого элемента 3| держки.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР Н 19893, кл. R 06 F 9/22, 1972.

2.Авторское свидетельство СССР Н 763898, кл. G 06 F 9/22, 1380 (прототип).

ff

S

H P

1

/9

4

Iff

i

9

n

№

Iff

fU

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

L-j

n

l

S

.Я

2f

//

a

LJ

2Г

I

J

J7

Л

J

Авторы

Даты

1982-12-30—Публикация

1981-07-27—Подача