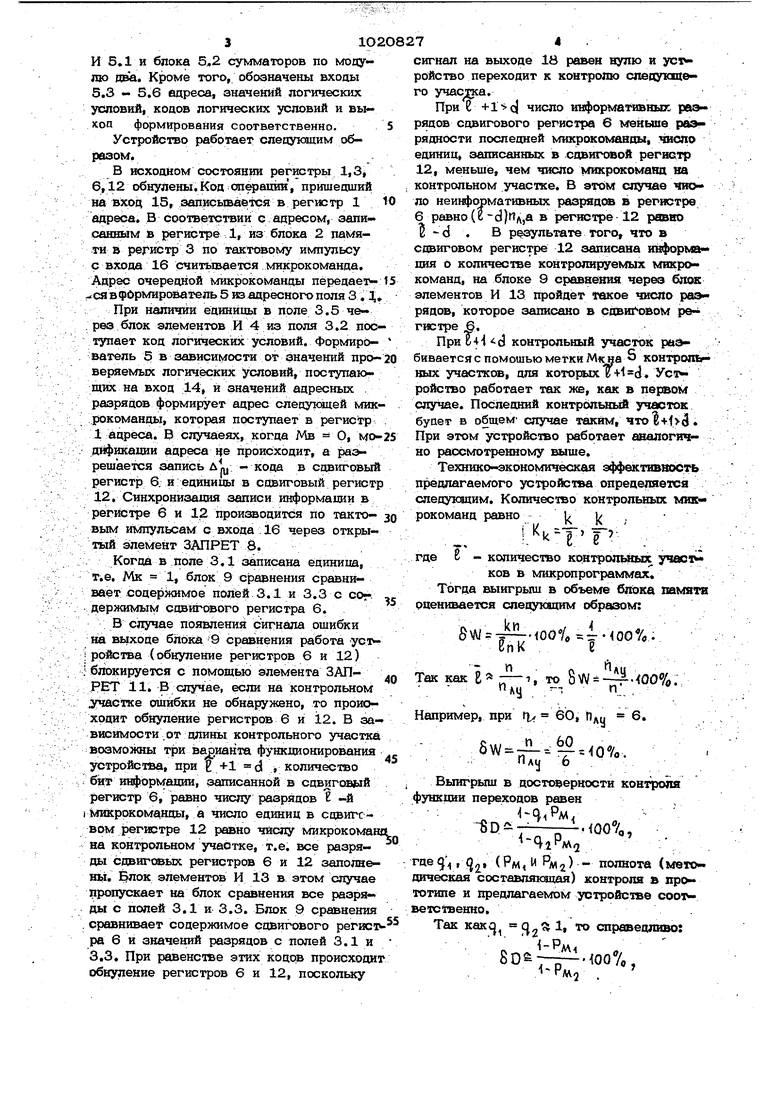

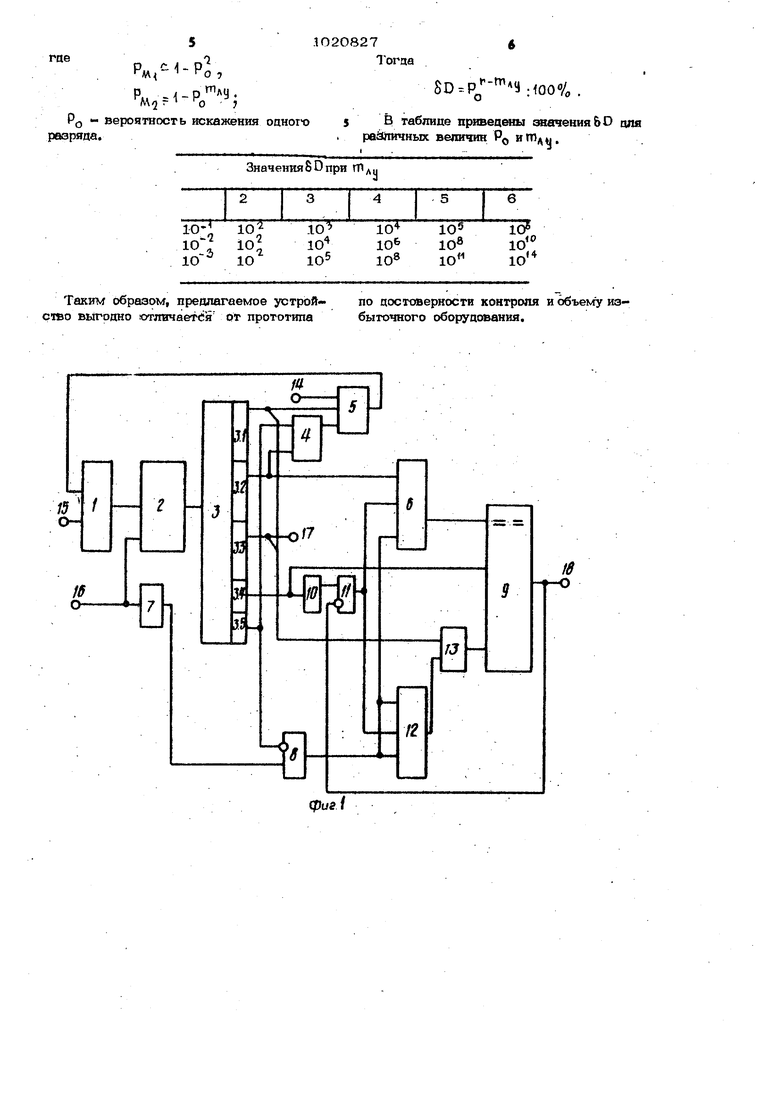

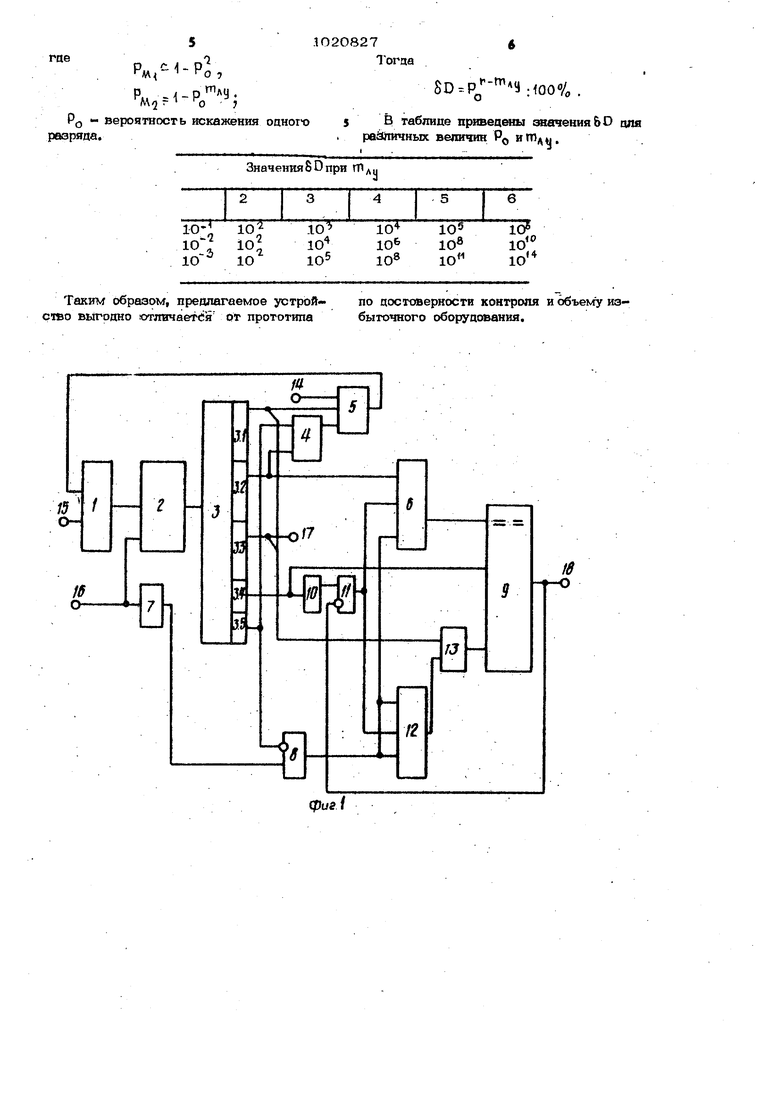

102 Изобретение относится к вычистггепьной технике и может быть использовано при проектировании управляющих устройств ЭВМ и вычислительных систем с микропрограммным управлением. Известно микропрограммное устройство с контролем, содержащее репястр адреса, блок памяти микрокоманд, регистр микрокоманд, сдвигающий регистр, формирователь адреса, схему сравнения, элементы И Недостатком этого устройства является низкая достоверность контроля, обусловленная отсутствием ксяятротя функции выходов.. Известно микропрограммное устройство с контролем, содержащее регистр адреса, блбк памяти микрокоманд, регистр микрокоманд, схему сравнения, элементы И J2 Недостатком устройства также является низкая достоверность контроля, так как осуществляется контроль только субъе Т1ШНЫХ ошибок типа тупик. Наиболее близким к предлагаемгалу по технической сущности является микропрогг . раммное устройство с контролем, содержащее регистр адреса, блок памяти, формирователь адреса, микрокоманд, -(Первый регистрсд ига| схемусравнен)ш C3J Недостатки устройства заключаются в низкой достоверности контротя и бопьщой, избыточности блока памяти. Цель изобретения - повышение досто верности контроля и снижение объема блока памяти. Поставленная цепь достигается тем, что в микропрограммное устройство с кон . тролем, содержащее регистр адреса, блок памяти, регистр микроксж4анд, фqpмиpoвaтель адреса микрокоманд, первый регистр сдвига, блок сравнения, причем первый вход регистра ащ)еса является входом кода операций устройства, второй вход регистра адреса соединен с выходом формирователя адреса микрокоманд,первый вход которого является входом логических условтай устройства, второй вход формирователя адреса микрокоманд соединен с выхсдом адреса микрокоманды регистра микроКоманд, выходы логических условий микроопераций, метки конца контрольного участ ка которого связаны соответственно с Шформацгожным входом первого регистра сдвига, выходом мтофоопераций устройства и первым входом блока сравнения, второй вход которого соединен с выходом первого регистра сдвига, выход блока срав нения является выходом сигнала ошибки устройства, выход регистраадреса соеди7.2. . нен с первым входом блоки памяти, выход которого соединён с входом регистра микрокоманд, введены второй регистр сдвига, Первый и второй элементы задержки, первый и второй элементы ЗАПРЕТА, первый К второй блоки элементов И, причетд тактовый вход устройства через первый элемент задержки подключен к прямому входу первого элемента ЗАПРЕТ, инверсный вход которого соединен с выходом метки ветвления регистра микрокоманд и с первым входом первого блока элементов И, второй вход которого соединец с выходом логических условий регистра микрокоманд, выходы адреса и микроопераций которого под14лючены к первому входу второго блока элементов И, второй вход которого связан с выходом второго регистра сдвига .тактовый и информационный входы которого соединены с тактовым входом первого регистра сдвига,, вход обнулеьтя которого связан с входом обнуления второго регист ра сдвига и выходом второго элемента ЗАПРЕТ, прямой И инверсный входы которого соединены соответственно через второй элемент задержки с выходом метки конца контрольного участка регистра микрокоманд и выходом блока сравнения, выход первого элемента ЗАПРЕТ подключен к тактовому входу второго регистра сдвига, выход второго блока элементов И связан с третьим входом блока сравнения, выход первого блока элементов И связан с третьим входом формирователя адреса микрокоманд. I На фиг. 1 представлена функциональна схема микропрограммного устройств ва; на фиг. 2 - функциональная схема формирователя адресов микрокоманд. Микропрограмкгаое устройство содержит регистр 1 адреса, блок 2 памяти, регистр 3 микрокоманд с полями; адреса 3.1, логических условий 3.2, микроопераций 3,3 метки конца контрольного участка 3.4, метки ветвления 3,5; первый блок элементов И 4, формирователь 5 адреса микрокоманд, первый сдвиговой регистр 6, первый элемент 7 задержки, первый эле м«гг ЗАПРЕТ 8, блок; 9 сравнения, второй элемент 10 задержки, второй элемент ЗАПРЕТ 11, второй сдвиговый регистр 12, второй блок элементов И 13, входы 14 16 логических условий, кода операций и тактовых импульсов устройсгеа cooieei стеенно, выходы 17 и 18 микроопера«ций и сигнала ошибки устройства coot ветственно. Формировагель 5 адреса микрокоманд {фиг. 2) состоит из блока элементов

5.1 и блока 5,2 сумматоров по модую два. Кроме того, обозначены входы 5.3 - 5.6 адреса, значений логических словий, кодов логических условий и выход формирования соответственно.5

Устройство работает следукадим образом.

В исходном состоянии регистры 1,3j 6,12 обнулены. Код операции, пришедший на вход 15, записывается в регистр 1 10 адреса. В соответствии с адресом, записанным в регистре 1, из блока 2 памяти в регистр 3 по тактовому импульсу с входа 16 считьшается микрокоманда. Адрес очередной микрокоманды передает - 15

сявФйрмирователь 5 ю адресного поля З.Д При наличии единицы в поле 3.5 через блок элементов И 4 из поля 3.2 поступает код логических условий. Формирователь 5 в зависимости от значений про-20 веряемых логических условий, поступающих на вход 14, и значений адресных разрядов формирует адрес спёдукяцей микрокоманды, которая поступает в регистр 1 адреса. В случаеях, когда Мв О, N rD-25 дйфикации ааресй це происходит, а разрешается запись AJy - кода в сдвиговый регистр 6. и единицы в сдвиговый регистр 12. Синхронизация записи информации в регистре б и 12 производится по такто- зо вым импульсам с входа 16 через открытый элемент ЗАПРЕТ 6.

Когда в .поле 3.1 залисана единица, Tie. Мк 1, блок 9 сравнения сравнивает .содержимое попей 3.1 и 3.3 с сог держимым сдвигового регистра 6.

В случае появления сшгнала ошибки 1Ш выходе блока 9 сравнения работа уст

ррйства (обнуление регистров 6 и 12)

блокируется с помощью элемента ЗАПРЕТ 11. В случае, если на контрольном частке ошибки не обнаружено, то происходит обнуление регистров 6 и 12. В зависимости от длины контрольного участка возможны TJ3H ва.ианта функционирования устройства, при Е +1 d количество

бтат информации, записанной в сдвиговцй регистр 6, равно числу разрядов Е -и

мшсрокоманды, а число единиц в сдвигеВ6М регистре 12 равно числу микрокомано на контрольном участке, т.е. все разряды сдвиговых регистров 6 и 12 заполнеHbi. $лок элементов И 13 в этом случае пропускает на блок сравнения все разряды с полей 3.1 и 3.3. Блок 9 сравнения

сравнивает содержимое сдвигового регисрра 6 и значений разрядов с полей 3.1 и 3.3. При равенстее этих кодов происходит обнуление регистров 6 и 12, поскольку

сигнал на выходе 18 равен нулю и уст ройство переходит к контролю спедукще- го участеа.

При 2 +1SC) число информатавных раэpsuxoB сдвигового регистра 6 меньше рею рядности последней микрокоманды, число единиц, записанных в .сдвиговой репютр 12, меньше, чем чжато микрокоманд на контрольном участке. В этом случае чню- ло неинформативных разрядов в регистре 6 равно(ь-d)nft,a в регистре 12 равно cJ . В результате того, что в сдвиговом регистре 12 записана ция о количестве контролируемых микрокоманд, на блоке 9 сравнения через бшж элементов И 13 пройдёт 1«кое число раэрядов, которое записешо в сдвиговом ре гвстре 6.

При bfi d контрольный участок разбивается с помощью метки Мкна S контропьг шлх участков, для которых d. Устройство работает так же, как в первом случае. Последний контрольный участок будет в общем случае таким, что1+(3. При этом устройство работает аналогичЕно рассмотренному выше.

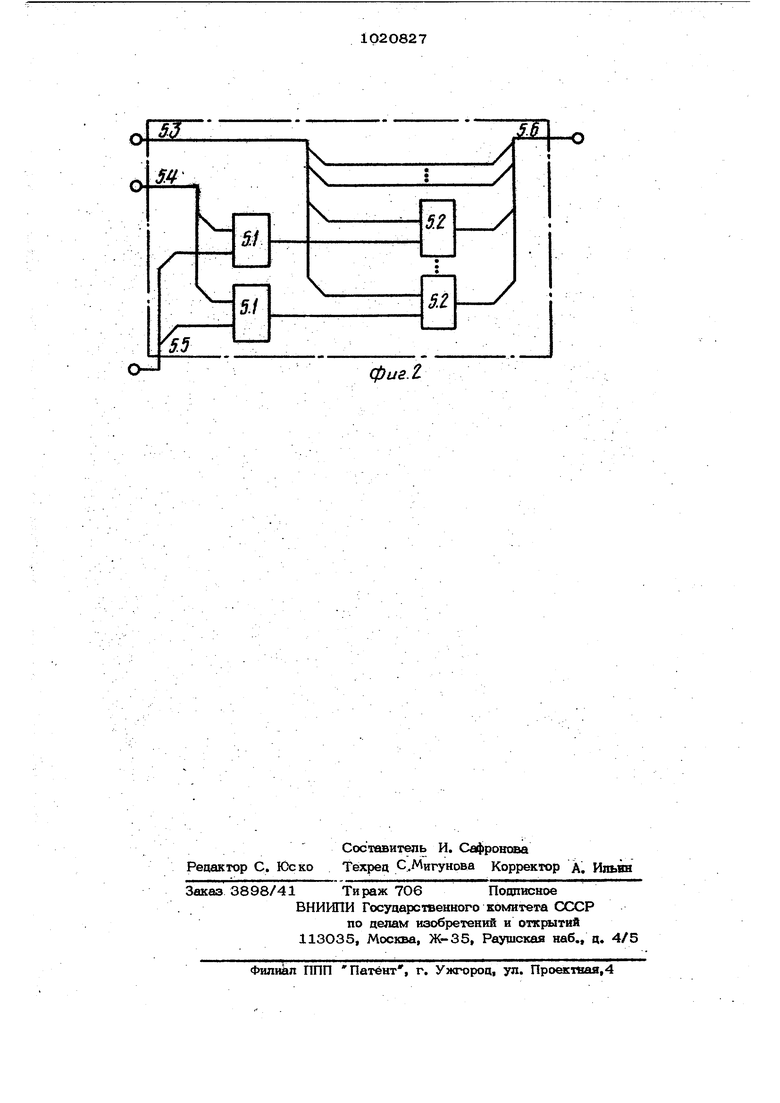

Технико-экономическая эффективвость предлагаемого устройства определяется следующим. Количество контрольных мик- рокоманд равно1/1/

; 1/

ёё

где 8 - количество контрольньк участ

ков в микропрограммах Тогда выигрыш в объеме блока памяти оценивается спедунацим образом:

aw -iooY,.i4oo%; ЕпК .8

11/

как Е то Sw - -400%.

п

п

АУ

6.

Например, при Ч 60, Пд П 60

. OV.

п

AIJ

Выигрыш в достоверности контроля функции переходов равен

bq,PM

тчлг; л

РМ)- полнота (методическая составлякшщя) контроля в лро тотипе и предлагаемом устройстве соот ветственно.

Так как cj li то справедливо:

.

ьр

АЛ2 р с. -1 - р 0 -, Р., . М - 0 J РО5 В вероятность искажения одного разряда.

Значения 8 D при гЯдц раёйто . SD.P таблице приведены значения & О оля ных величин PQ и Шд

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО С КОНТРОЛЕМ, содержаще е регистр адреса, блок памяти, регистр микрокоманд, формирователь адреса мик- рокомйнд, первый регистр сдвига, блок сравнения, причем первый вход регистра адреса является входом кода операций устройства, второй вход регистра адреса соединен с выходом формирователя адреса микрокоманд, первый вход которого является входом логических условий усгройства, второй вход формирователя адреса микрокоманд соединен с выходом адреса микрокоманды регистра микрокоманд, выходы логических условий микроопераций, метки конца контрольного участка которого связаны соответственно с информационным входом первого регистра сдвига, выходом микроопераций устройства и первым входом блока сравнения, второй вход которого соединен с выходом первого регистра сдвига, выход блока сравнения является вььчодом сигнала ошибки устройства, выход регистра адреса coetiH- нек с первым бходом .блока памяти, выход которого соединен с входом регистра, микрокоманд, о т л и ч а ю щ е е с я тем, что, с делью повышения достоверности контроля и снижения объема блока памяти, в него введены второй регистр сдвига, первый и второй элементы задержки, первый и второй элементы ЗАПРЕТ, первый и второй блоки элементов И, причем тактовый вход устройства ч&pea первый элемент задержки подключен к прямому входу первого элемента ЗАПРЕТ, инверсный вход которого соединён с выходом метки ветвления регистра микрокоманд и с первым входом первого блока элементов И, второй вход которого соединен с выходом логических условий ре.гистра микрокоманд, выходы адреса и микроопераций которого подключены к первому входу второго блока здементов И, второй вход которого связан е выходом второго регистра сдвига, тактовый и информационный входы которого соединены с тактовым входом nepBjsro регистра Ю сдвига, вход обнуления которого связан с входом обнуления второго регистра сдвиоо ю .4 га и выходом второго элемента ЗАПРЕТ, п}:ямой и инверсный входы которого соединены соответственно через второй элемевт задержки с выходом метки конца контропЕгного участка регистра микрокоманд и выходом блока сравнения, ВБКОД элемента ЗАПРЕТ подключен к тактовому входу второго регистра сдвига, выход вточ рого блока, эпемеятов И связан с третьшд входсил блока сравнения, выход первого . блока элементов И связан с третьим входом формирователя адреса микрокоманд.

Таким образом, преолагаемое устройстео выгодно отличается от прототипа

по достоверности контроля и объему избыточного оборудования.

OJ

0ue.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свицетельство СССР по заявке № 3286938/24, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-17—Подача