прямым входом третьего элементов И, второй прямой вход и выход третьего элемента И соединены соответственно

с вторым входом блока управления и вторым входом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 1991 |

|

RU2007024C1 |

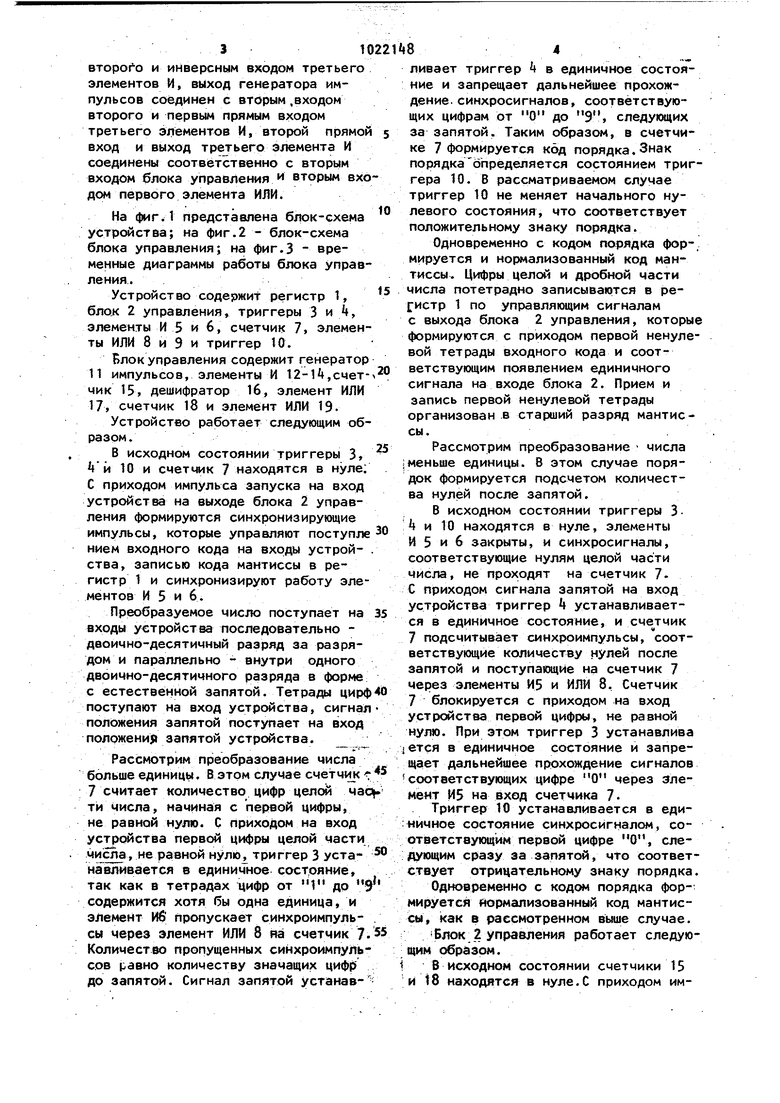

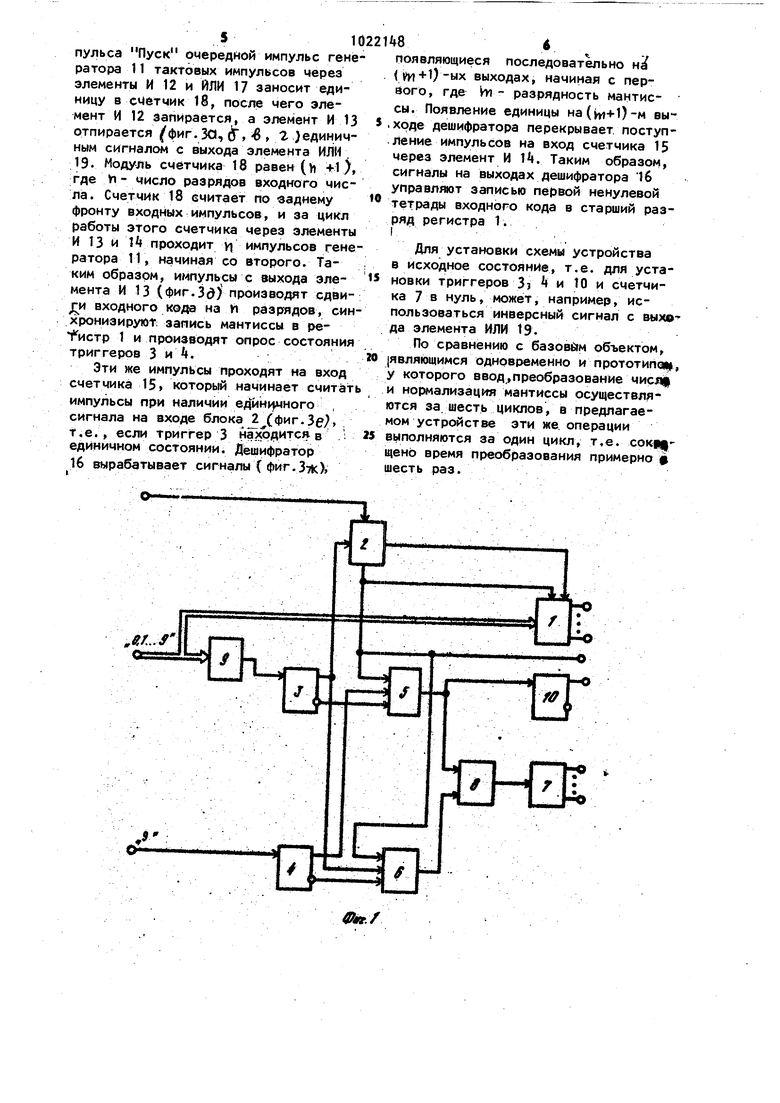

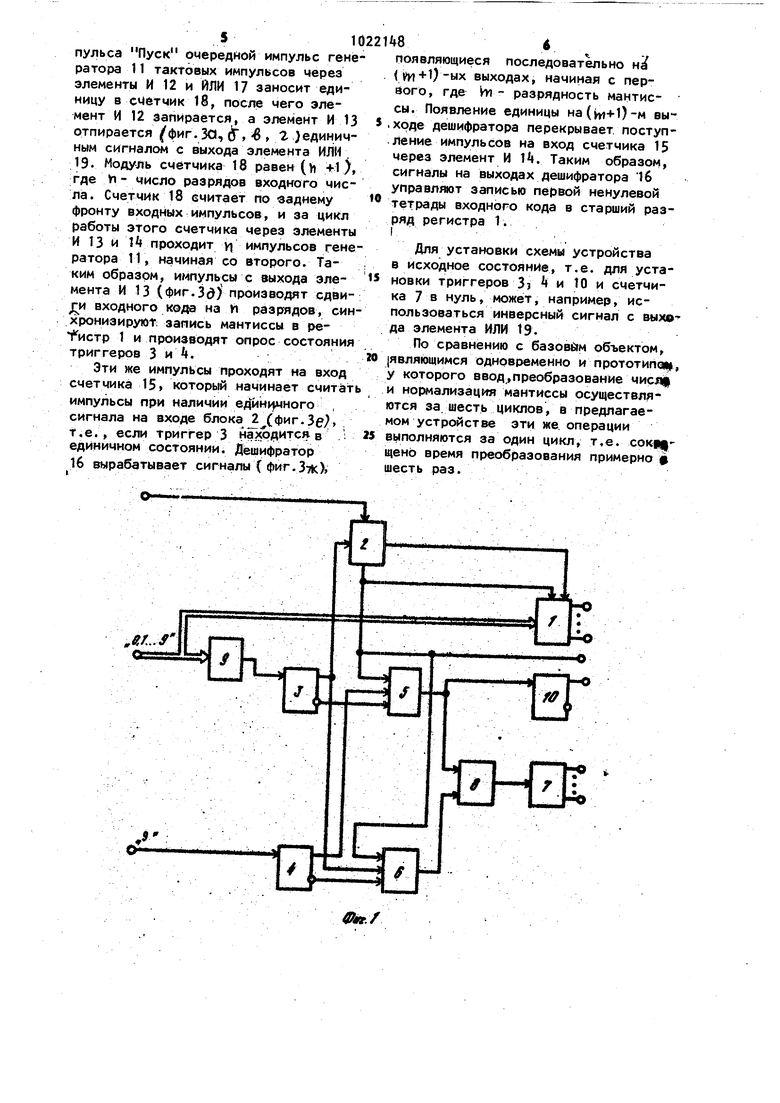

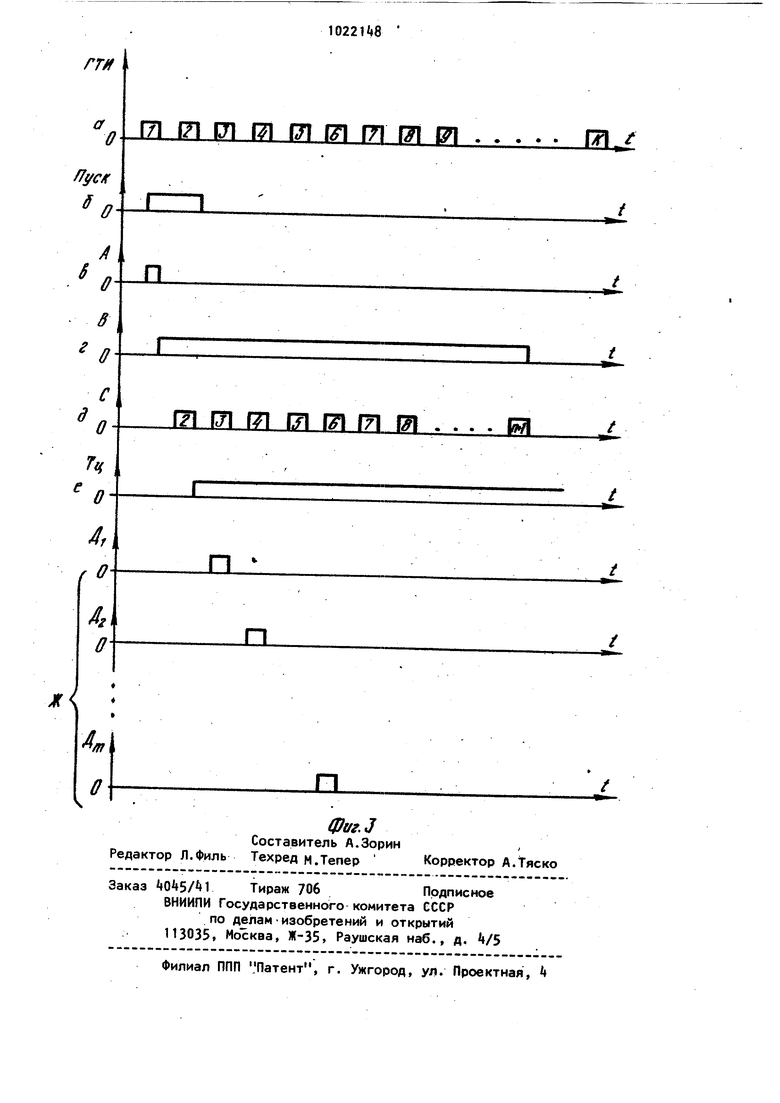

. 1 ; : , : ,. , Изобретение относится к вычислительной технике и может быть использовано для формирования кода с плавающей запятой в процессе ввода в электронное вычислительное устрой ство информации в форме с фиксированной запятой. Известно устройство для преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой в электронных вычислительных машинах, которое реализова,но , на типовых электронных узлах: регистре хранения, регистре сдвига, сумматоре и устройстве . управления. Преобразование чисел производится алгоритмом, реализованном на уровне стандартных команд или микрокоманд машины Г 3 Недостатком данного устройства является низкое быстродействие. Наиболее близким к предлагаемому по технической сущности является. устройство, содержащее два регистра сдвига с последовательностями цифр и символов, два регистра сдвига,связанных с сумматорами, два триггера, группу элементов И, элемент И-НЕ и устройство управления СЯ. К недостаткам известного устройст ва относятся сложный алгоритм и низкое быстродействие.; Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство для преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой, содержащее блок управления регистр, счетчик, два триггера и два элемента И, первые входы которых сое динены с инверсными выходами соответ ствующих триггеров, первый выход« бл ка управлен)ля соёдийён с входом сдви га рег истра, выход которого сое- динен с выходом мантиссы.устройства,выход порядка к тйрого соединен с выходом счетчика, дополнительно Введены два элемента ИЛИ и третий Триггер, выход которого соединен с выходом знака порядка устройства, вход числа которого соединен с ин.формационным входом регистра и через первый элемент ИЛИ с входом первого триггера прямой выход которого соединен с первым входом блока управления и вторым входом второго элемента И, третий- вход которого соединен с первым выходом блока управления и вторым входом первого элемента И, третий вход которого соединен с прямым выходом второго триггера, вход которого соединен с входом положения запятой устройства, вход запуска которого соединен с вторым входом блока управления, второй выход которого подключен к входу записи регистра,выход первого элемента И соединен с входом третьего триггера и первым входом второго элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом счетчика. Причем блок управления содержит генератор импульсов, три элемента И, два элемента ИЛИ, два счетчика и дешифратор, первый выход которого соединен с вторым выходом блока управления, первый выход которого сое- динен с управляющими входами первого счетчика и дешифратора, информационные входы которых соединены соответственно с выходом первого элемента И и выходом счетчика, второй выход дешифратора соединен с инверсным входом первого элемента И, прямой вход которого соединен с выходом второго элемента И первым выходом блока управления и первым входом первого элемента ИЛИ, выход которого через второй счетчик соединен с входами второго элeмeнta ИЛИ, выход которого соединен с первым входом BTOpofo и инверсным входом третьего элементов И, выход генератора импульсов соединен с вторым .входом второго и первым прямым входом третьего э тементов И, второй прямой вход и выход третьего элемента И соединены соответственно с вторым входом блока управления и вторым вхо дом первого элемента ИЛИ. На фигЛ представлена блок-схема устройства; на фиг.2 - блок-схема блока управления; на фиг.З - временные диаграммы работы блока управления. Устройство содержит регистр 1, блок 2 управления, триггеры 3 и 4, элементы И 5 и 6, счетчик 7, элементы ИЛИ 8 и 9 и триггер 10. Блок управления содержит генератор 11 импульсов, элементы И l2-1,c4eTчик 15, дешифратор 16, элемент ИЛИ 17, счетчик 18 и элемент ИЛИ 19. Устройство работает следующим образом. В исходном состоянии триггеры 3, й 10 и счет1«1к 7 находятся в нуле; С приходом импульса запуска на вход устройства на выходе блока 2 управления формируются синхронизирующие импульсы, которые управляют поступле нием входного кода на входы устройства, записью кода мантиссы в регистр 1 и синхронизируют работу элементов И 5 и 6. Преобразуемое число поступает на входы устройства последовательно двоично-десятичный разряд за разрядом и параллельно - внутри одного двоично-десятичного разряда в форме с естественной запятой. Тетрады цирф поступают на вход устройства, сигнал положения запятой поступает на вход положения запятой устройства. Рассмотрим преобразование числа больше единицы. В этом случае счетчик 7 считает количество цифр целЫ Mao ти Числа, начиная с первой цифры, не равной нулю. С приходом на вход устройства первой цифры целой части числа, не равной нулю триггер 3 устанавливается в единичное состояние, так как в тетрадах цифр от 1 до Э содержится хотя бы одна единица, и элемент Иб пропускает синхроимпульсы через элемент ИЛИ 8 на счетчик 7 Количество пропущенных синхроимпульсов равно количеству значащих циф|;: до запятой. Сигнал запятой устанавливает триггер в единичное состояние и запрещает дальнейшее прохождение, синхросигналов, соответствующих цифрам от О до 9, следующих за запятой. Таким образе, в счетчике 7 формируется код порядка.Знак порядкаопределяется состоянием три1- гера 10. В рассматриваемом случае триггер 10 не меняет начального нулевого состояния, что соответствует положительному знаку порядка. Одновременно с кодом порядка формируется и нормализованный код мантиссы. Цифры целсЛ и дробной части числа потетрадно записываются в 1 по управляющим сигналам с выхода блока 2 управления, которые формируются с приходом первой ненулевой тетрады входного кода и соответствующим появлением единичного сигнала на входе блока 2. Прием и запись первой ненулевой тетрады организован в старший разряд мантиссы.. Рассмотрим преобразование числа меньше единицы. В этом случае порядок формируется подсчетом количества нулей после запятой. В исходном состоянии триггеры 3 j и 10 находятся в нуле, элементы И 5 и 6 закрыты, и синхросигналы, соответствующие нулям целой части числа, не проходят на счетчик 7. С приходом сигнала запятой на вход устройства триггер k устанавливается в единичное состояние, и счетчик 7 подсчитывает синхроимпульсы, соответствующие количеству нулей после запятой и поступающие на сметчик 7 через элементы И5 и ИЛИ 8. Счетчик 7 блокируется с приходом на вход устройства первой цифры, не равной нулю. При этом триггер 3 устанавлива ется в единичное состояние и запрещает дальнейшее прохождение сигналов соответствующих цифре О через злеме«т И5 на вход счетчика 7 Триггер 10 устанавливается в еди«ичное состояние синхросигналом, соответствующим первой цифре О, следующим сразу за запятой, что соответствует отрицательному знаку порядка. Одновременно с кодом порядка фор-мируется йормапизованный код мантиссы, как в рассмотренном вьние случае. i Блок 2 управления работает следующим образом. В исходном состоянии счетчики 15 и 18 находятся в нуле.С приходом импульса Пуск очередной импульс генератора t1 тактовых импульсов через элементы И 12 и ИЛИ 17 заносит единицу в сметчик 18, после чего элемент И 12 запирается, а элемент И 13 отпирается фиг. ЗО, О , -б , 2 Jединичным сигналом с выхода элемента ИЛИ 19. Модуль счетчика 18 равен (), где VI - число разрядов входного числа. Счетчик 18 считает по заднему фронту входных импульсов, и за цикл работы этого счетчика через элементы И 13 и И проходит У) импульсов генератора 11, начиная со второго. ТаКИМ образом, импульсы с выхода элемента И 13 (Фиг.3d) производят сдаи ;; и входного кода на И разрядов, синхронизируют; запись мантиссы в 1 и производят опрос состояния триггеров 3 и Л. Эти же импульсы проходят на вход счетчика 15 который начинает считат импульсы при наличии е4йн нного , сигнала на входе блока (фиг.Зе| ; т.е., если триггер 3 находится в ; единичном состоянии. Д|ешифратор 16 вырабатывает сигналы (фиг,Зж).

Sf...r

Q,V

ТД

о 10

Ш

fff 8 появляющиеся последовательно н Уи+1)ых выходах, начиная с первого, где Hi - разрядность мантиссы. Появление единицы на(ы+1)м выходе дешифратора перекрывает, поступление импульсов на вход счетчика 15 через элемент И . Таким образом, сигналы на выходах дешифратора 16 управляют записью первой ненулевой тетрады входного кода в старший разряд регистра 1. Для установки схемы устройства в исходное состояние, т.е. для установки триггеров 3 и to и счетчика 7 в нуль, может, например, использоваться инверсный сигнал с выхвда элемента ИЛИ 19. По сравнению с базовйм объектом, |являющимся одновременно и прототипа, у которого ввод,преобразование мися и нормализация мантиссы осуществляются за шесть циклов, в предлагаемом устройстве эти же операции выполняются за один цикл, т.е. сок1|| щено время преобразования примерно р шесть раз.

стг

в

L- i-OJ

M

77

f$

2

/

-o --

г /

fff

//

т т/

ж

т

fff

4f.Z -

/7Г

Фг№,г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электронная вычислительная машина Электроника-бО | |||

| Эксилуатационная документация | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1983-06-07—Публикация

1982-03-10—Подача