дулю два второй групш# (,.. . J l,. I .),R- и S-входы каждого триггера приемного регистра соединены

соответственно с нулевым и единичным выходами соответствующего ему триггера передающего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля принимаемой информации | 1984 |

|

SU1242960A1 |

| Устройство для контроля принимаемой информации | 1991 |

|

SU1820384A1 |

| Устройство для контроля принимаемой информации | 1977 |

|

SU739538A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Устройство для обнаружения ошибок при передаче кодов | 1983 |

|

SU1091211A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU960823A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Устройство для контроля передачи информации | 1987 |

|

SU1525702A1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| Постоянное запоминающее устройство | 1983 |

|

SU1151573A1 |

1. УСТРОЙСТВОДЛЯ КОНТРОЛЯ ПРИНИМАЕМОЙ ИНФОРМАЦИИ, содержащее п-байтный передающий регистр,п-байтный приемный регистр, 2п блоков свертки по модулю два, 2т дополнительных блоков свертки по модулю два, блок сравнения содержащий дв е группы сумматоро в по модулю два и элемент ИЛИ, прн1чем выхода п-.байтного. передающего регистра соединевдз с соответствующими входами п-байтного приемного регистра, выходы й байтного приемного регистра соединены с соответствующими входами п блоков свертки по модулю два первой групщд, выходы которых связаны с первыми входгьми соответствующих п сумматоров по могдулю два перЁой группы, выходы п-байтного передающего регистра подключены к соответствующим входам п блоков свертки по модулю два рой группы, выходы которых соединен с вторыми входами соответствующих п сумматоров по модулю два первой груйпы, выходы i-ro разряда всех байтов передающего регистра связаны с входами соответствующих m дополнительных блоков свертки по модулю два первой группы, выходы которых соединены с первыми входами соответствующих m сумматоров по модулю два второй группы, выходы j-го сазряда . всех байтов приет«1ного регистра соединены с входами соответствующих m дополнительных блоков свертки по два второй группы, выходы котрЕилх связаны с вторыми входами соответствующих го сумматоров по модулю два второй группы, выходы сумматоров по модулю два первой и второй групп подключены к соответствующим группам входов элемента ИЛИ, выход которого является выходом сигнала обнаружения ошибки, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет коррекции однократных Ошибок, блок сравнения ,сх дерэсит первый и второй элементы g ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент Не динамическим выходом, причем выходы п Л сумматоров по модулю два первой груп j пы соединены с соответствующими входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы ю сумматоров по модулю.. В два второй группы связаны с соот- ; ветствующими входгми второго элемента ИСКЛЮЧАКВДЕЕ ИЛИ, выходы пер- J вого и второго элементов ИСЮЮЧАКВДЕЕ пояклюЧены к соотве1 х;т1вуйвшм входам элемента И с динамическим KJiходом,выход которого является выходом разрешения коррекции блока сравнения. 2. Устройство по п. 1, о.-т л ич а ю щ е е с я тем, что каждый байт приемногчэ регистра содержит m RSTтриггёров (где т - число разрядов :в байте) и m элементов и, причем ;выходы элементов И подключены к тактовым и синхронизирующим входам соответствующих триггеров, первые вход|а Всех элементов, и подключены к шине разрешения коррекции блока сравнения, входы всех элементов И Ооединенк.с выходом i-ro сумматора по модулю два первой группы, третьи входы всех элетлентов И связаны с выходомj -го сумматора по мо

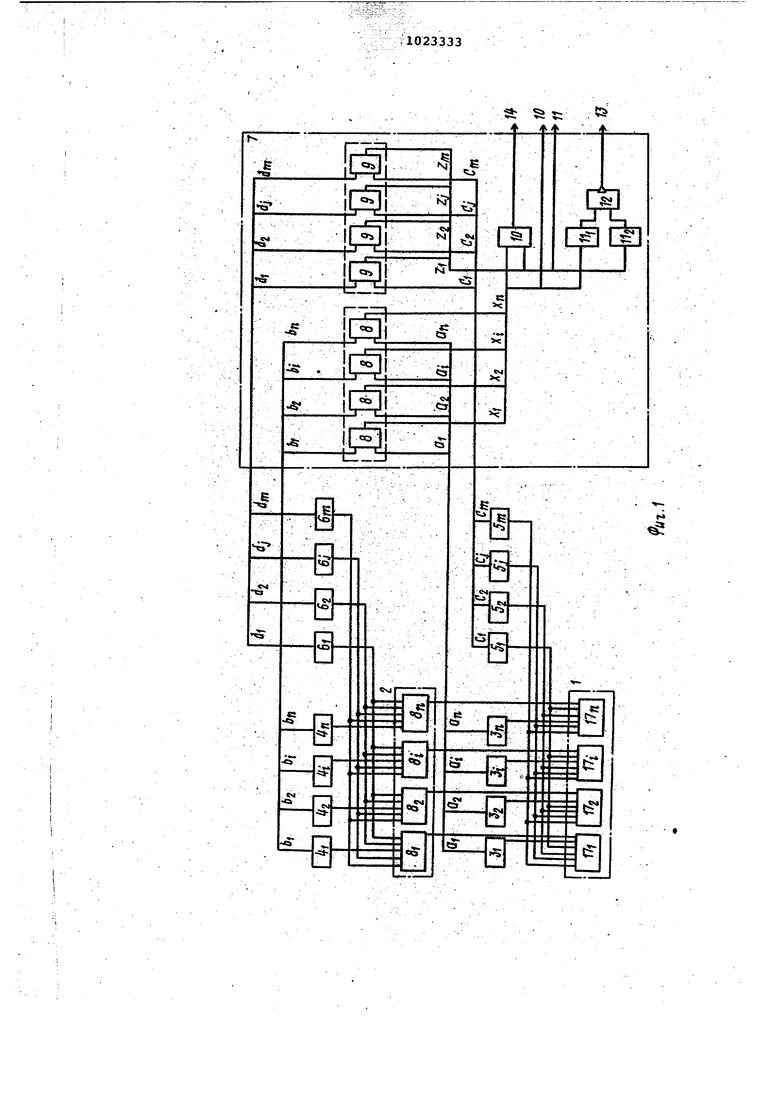

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля при нимаемой.информации в электронновычислительных, машинах. Известно устройство для контроля передачи информации в-.универсальных вычислительных машинах Единой сист мы (ЕС ЭВМ), содержащее 2п блоков свертки по модулю два, выходы которых соединены с блоком сравнения выход которого является выходом, устройстваfij. Недостатками данного устройства являются отсутствие возможности кор рекции однократных ошибок и обнаруж ния ошибок кратности 2 в байте. Известно устройство, для обнару жения и локализации одиночных ошибо при передаче цифровой информации. Содержащее приемный регистр информации, подключенный линией связи к передающему регистру, выходы кото рого соединены с входами-первой cxeNttxi кодирования, к выходам которой через линию связи подключены вх ды приемного регистра контрольных разрядов, и регистр ошибки, выходы которого через дешифратор слова ошибки соединены с входами приемного регистра инфбрМации, схему сравнения, включенную между прие ным регистром контрольных разрядов И регистром ошибки,, и вторую схему кодирования, включенную между приемным регистром информации и схе мой уравнения 2 . : Недостатками устройства являются большой объем оборудования и отсутствие возможности исправления однократных ошибок. Наиболее близким к изобретению является устройство для контроля п ин1№1аемой информации, содержащее п-байтный передающий регистр, п байтнвгй приемный регистр, 2п блоков свертки по модулю два, 2т дополнительных блоков свертки по модулю два, выходы « -байтного передаю щегр регистра соединены с соответствуюиими входами п-байтного приемного регистра, выходы п-байтного приемного регистра соединены с соо ветствуюйшми входами первых п блоков свертки по модулю два, выходы п-байтного передающего регистра со динены с, соответствующими входами остальных п блоков свертки по модулю два, выходы j-ro разря 1а всех байтов передающего регистра соединены с входами J-ro из первых т дополнительных блоков свертки по модулю два, выходы j-ro разряда всех байтов приемнсэго регистра соединены с входами j-ro из остальных m дополнительных блоков свертки по . дулю два, выходы всех блоков свертки по модулю два соединены с входами блока сравнения, выход которого является выходом устройства « Однако известное устройство характеризуется невозможностью коррекции однократных ошибок. | . ( . - Целью изобретения является расширение функциональных возможностей за счет коррекции однократных ошибок. Поставленная цель достигается тем, что в устройстве для контроля принимаемой информации, содержащем п-байтный передающий регистр,п-байтный приемный регистр, 2п блоков, свертки по модулю два, 2т дополнительных блоков свертки по.модулю два, блок сравнения, содержащий две группы сумматоров по модулю два и элемент ИЛИ, причем выходы п-байтного передающего регистра соединены с соответствующими входами п-байтного приемного регистра, выходы п-байтного приемного регистра соединены с соответствующими входами п блоков свертки по модулю два первой группы, выходы которых связаны,с первыми входами соответствующих п сумматоров по модулю два первой группы, выхода п-байтного передающего регистра подключены к соответствующим входам П-блоков сйертки по модулю два -второй группы, выходы которых соединены со вторыми входами,соответствующих п-Сумматоровпо модулю два первой группы,выходы 1-го разряда всех байтов передающего регистра связаны с входами соответствующих m дополнительных блоков свертки по модулю два первой группы, выходы которых соединены с первыми входалш соответствующих .т сумматоров по модулю два , второй группы, выходы j-ro разряда jBcex байтов приемного регистра соединены с входами соответствующих m дополнительных блоков свертки по модулю два второй группы, выходы которых связаны с вторыми входами соответствующих m сумматоров по модулю два второй группы, выходы сумматоро по модулю два первой и второй групп подключены к соответствующим группам входов элемента ИЛИ, выход которого является выходом сигнала обнаружения ошибки, блок сравнения со держит первый и второй элементы ИСЮШЧЛрЦЕЕ ИЛИ и элемент И с динам ческим выходом, причем выходы п сумматоров по модулю два первой гру пы соединены, с соответствующими вхо дами первого гэдемента ИСКЛЮЧАЮЩЕЕ ИЛИ/ выходы га сумматоров по модулю .два второй группы связаны с соот-. ветствующими входами второго элеме ,та. ИСКЛЮЧАЮЩЕЕ ИЛИ, ВЫХОД первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к соответствующим входам элемента И с динамическим выхо дом, выход которого является выходом разрешения коррекции блока срав нения.. . - : ,-..- Кроме того, каждый байт приемного регистра содержит mRST-триггеIров ..(где га - число разрядов в. бай- )те) и га элементов И, причем выходы эл.ементов И подключены к тактовы и синхронизирующим входам соответствующих триггеров, первые входы вс элементов И подключены к шине разрешения коррекции блока сравнения, вторые входы всех элементов И роединены с выходом 1-го сумматора по модулю два первой группы, третьи входы йсех элементов И связаны с выходом J-ro сумматора по модулю два второй группы (.,« i п ,.. . R- и S-входы каждого триггера приемного регистра соединены соот, ветственно с нулевым и единичным выходами соответствующего ему триггера передающего регистра. На фиг. 1 приведена структурная схема устройства для контроля прини маемой информации; на фиг. 2 - структурная схема Г-го байта приемного регистра; на фиг, 3 - временная диаграмма работы устройства. Устройство для контроля принимае мой информации содержит п-байтный передакнцйй регистр 1, п-байтный при ный регистр. 2, 211 блоков свертки по модулю два - и , ,2in дополнительных блоков свертки по мо рулю два 5 -5„ и 6 6, блок 7 сравнения. Выходы п-байтного передеиощего регистра 1 соединены с соот ветствуюиими входами п-байтного пр емного регистра 2, выходып-байтног приемного регистра 2 соединены с соответствующими входами первых п блоков свертки по модулю два , выходам п-байтного передающего ре- гистра 1 соединены с соответствуюшими входами остальных п блоков свертки по модулю два 3, -3,выходы J-ro разряда вСех байтов передающего регистра 1 соединены с входами j-го из первы х m дополнительных блоков свертки по модули два ,„, выходы ij-го разряда всех байтов приемного регистра 2 соединены с входами j-ro из остальных м дополнительных блоков свертки бjj-6j. Блок 7 сравнения содержит две группы п и m сумматоров 8 и9 по модулю два, элемент ИЛИ 10, первый второй Hi элементы ИСКЛЮЧАКЯЦЕЕ ИЛИ, элемент И 12 с прямым динамическим выходом, выход ±-го блока свертки по модулю два первой группы из п блоков свертки по модулю два соединен с первым входом i-ro сумматора 8 по модулю два первой группы из п сумматоров по модулю два,, второй вход которого соединен с выходом i-ro блока свертки по модулю два второй группы из п блоков свертки по модулю два (, .12,...,п), выход j-ro блока свертки :по модулю два второй группы m до,полнительных , блоков свертки ,по модулю два соединен с первым . входом -го сумматора 9 по модулю два из ,второй ГР5П1ПЫ m сумматоров шо модулю I два, второй вход йоторого соединен с выходом j-го блока свертки по модулю два .первой группы, из m дополнительных блоков ( свертки по модулю два (j 1,2,.. ,in) , выходы п cyivwa торов 8 по модулю два первой труппы соединены с первой группой входов элементов ИЛИ 10 и входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ i 1 , выхода суммуторов 9 по модулю два соединены со второй группой элемента ИЛИ 10 и входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ , выходы первого 11 и второго 112 эле- ментов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входами элемента И 12 с прямым дийамическим выходом, выход 13 которого является шиной сигнала разрешения коррекции, выход 14 элемента ИЛИ ГО является выходом устройства. i - - , - Приемный регистр 2 выполнен на RST-триггерах 15 и содержит в каждом разряде дополнительный элемент И 16, ; причем счетный вход и вход синхрониэации каждого триггера регистра 2 соединены с выходом соответствующего дополнительного элемента И 16, первый вход всех дополнительных элементов И 16 соединен с шиной разрешения коррекции 13, выход сумматора 8 по модулю два первой группы и э п сум- маторов по модулю два блока 7 сравнения соединен с вторым входом всех д6полнительных элементов И 16 байта 17;,- приемного регистра 2, выход j-ro сумматора 9 по модулю два второй группы из m сумматоров по модулю два блока 7 сравнения соединен с третьим входом дополнительного элемента И 16 j-го разряда каждого байта приемного регистра 2 (,2,. n;j -If 2f. . /щ) , Устройство работает следующим о.б разом. Информация из п-байтного передающего регистра 1 передается в п-бай ный приемный регистр 2, С целью I контроля передачи информации содержимое каждого байта ITj передающего регистра 1 сворачивается в соответствующем блоке свертки по модулю два, который формирует значение контрольного разряда . После приема информации в регистр 2 содержимое каждого его байта 17 сворачивается в соответствующем блоке свер ки 4 по модулю два, который формирует значение контрольного разряда b|(,2,...,n). Кроме того, одноименные j-е разряды всех байтов передающего регист ра 1 сворачиваются блоком свертки 5j по модулю два, формирующем зна-. чение контрольного разряда с; , а одноименные j-e разряды всех п байтов приемного регистра 2 сворачиваются блоком свертки б; по модулю дв формирующем-значение контрольного разряда d { jj 1, 2 ,. . .т). Сформированные значения контроль ныя разрядов а Ь,- поступают на входы i-ro сумматора 8 rio модулю два первой группы из п сумматоров по мо дулю два, а значения Cjdj - на вход j-ro сумматора 9 по модулю два вто рой группы из га сумматоров по модул два блока 7 Сравнения. В блоке 7 сравнения с помощью сумматоров по . модулю два производится попарное сравнение значений контрольных разрядов Ь,-,с и dj и формируются значения сигналов , 7; по формулам х,ау® Ь, d , где @- символ операции сложения по ,, модулю два. от з Фствии ошибок передачи информации значения контрольных разрядов попарно совпадают,значения сигналов ,2t f)K Zj( J 1,2,... ,in) равны нулю, и на выходе 14 элемента ИЛИ 10 сигнал ошибки отсутствует. Если при передачи информации возникла ошибка четной кратности или любой нечетной кратности, то значения одной или. нескольких пар контрольных разрядов не совпадают, на выходе одного или нескольких сумматоров по. модулю два формируются единичные сигналы и на выходе 14 элемента ИЛИ 10, как и в прототипе,, выра батывается сигнал обнаружения ошибки. Если же -Ъознимдая ошибка - однократная, то, того, такая ошибка автоматически корректируется, Действительно, пусть,например, возникла ошибка в фиксированном J-M разряде-i-ro байта. Тогда значения, контрольных разрядов и Ъ ,с и djj попарно не совпадают, на выходе i-ro из первых п сумматоров 8 по модулю два формируе.тся сигнал х.- J, на выходе j-го из остальных m сумматоров 9 по модулю два формируется сигнал Zj.- Значения выходных сигналов остальных сумматоров по модулю два равны нулю. ПРИ этом на выходах первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ вырабатывается единичный сигнал. Элемент И 12 представляет собой обычный элемент И, к выходу которого подключена дифференцирующая цепь. Поэтому на динамическом выходе элемента И 12 (на выходе дифференцирующей цепи) фррмируется импульсный сигнал разрешения коррекции, который поступает на первый вход всех дополнительных элементов И 16 приемного регистра 2. Одг(новременно единичный / сигнал х поступает на второй вход всех дополнительных элементов И 16 байта 17 приемного регистра 2, а единичный сигнал.)- на третий дополнительного элемента И 16 j-го разряда каждого байта приемного регистра 2. в результате на всех трех входах дополнительного элементе И 16 j-го разряда i-ro байта действуют единичные сигналы. Поэтому на его выходе формируется единичный импульсный сигнал, именяющий состояние триггера j-го разряда i-ro байта приемного регистра 2 на про- тивоположное. Таким образом, осущест- вляется коррекция всех однократных . ошибок, возникающих при передаче информации из передающего регистра 1 в приемный регистр 2. Ш1Ибки кратности 2 и более не корректируются, так как при этом на выходе хотя бы одного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ формируется рулевой сигнал/ и сигнал разрешения коррекции ие вырабатывается.

5

Регистр

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборное колесо | 1921 |

|

SU370A1 |

| Под ред | |||

| Л.М.Райкова | |||

| М., Мир, 1975, С.331 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля принимаемой информации | 1977 |

|

SU739538A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-15—Публикация

1981-10-16—Подача