Изобретение относится к цифровой вычислительной технике и может быть использовано для обнаружения и коррекции ошибок в трактах пересылки информации электронно-вычислительных машин.

Цель изобретения - повышение достоверности контроля принимаемой информации.

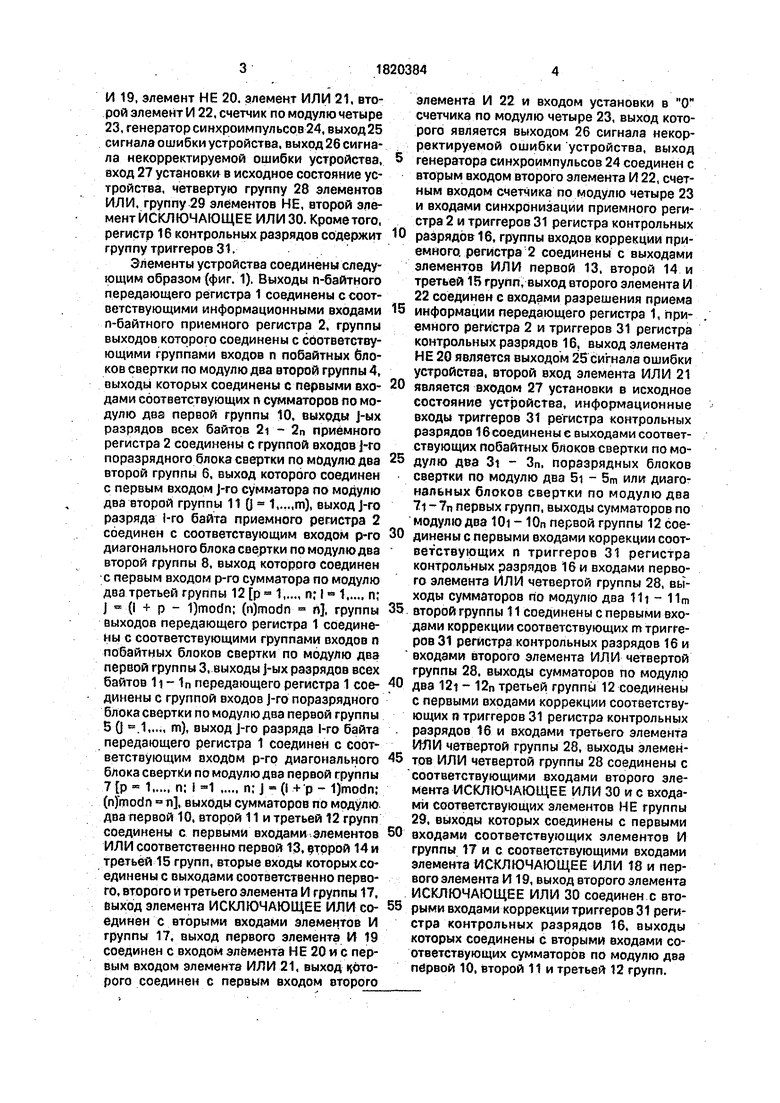

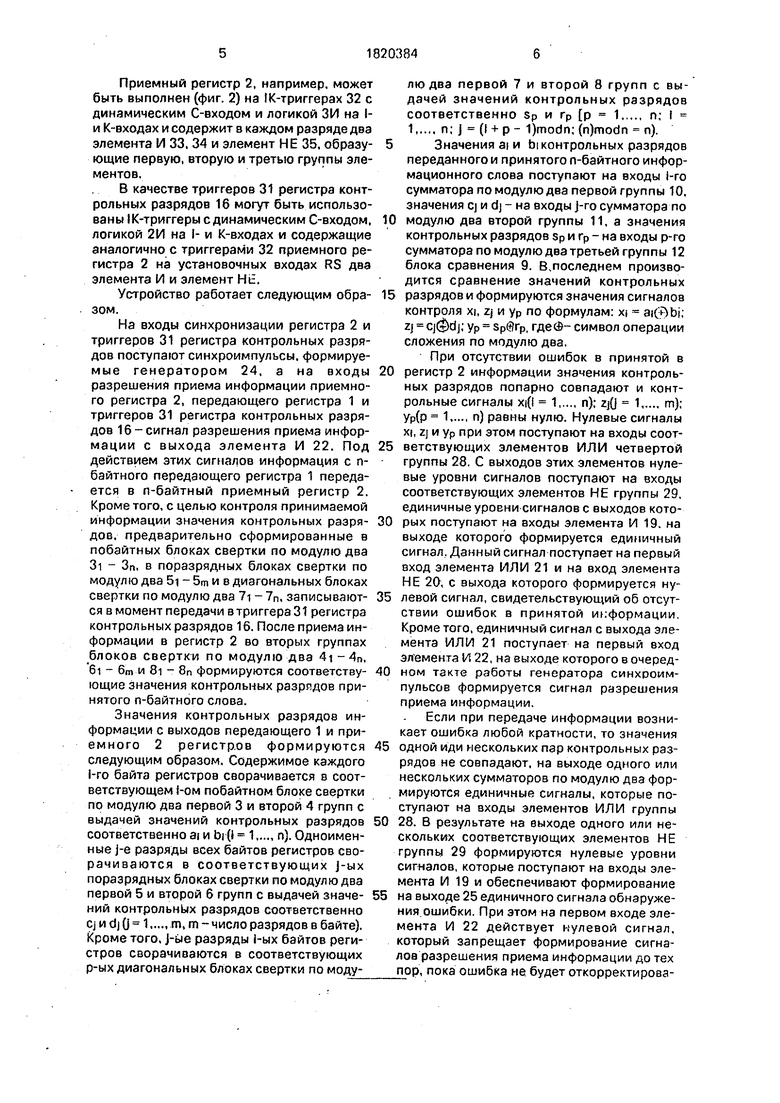

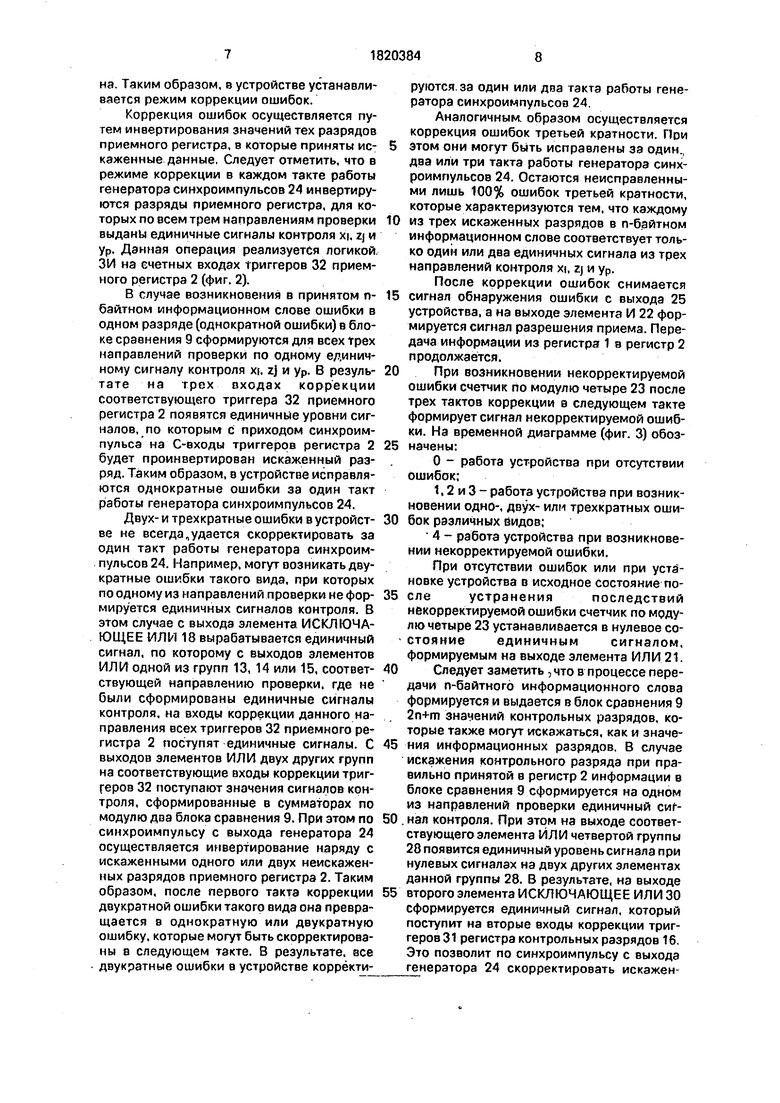

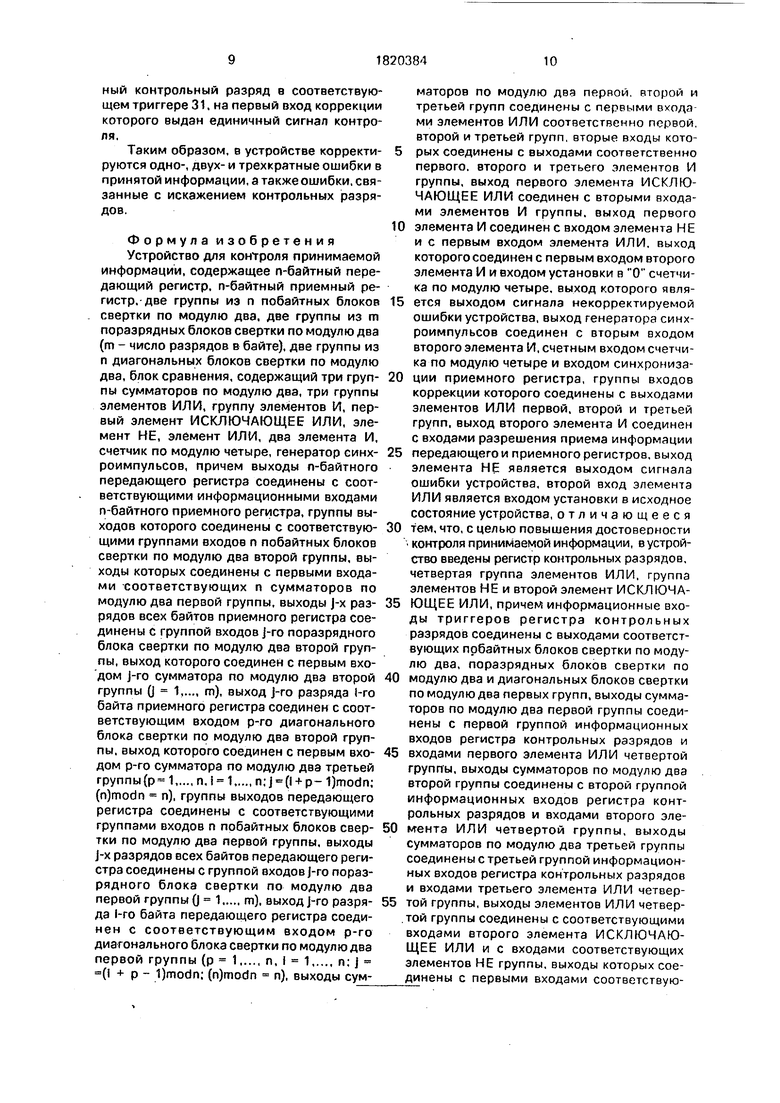

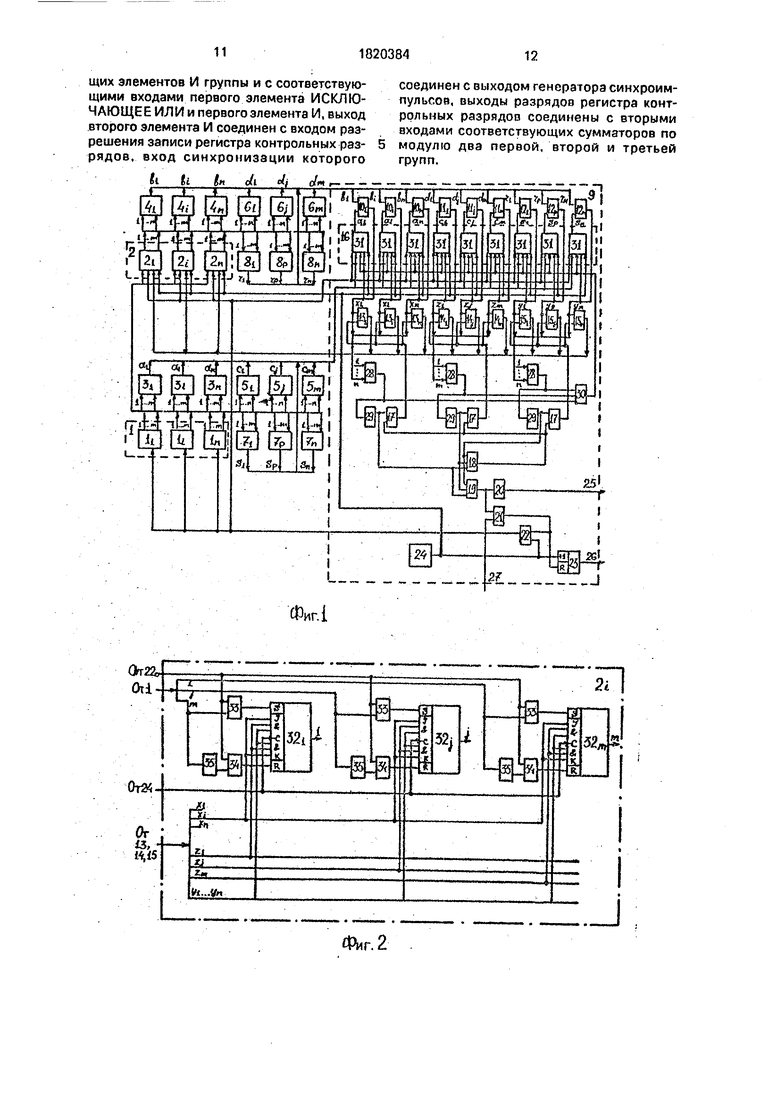

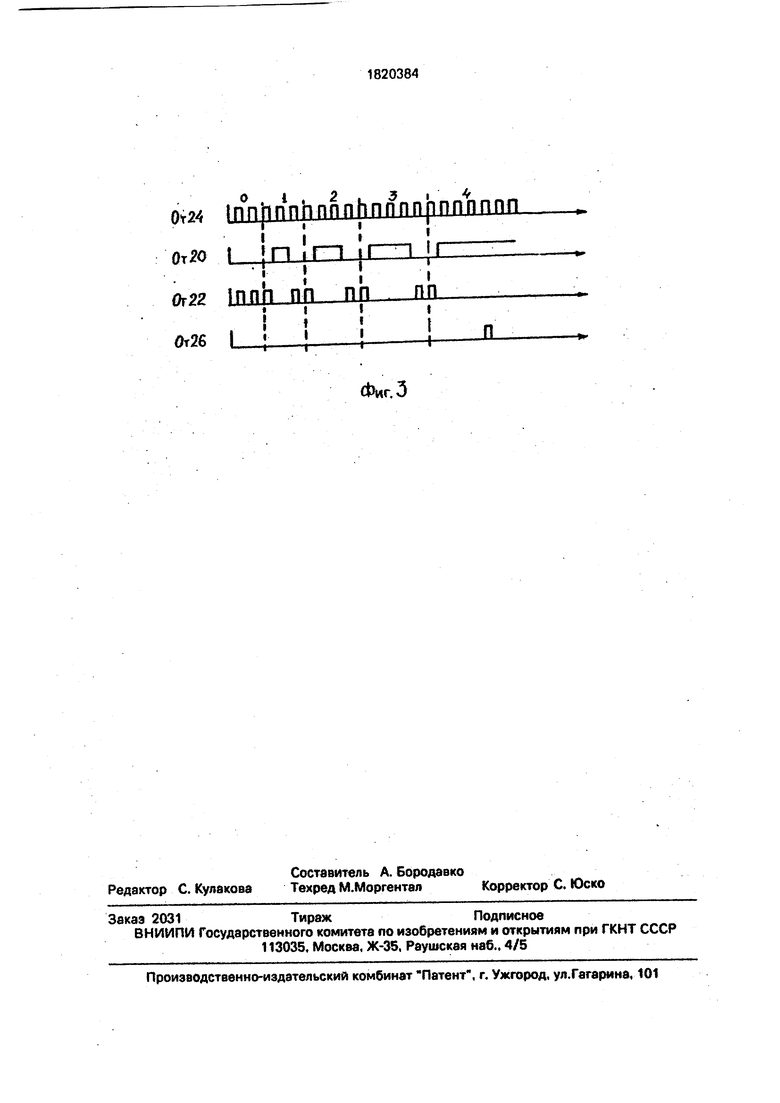

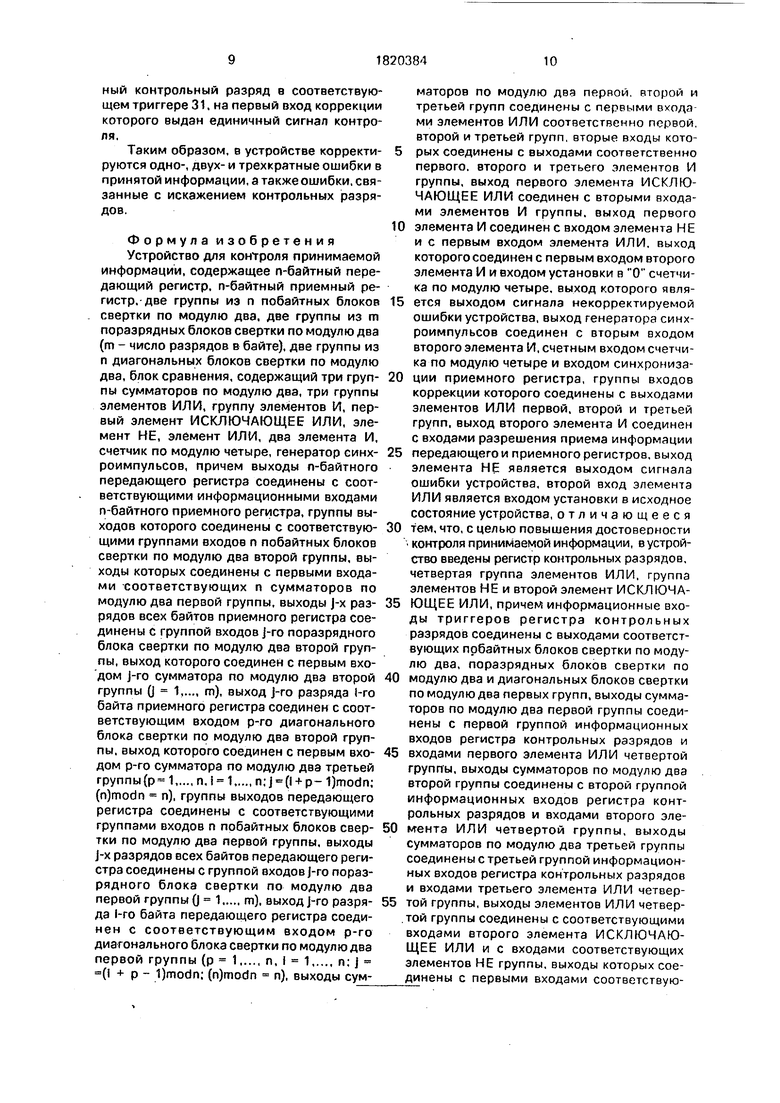

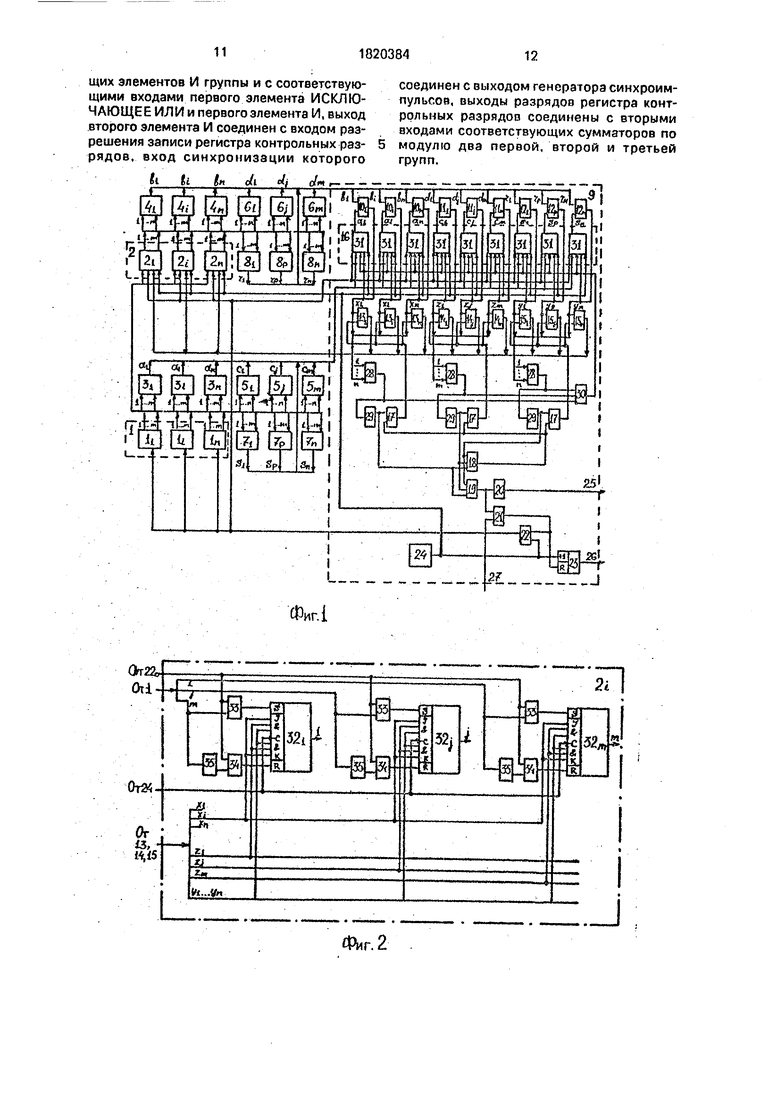

На фиг. 1 представлена функциональная схема устройства для контроля принимаемой информации; на фиг. 2 - функциональная схема i-ro байта приемного регистра устройства; на фиг. 3 - временные диаграммы работы устройства.

Устройство содержит (фиг. 1) п-байтный передающий регистр 1,. n-байтный приемный регистр 2. первую 3 и вторую 4 группы из п побайтных блоков свертки по модулю два, первую 5 и вторую 6 группы из m поразрядных блоков свертки по модулю два, первую 7 и вторую 8 группы из п диагональных блоков свертки по модулю два. блок 9 сравнения, содержащий первую 10, вторую 11 и третью 12 группы сумматоров по модулю два, первую 13. вторую 14 и третью 15 группы элементов ИЛИ, регистр 16 контрольных разрядов, группу 17 элементов И. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, первый элемент

00

ю о

OJ

со

N

И 19, элемент НЕ 20. элемент ИЛИ 21, второй элемент И 22, счетчик по модулю четыре 23, генератор синхроимпульсов 24, выход 25 сигнала ошибки устройства, выход 26 сигнала некорректируемой ошибки устройства, вход 27 установки в исходное состояние устройства, четвертую группу 28 элементов ИЛИ, группу 29 элементов НЕ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛ И 30. Кроме того, регистр 16 контрольных разрядов содержит группу триггеров 31.

Элементы устройства соединены следующим образом (фиг. 1). Выходы п-байтного передающего регистра 1 соединены с соответствующими информационными входами n-байтного приемного регистра 2, группы выходов которого соединены с соответствующими группами входов п побайтных блоков свертки по модулю два второй группы 4, выходы которых соединены с первыми входами соответствующих п сумматоров по модулю два первой группы 10, выходы J-ых разрядов всех байтов 2i - 2n приёмного регистра 2 соединены с группой входов j-ro поразрядного блока свертки по модулю два второй группы 6, выход которого соединен с первым входом J-ro сумматора по модулю два второй группы 11 ( 1,...,т), выход j-ro разряда 1-го байта приемного регистра 2 соединен с соответствующим входом р-го диагонального блока свертки по модулю два второй группы 8, выход которого соединен с первым входом р-го сумматора по модулю два третьей группы 12 р « 1,..., n; I 1,..., п; J ( + р - 1)modn; (n)modn п, группы выходов передающего регистра 1 соединены с соответствующими группами входов п побайтных блоков свертки по модулю два первой группы 3, выходы j-ых разрядов всех байтов 1| 1п передающего регистра 1 соединены с группой входов j-ro поразрядного блока свертки по модулю два первой группы 5 0 -.1.-, лл). выход J-ro разряда 1-го байта передающего регистра 1 соединен с соответствующим входом р-гр диагонального блока свертки по модулю два первой группы 7 р - 1,..., n; i -1 ,..., n; j - (I + р - 1)modn; . (njfanodn ая, выходы сумматоров по модулю два первой 10, второй 11 и третьей 12 групп соединены с первыми входами элементов ИЛИ соответственно первой 13, второй 14 и третьей 15 групп, вторые входы которыхсо- единены с выходами соответственно первого, второго и третьего элемента И группы 17, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторыми входами элементов И группы 17, выход первого элемента И 19 соединен с входом элемента НЕ 20 и с первым входом элемента ИЛИ 21, выход которого соединен с первым входом второго

элемента И 22 и входом установки в 0й счетчика по модулю четыре 23, выход которого является выходом 26 сигнала некорректируемой ошибки устройства, выход

генератора синхроимпульсов 24 соединен с вторым входом второго элемента И 22, счетным входом счетчика по модулю четыре 23 и входами синхронизации приемного регистра 2 и триггеров 31 регистра контрольных

разрядов 1 б, группы входов коррекции приемного, регистра 2 соединены с выходами элементов ИЛИ первой 13, второй 14 и третьей 15 групп, выход второго элемента И 22 соединен с входами разрешения приема

информации передающего регистра 1, приемного регистра 2 и триггеров 31 регистра контрольных разрядов 16, выход элемента НЕ 20 является выходом 25 сигнала ошибки устройства, второй вход элемента ИЛИ 21

является входом 27 установки в исходное состояние устройства, информационные входы триггеров 31 регистра контрольных разрядов 16 соединены е выходами соответствующих побайтных блоков свертки по модулю два 3t - Зп, поразрядных блоков свертки по модулю два 5i - 5m или диагональных блоков свертки по модулю два 71 - 7л первых групп, выходы сумматоров по модулю два 10i - Юп первой группы 12 соединены с первыми входами коррекции соответствующих п триггеров 31 регистра контрольных разрядов 16 и входами первого элемента ИЛИ четвертой группы 28, выходы сумматоров по модулю два 11i - 11m

второй группы 11 соединены с первыми входами коррекции соответствующих m триггеров 31 регистра контрольных разрядов 16 и входами второго элемента ИЛИ четвертой группы 28. выходы сумматоров по модулю

два 12i - 12n третьей группы 12 соединены с первыми входами коррекции соответствующих п триггеров 31 регистра контрольных разрядов 16 и входами третьего элемента ИЛИ четвертой группы 28, выходы элементов ИЛИ четвертой группы 28 соединены с соответствующими входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 и с входами соответствующих элементов НЕ группы 29. выходы которых соединены с первыми

входами соответствующих элементов И группы 17 и с соответствующими входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 и первого элемента И 19, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 соединен с вторыми входами коррекции триггеров 31 регистра контрольных разрядов 16, выходы которых соединены с вторыми входами соответствующих сумматоров по модулю два пбрвой 10, второй 11 и третьей 12 групп.

Приемный регистр 2, например, может быть выполнен (фиг. 2) на IK-триггерах 32 с динамическим С-входом и логикой ЗИ на I- и К-входах и содержит в каждом разряде два элемента И 33. 34 и элемент НЕ 35, образу- ющие первую, вторую и третью группы элементов,

В качестве триггеров 31 регистра контрольных разрядов 16 могут быть использованы IK-триггеры с динамическим С-входом, логикой 2И на I- и К-входах и содержащие аналогично с триггерами 32 приемного регистра 2 на установочных входах RS два элемента И и элемент Ни.

Устройство работает следующим обра- зом.

На входы синхронизации регистра 2 и триггеров 31 регистра контрольных разрядов поступают синхроимпульсы, формируемые генератором 24, а на входы разрешения приема информации приемного регистра 2, передающего регистра 1 и триггеров 31 регистра контрольных разрядов 16 - сигнал разрешения приема информации с выхода элемента И 22. Под действием этих сигналов информация с п- байтного передающего регистра 1 передается в n-байтный приемный регистр 2. Кроме того, с целью контроля принимаемой информации значения контрольных разря- дов, предварительно сформированные в побайтных блоках свертки по модулю Два 3i - Зп, в поразрядных блоках свертки по модулю два 5i - 5т и в диагональных блоках свертки по модулю два 7ч - 7П. записывают- ся в момент передачи в триггера 31 регистра контрольных разрядов 16. После приема информации в регистр 2 во вторых группах блоков свертки по модулю два 4i - 4П, 6i - 6m и 8i - 8n формируются соответству- ющие значения контрольных разрядов принятого n-байтного слова.

Значения контрольных разрядов информации с выходов передающего 1 и приемного 2 регистров формируются следующим образом. Содержимое каждого i-ro байта регистров сворачивается в соответствующем Ьом побайтном блоке свертки по модулю два первой 3 и второй 4 групп с выдачей значений контрольных разрядов соответственно ai и ЬгО 1,..., п). Одноименные j-e разряды всех байтов регистров сво- рачиваются в соответствующих j-ых поразрядных блоках свертки по модулю два первой 5 и второй 6 групп с выдачей значе- ний контрольных разрядов соответственно Cj и dj 0 1..... го, m - число разрядов в байте). Кроме того, j-ые разряды 1-ых байтов регистров сворачиваются в соответствующих р-ых диагональных блоках свертки по модулю два первой 7 и второй 8 групп с выдачей значений контрольных разрядов соответственно Sp и гр р 1...., n; I 1,.... n; J (I + р - 1)modn; (n)modn n).

Значения ai и bi контрольных разрядов переданного и принятого n-байтного информационного слова поступают на входы 1-го сумматора по модулю два первой группы 10, значения cj и dj - на входы j-ro сумматора по модулю два второй группы 11, а значения контрольных разрядов Sp и гр - на входы р-го сумматора по модулю два третьей группы 12 блока сравнения 9. В,последнем производится сравнение значений контрольных разрядов и формируются значения сигналов контроля XL Zj и ур по формулам: xi ai0bi; zj CjCj-Hdj,1 Ур sp®rp, гдеФ- символ операции сложения по модулю два.

При отсутствии ошибок в принятой в регистр 2 информации значения контрольных разрядов попарно совпадают и контрольные сигналы xi(l 1,..., n); zjQ 1,.... m); Ур(р 1.-. п) равны нулю. Нулевые сигналы xi, zj и ур при этом поступают на входы соответствующих элементов ИЛИ четвертой группы 28. С выходов этих элементов нулевые уровни сигналов поступают на входы соответствующих элементов НЕ группы 29. единичные уровни сигналов с выходов которых поступают на входы элемента И 19. на выходе которого формируется единичный сигнал. Данный сигнал поступает на первый вход элемента ИЛИ 21 и на вход элемента НЕ 20, с выхода которого формируется нулевой сигнал, свидетельствующий об отсутствии ошибок в принятой информации. Кроме того, единичный сигнал с выхода элемента ИЛИ 21 поступает на первый вход элемента И 22, на выходе которого в очередном такте работы генератора синхроимпульсов формируется сигнал разрешения приема информации.

Если при передаче информации возникает ошибка любой кратности, то значения одной иди нескольких пар контрольных разрядов не совпадают, на выходе одного или нескольких сумматоров по модулю два формируются единичные сигналы, которые поступают на входы элементов ИЛИ группы 28. В результате на выходе одного или нескольких соответствующих элементов НЕ группы 29 формируются нулевые уровни сигналов, которые поступают на входы элемента И 19 и обеспечивают формирование на выходе 25 единичного сигнала обнаружения, ошибки. При этом на первом входе элемента И 22 действует нулевой сигнал, который запрещает формирование сигналов разрешения приема информации до тех пор, пока ошибка не. будет откорректирована. Таким образом, в устройстве устанавливается режим коррекции ошибок.

Коррекция ошибок осуществляется путем инвертирования значений тех разрядов приемного регистра, в которые приняты искаженные данные, Следует отметить, что в режиме коррекции в каждом такте работы генератора синхроимпульсов 24 инвертируются разряды приемного регистра, для которых по всем трем направлениям проверки выданы единичные сигналы контроля xi, zj и ур. Данная операция реализуется логикой, ЗИ на счетных входах триггеров 32 приемного регистра 2 (фиг. 2).

В случае возникновения в принятом п- байтном информационном слове ошибки в одном разряде (однократной ошибки) в блоке сравнения 9 сформируются для всех трех направлений проверки по одному единичному сигналу контроля xi, zj и ур. В результате на трех входах коррекции соответствующего триггера 32 приемного регистра 2 появятся единичные уровни сигналов, по которым с приходом синхроимпульса на С-входы триггеров регистра 2 будет проинвертирован искаженный разряд. Таким образом, в устройстве исправляются однократные ошибки за один такт работы генератора синхроимпульсов 24.

Двух- и трехкратные ошибки в устройстве не всегда,удается скорректировать за один такт работы генератора синхроимпульсов 24. Например, могут возникать двукратные ошибки такого вида, при которых по одному из направлений проверки не формируется единичных сигналов контроля. В этом случае с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 вырабатывается единичный сигнал, по которому с выходов элементов ИЛИ одной из групп 13, 14 или 15, соответствующей направлению проверки, где не были сформированы единичные сигналы контроля, на входы коррекции данного направления всех триггеров 32 приемного рв гистра 2 поступят единичные сигналы. С выходов элементов ИЛИ двух других групп на соответствующие входы коррекции триггеров 32 поступают значения сигналов контроля, сформированные в сумматорах по модулю два блока сравнения 9. При этом по синхроимпульсу с выхода генератора 24 осуществляется инвертирование наряду с искаженными одного или двух неискаженных разрядов приемного регистра 2. Таким образом, после первого такта коррекции двукратной ошибки такого вида она превращается в однократную или двукратную ошибку, которые могут быть скорректированы в следующем такте. В результате, асе двукратные ошибки в устройстве корректируются, за один или два такта работы генератора синхроимпульсоа 24.

Аналогичным, образом осуществляется коррекция ошибок третьей кратности. Пои

этом они могут быть исправлены за один., два или три такта работы генератора синхроимпульсов 24. Остаются неисправленными лишь 100% ошибок третьей кратности, которые характеризуются тем, что каждому

0 из трех искаженных разрядов в п-байтном информационном слове соответствует только один или два единичных сигнала из трех направлений контроля xi, Zj и ур.

После коррекции ошибок снимается

5 сигнал обнаружения ошибки с выхода 25 устройства, а на выходе элемента И 22 формируется сигнал разрешения приема. Передача информации из регистра 1 в регистр 2 продолжается.

0 При возникновении некорректируемой ошибки счетчик по модулю четыре 23 после трех тактов коррекции в следующем такте формирует сигнал некорректируемой ошибки. На временной диаграмме (фиг. 3) обоз5 начены:

О - работа устройства при отсутствии ошибок;

1,2 и 3 - работа устройства при возникновении одно-, двух- или трехкратных оши0 бок различных видов;

4 - работа устройства при возникновении некорректируемой ошибки.

При отсутствии ошибок или при установке устройства в исходное состояние по5 еле устраненияпоследствий некорректируемой ошибки счетчик по модулю четыре 23 устанавливается в нулевое состояние единичным сигналом, формируемым на выходе элемента ИЛИ 21.

0 Следует заметить, что в процессе передачи п-байтного информационного слова формируется и выдается в блок сравнения 9 2n+m значений контрольных разрядов, которые также могут искажаться, как и значе5 ния информационных разрядов. В случае искажения контрольного разряда при правильно принятой в регистр 2 информации в блоке сравнения 9 сформируется на одном из направлений проверки единичный сиг0 . нал контроля. При этом на выходе соответствующего элемента ИЛИ четвертой группы 28 появится единичный уровень сигнала при нулевых сигналах на двух других элементах данной группы 28. В результате, на выходе

5 второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 сформируется единичный сигнал, который поступит на вторые входы коррекции триггеров 31 регистра контрольных разрядов 16, Это позволит по синхроимпульсу с выхода генератора 24 скорректировать искаженный контрольный разряд в соответствующем триггере 31. на первый вход коррекции которого выдан единичный сигнал контроля,

Таким образом, в устройстве корректируются одно-, двух- и трехкратные ошибки в принятой информации, а также ошибки, связанные с искажением контрольных разрядов.

Формула изобретения Устройство для контроля принимаемой информации, содержащее n-байтный передающий регистр, n-байтный приемный регистр,-две группы из п побайтных блоков свертки по модулю два. две группы из m поразрядных блоков свертки по модулю два (т - число разрядов в байте), две группы из п диагональных блоков свертки по модулю два, блок сравнения, содержащий три группы сумматоров по модулю два, три группы элементов ИЛИ, группу элементов И, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, элемент ИЛИ, два элемента И, счетчик по модулю четыре, генератор синхроимпульсов, причем выходы л-байтного передающего регистра соединены с соответствующими информационными входами n-байтного приемного регистра, группы выходов которого соединены с соответствующими группами входов п побайтных блоков свертки по модулю два второй группы, выходы которых соединены с первыми входами соответствующих п сумматоров по модулю два первой группы, выходы j-x разрядов всех байтов приемного регистра соединены с группой входов j-ro поразрядного блока свертки по модулю два второй группы, выход которого соединен с первым вхо- дом j-ro сумматора по модулю два второй группы 0 Ч.--, гл), выход j-ro разряда 1-го байта приемного регистра соединен с соответствующим входом р-го диагонального блока свертки по модулю два второй группы, выход которого соединен с первым входом р-го сумматора по модулю два третьей группы (р 1,..., n,i 1,..., + p- 1)modn; (n)modn п), группы выходов передающего регистра соединены с соответствующими группами входов п побайтных блоков свертки по модулю два первой группы, выходы j-x разрядов всех байтов передающего регистра соединены с группой входов j-ro поразрядного блока свертки по модулю два первой группы (j 1...., т), выход j-ro разряда 1-го байта передающего регистра соединен с соответствующим входом р-го диагонального блока свертки по модулю два первой группы (р 1,..., п, I 1,..., n: j 0 + р - 1)modn; (n)modn п), выходы сумматоров по модулю два первой, второй и третьей групп соединены с первыми входа ми элементов ИЛИ соответственно первой. второй и третьей групп, вторые входы кото- 5 рых соединены с выходами соответственно первого, второго и третьего элементов И группы, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторыми входами элементов И группы, выход первого

0 элемента И соединен с входом элемента НЕ и с первым входом элемента ИЛИ. выход которого соединен с первым входом второго элемента И и входом установки в О счетчика по модулю четыре, выход которого явля5 ется выходом сигнала некорректируемой ошибки устройства, выход генератора синхроимпульсов соединен с вторым входом второго элемента И, счетным входом счетчика по модулю четыре и входом синхрониза0 ции приемного регистра, группы входов коррекции которого соединены с выходами элементов ИЛИ первой, второй и третьей групп, выход второго элемента И соединен с входами разрешения приема информации

5 передающего и приемного регистров, выход элемента НЕ является выходом сигнала ошибки устройства, второй вход элемента ИЛИ является входом установки в исходное состояние устройства, отличающееся

0 тем, что, с целью повышения достоверности контроля принимаемой информации, в устройство введены регистр контрольных разрядов, четвертая группа элементов ИЛИ. группа элементов НЕ и второй элемент ИСКЛЮЧА5 ЮЩЕЕ ИЛИ, причем информационные входы триггеров регистра контрольных разрядов соединены с выходами соответствующих побайтных блоков свертки по модулю два, поразрядных блоков свертки по

0 модулю два и диагональных блоков свертки по модулю два первых групп, выходы сумматоров по модулю два первой группы соединены с первой группой информационных входов регистра контрольных разрядов и

5 входами первого элемента ИЛИ четвертой группы, выходы сумматоров по модулю два второй группы соединены с второй группой информационных входов регистра контрольных разрядов и входами второго эле0 мента ИЛИ четвертой группы, выходы сумматоров по модулю два третьей группы соединены с третьей группой информационных входов регистра контрольных разрядов и входами третьего элемента ИЛИ четвер5 той группы, выходы элементов ИЛИ четвер- .той группы соединены с соответствующими входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входами соответствующих элементов НЕ группы, выходы которых сое- динены с первыми входами соответствующих элементов И группы и с соответствую-соединен с выходом генератора синхроимицими входами первого элемента ИСКЛЮ-пульсов, выходы разрядов регистра контЧАЮЩЕЕ ИЛ И и первого элемента И, выходрольных разрядов соединены с вторыми

второго элемента И соединен с входом раз-входами соответствующих сумматоров по

решения записи регистра контрольных раз-5 модулю два первой, второй и третьей

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля принимаемой информации | 1984 |

|

SU1242960A1 |

| Устройство для контроля принимаемой информации | 1981 |

|

SU1023333A1 |

| Устройство для контроля принимаемой информации | 1977 |

|

SU739538A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для обнаружения ошибок при передаче кодов | 1983 |

|

SU1091211A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для обнаружения и коррекции ошибок в трактах лересылки информации электронно-вычислительных машин. Цель изобретения - повышение достоверности контроля принимаемой информации. В устройство, содержащее n-байтный передающий регистр, n-бзйтный приемный регистр, ,2п побайтных блоков свертки по модулю два, 2т поразрядных блоков свертки по модулю два. где m - число разрядов в байте. 2п диагональных блоков свертки по модулю два, блок сравнения, содержащий три группы сумматоров по модулю два, три группы элементов ИЛИ, группу элементов И. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ. элемент ИЛИ. два элемента И, счетчик по модулю четыре, генератор синхроимпульсов, введены регистр контрольных разрядов, четвертая группа элементов ИЛИ, группа элементов НЕ и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. В устройстве с целью контроля передачи информации формируются контрольные разряды передаваемого и принимаемого п-байтного слова, по которым в блоке сравнения формируются сигналы контроля по трем направлениям проверки. Это позволяет корректировать в устройстве одно-, двух- и трехкратные ошибки, а также ошибки, связанные с искажением контрольных разрядов, что существенно повышает достоверность контроля принимаемой информации. 3 ил. ел с

рядов, вход синхронизации которого V

Orffl Oti

групп.

П

..

Фиг. 2

оТ24 inn pnnhnnnhnnnnpnnihnnn

Фиг.З

| Устройство для контроля принимаемой информации | 1981 |

|

SU1023333A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля принимаемой информации | 1984 |

|

SU1242960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1993-06-07—Публикация

1991-02-25—Подача