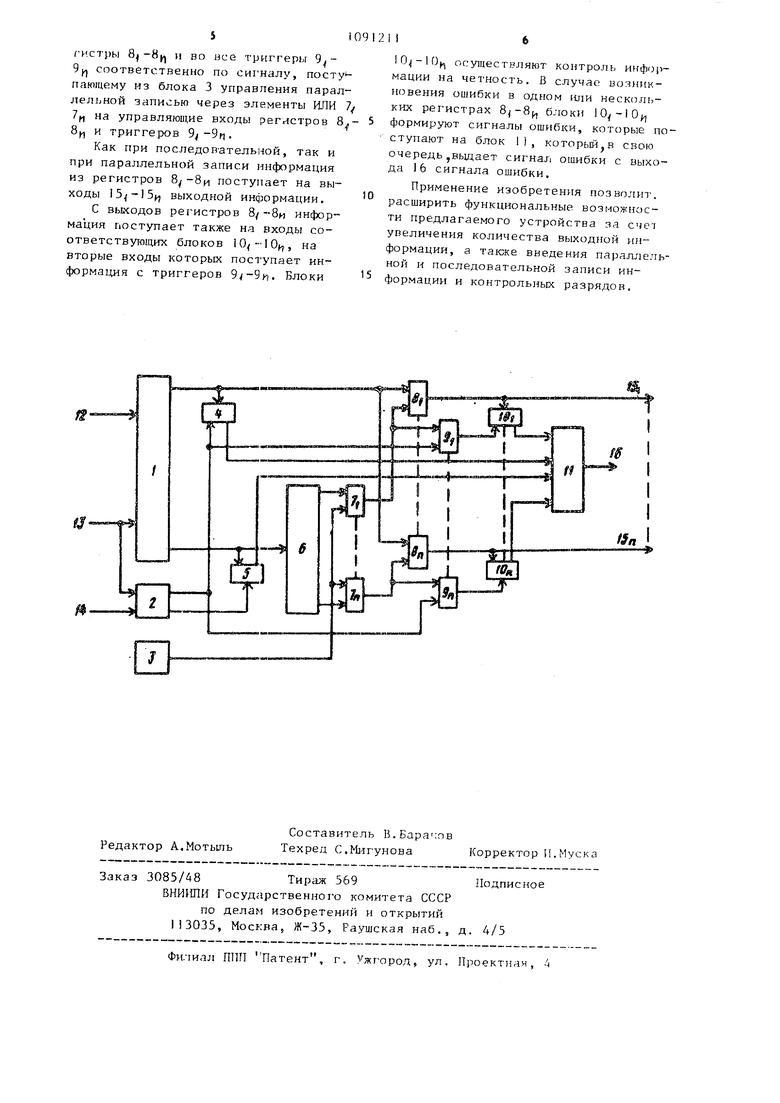

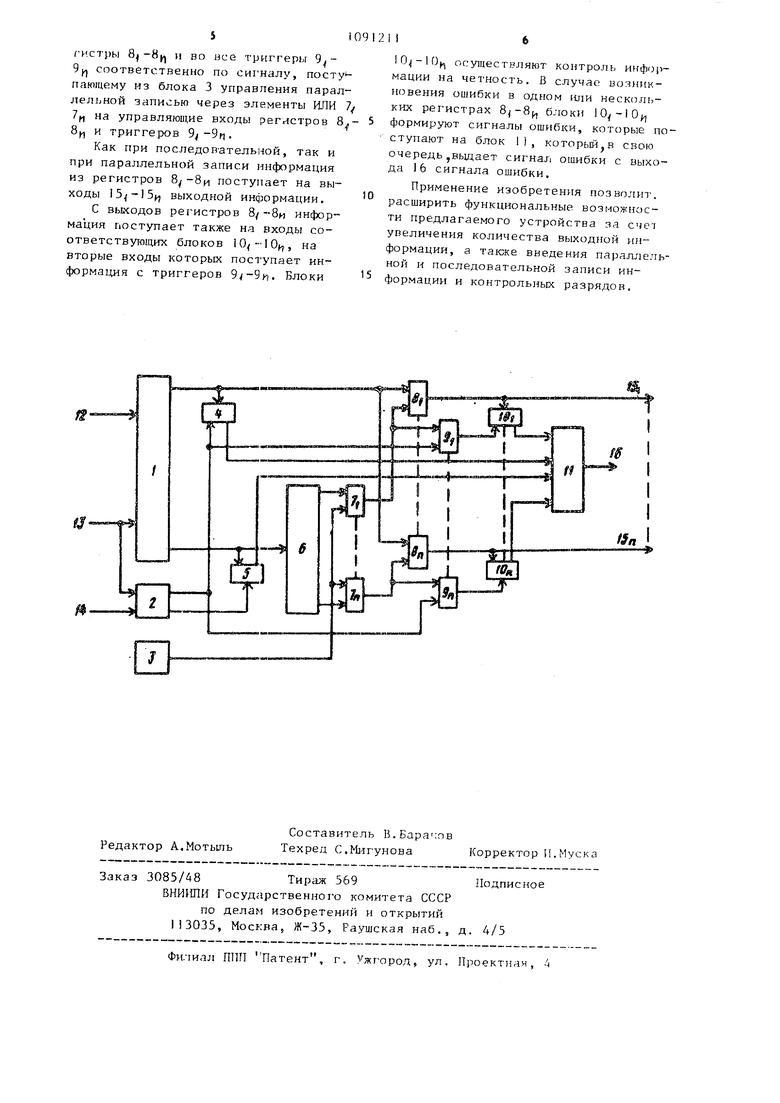

1 Изобретение относится к вычислительной технике, а имекно к устройс вам для автоматизированного контрол правильности функционирования устройств управления, в частности коммутаторов шш блоков выдачи дискрет ной информации. Известно устройство для контроля принимаемой информации, содержащее п-байтный передающий регистр, п-бай ный приемный регистр, блоки свертки по модулю два, вторую группу блоков свертки по модулю два, две группы дополнительных блоков свертки по мо дулю два и блок сравнения,, С целью контроля передачи информ ции каждый байт инфсфмации передающего регистра сЕорачивается соответствующим блоком свертки о модулю два, который формирует контрольный разряд в соответствии с содержимым передающего регистра. После завершения передачи информации в приемный регистр содержимое этого регистра сворачивается соответствую щим блоком из второй группы блоков свертки по модулю два, которые форм руют контрольные разряды байтов в соответствии с содержим з1м принятой информации в приемный регистр. Далее значения соответствующих байтов контрольных разрядов сравниваются и. если они не равны, то на выходе блока сравнения вырабатывает ся сигнал сбоя при передаче информации. С целью обнаружения ошибок кратности 2 предлагаемое устройство содержит две группы дополнительных блоков по модулю два и передающих и приемных регистров flj. Недостаток данного устройства ограниченные функциональные возможности. Такое устройство не обеспечивает полную проверку блоков контроля при передаче информации на регистры. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для обнаружения ошибок в контрольном оборудовании, содержащее входной регистр, триггер контрольного разряда входного рехистра, п регистров, п триггеров контрольного .разряда, п триггероЕ; управления, п блоков формирован1 л контроль ного разряда, блок выработки сигнала ошибок, триггер режима проверки. 112 две группь элементов И и группу элементов ИЛИ, В данном устройстве происходит проверка блоков контроля в случае, когда производятся контролируемые пересыпки отдельньк порций информации из регистра вместе с общим контрольным разрядом., информация с входного pei-истра поступает на п регистров и на п блоков формирования контрольного разряда. Блок выработки сигнала ошибки обеспечивает контроль правильности принятой информации. Элементы 2И-ЗИ-ИЛИ обеспечивают запись контрольных разрядов в п триггеров контрольного разряда, поступающих из соответствующих блоков формирования контрольного разряда или из триггера контрольного разряда входного регистра. Триггер режима проверки и п триггеров управления служат для управления записью, а а блоков формирования контрольного разряда обеспечивают контроль правильности записи информации в п регистров C2j. Недостатками известного устройства являются сложность его функциональной схемы, которая приводит к необходимости формировать контрольные разряды и управлять записью контрольными разрядами, а также ограниченные функциональные возможности, определяемые тем, что информация с входного регистра поступает по частям на п регистров, что ограничивает количество управляемых регистров. Цель изобретения - упрощение устройства с расширением его функциональных возможностей путем обеспечения последовательной или параллельной записи информации с входного регистра в п регистров по заданной программе. Поставленная цель достигается тем, что в устройство, содержащее входной регистр, входы которого являются входами устройства, а первый выход соединен с первыми входами п выходных-регистров, п триггеров, п блоков контроля на четкость и п злементов ИЛИу каждого элемента ИЛИ через соответствз ющий выходной резистор подключен к первому входу соответствующего блока контроля на четкость, второй вход которого через соответствующий триггер соединен с выходом соответствующего элемента ИЛИ, а выходы всех блоков контроля на четкость подключены к 3 первым входам блока формирования сигнала ошибки, выход которого явля ся выходом устройства, а также регистр контрольных разрядов, первый выход которого подключен к вторым входам триггеров, введены блок упра ления параллельной записью, подключенный выходом к вторым входам элем тов ИШ, два блока контроля по модулю два и дешифратор, каждый выход которого подключен к первому входу соответствующего элемента ИЛИ, а вы ход соединен с вторым выходом входного регистра и первым входом перво блока контроля по модулю два, подключенного выходом к входу блока формирования сигнала ошибки, а вторым входом - к второму выходу регис ра контрольных разрядов, первьш вхо второго блока контроля по модулю два соединен с первым выходом входного регистра, второй вход - с первым выходом регистра контрольных ра рядов, а выход - с входом блока формирования сигнала ошибки. На чертеже приведена функгсиональ ная схема устройства. Устройство содержит входной регистр 1, регистр 2 контрольных разрядов, блок 3 управления параллельной записью, блоки 4 и 5 контроля п модулю два, дешифратор 6, элементы ИЛИ выходные регистры , триггеры , блоки контроля на четкость , блок 11 формирования сигнала ошибки, вход 12 информации, вход 13 строба, вход 14 контрольных разрядов, выходы 15 15|/1 выходной информации и выход 16 сигнала ошибки. Устройство работает следующим образом. На вход 12 информации регистра 1 поступают два байта информации в сопровождении двух контрольных разрядов, подаваемых на вход 14 контрольных разрядов. Информация с входа 12 информации регистра 1 и входа 14 контрольных разрядов регистра 2 принимается в регистр 1 и регистр 2 по стробу, поступающему с входа 13. Состояние регистра 1 конт ролируется блоками4 и 5. Каждый из блоков 4 и 5 контролирует один байт информации, причем каждый байт информации поступает в сопровождении своего контрольного разряда, который из регистра 2 подается на соответствующие блоки 4 и 5. При пра1 I вильном приеме информлци1 в регистрах 1 на выходе блоков i и 5 сигнал ошибки не вьщается. При нозникноисНИИ ошибки на выходах блоков 4 и 5 сигнал ошибки поступает в блок 1. С выхода регистра 1 первый байт информации поступает на информационные входы регистров ,. Контрольный разряд первого байта информации из регистра 2 поступает на три:- геры . Второй байт информации из регистра 1 поступает на дешифратор 6, причем сюда может поступить как весь байт информации, так и часть его. Максимально дешифратор 6, уцравляемьш одним байюм информации, может обеспечить управление 256 регистрами. Запись информации в регистры и-контрольных разрядов в триггеры 9)-9 и может осуществляться в зависимости от режима работы как последовательно, так и параллельное Элементы ИЛИ 7 -1 предназначены для обеспечения возможности управления последовательной записью дешифратором 7 и параллельной записью при поступлении управляющего сигнала от блока 3. Дешифратор 6 служит для управления последовательной записью информации из регистра 1 в регистры ,, а также контрольного разряда из регистра 2 в триггеры в соответствии с информацией, поступающей но втором байте. При последовательной записи информации первьй байт информации в сопровождении контрольного разряда поступает в блок 4 и на регистры . Второй байт информации в сопровождении контрольного разряда поступает в блок 5 и на дешифратор 6. С возбужденного одного из выходов дешифратора 6 управляющий сигнал через соответствуюшдй элемент ИЛИ поступает на управляющие входы одного из регистР - 8.(-8иодного из триггеров 9 9fi , при этом первый байт информации и его контрольный разряд записываются в один из регистров 8(- 8 м в один из триггеров 9 1При последовательной записи в каждый из регистров и триггеров может записываться в любой последовательности любая информация. При параллельной записи информации первый байт информации и его контрольный разряд заносятся во все ре гистры ( и BO все трнггеры ) соответственно по сигналу, посту панчцему из блока 3 управления парал лельной записью через элементы ИЛИ 7f, на управляющие входы регистров 8 8, и триггеров ). Как при последовательной, так и при параллельной записи информация из регистров поступает на выходы выходной информации. С выходов регистров 8/ -8и информация поступает также на входы соответствующих блоков , на вторые входы которых поступает информация с триггеров )|. Влоки осуществляют контроль информации на четность. В случае возникновения ошибки в одном или нескол1зких регистрах 8j-8( блоки формируют сигналы ошибки, которые поступают на блок II, который,в свою очередь ,выдает сигнал ошибки с выхода J6 сигнала ошибки. Применение изобретения позволит, расширить функциональные возможности предлагаемого устройства за счет увеличения количества выходной информации, а таюке введения параллельной и последовательной записи информации и контрольных разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок при передаче кодов | 1989 |

|

SU1615723A2 |

| Устройство для обнаружения ошибок при передаче кодов | 1987 |

|

SU1509902A2 |

| Устройство для обнаружения ошибок при передаче кодов | 1985 |

|

SU1403066A2 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сопряжения абонентов с общей магистралью | 1981 |

|

SU1022142A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для контроля принимаемой информации | 1981 |

|

SU1023333A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕ КОДОВ, содержащее входной регистр, входы которого являются входами устройства, а первый вы « ход соединен с первыми входами, М РЫходных регистров, Ц триггеров, ц блоков контроля на четкость и и элементов И1Ш, выход каждого элемента И1Ш через соответствующий выходной регистр подключен к первому входу соответствующего блока контроля на четкость, второй вход которого через соответствующий триггер соединен с выходом соответствуюп1его элемента ИЛИ, а выходы всех блоков контроля .на четкость подключены к первым входам блока форг-мрования сигнала ошибки, выход которого является выходом устройства, а также регистр контрольных разрядов, первый выход которого подключен к вторым входам трихтеров, отличаюп(ееся тем, что, с целью его упроп1,ения и расширения функциональных возможностей, в него введены блок управления параллельной записью, подключенный выходом к вторым входам элементов 1-ШИ, два блока контроля по модулю два и дешифратор, каждый выход которого подключен к nepBONfy входу соответствующего элемента ИЛИ, а выход соединен с вторым i выходом входного регистра и первым входом первого блока контроля по (Л модулю два, подключенного выходом к входу блока фop D poвaния сигнала с ошибки, а вторым входом - к второму выходу регистра контрольных разрядов, первый вход второго блока контроля по модулю два соединен с выходом о входного регистра, второй вход - с со первым выходом регистра 1;онтрольных разрядов, а выход - с входом блока to формирования сигнала ошибки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обнаружения ошибок в контрольном оборудовании | 1975 |

|

SU596949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-07—Подача