1 I

Изобретение относится к цифровой вычислительной технике и может быть использовано для обнаружения и коррекции ошибок в трактах пересылки информации электронно-вычислительных машин..

Целью изобретения является ние достоверности принимаемой информации за счет коррекции двух- и трехкратных ошибок.

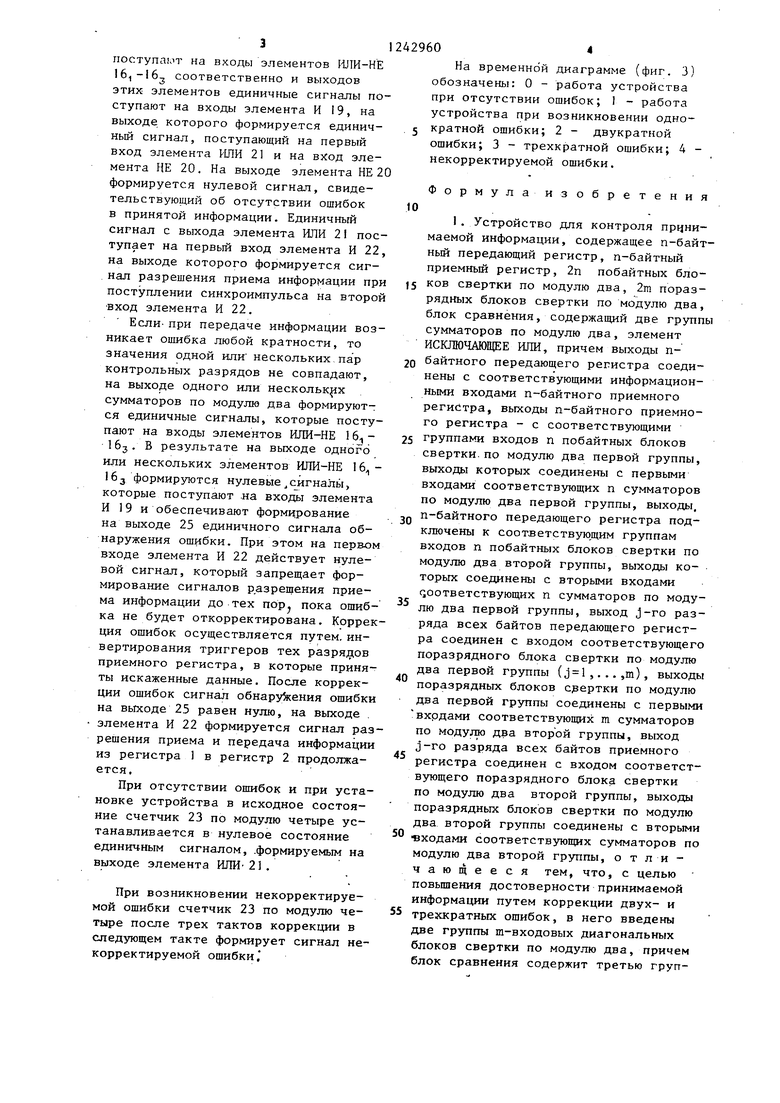

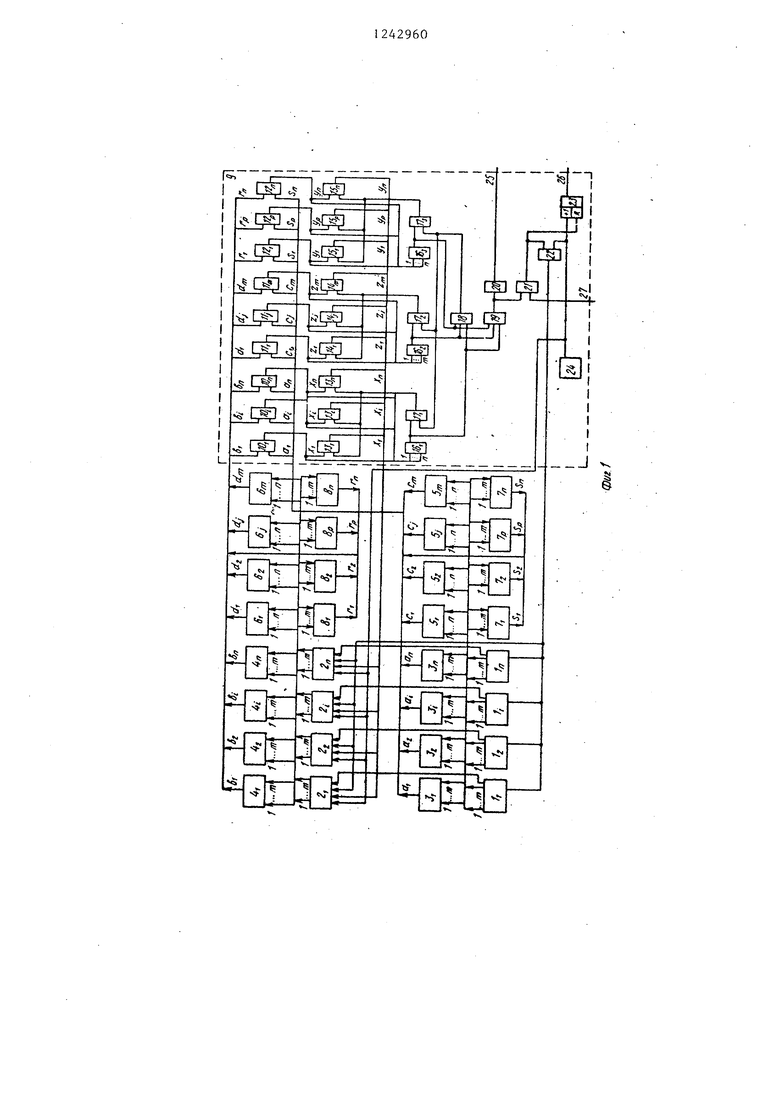

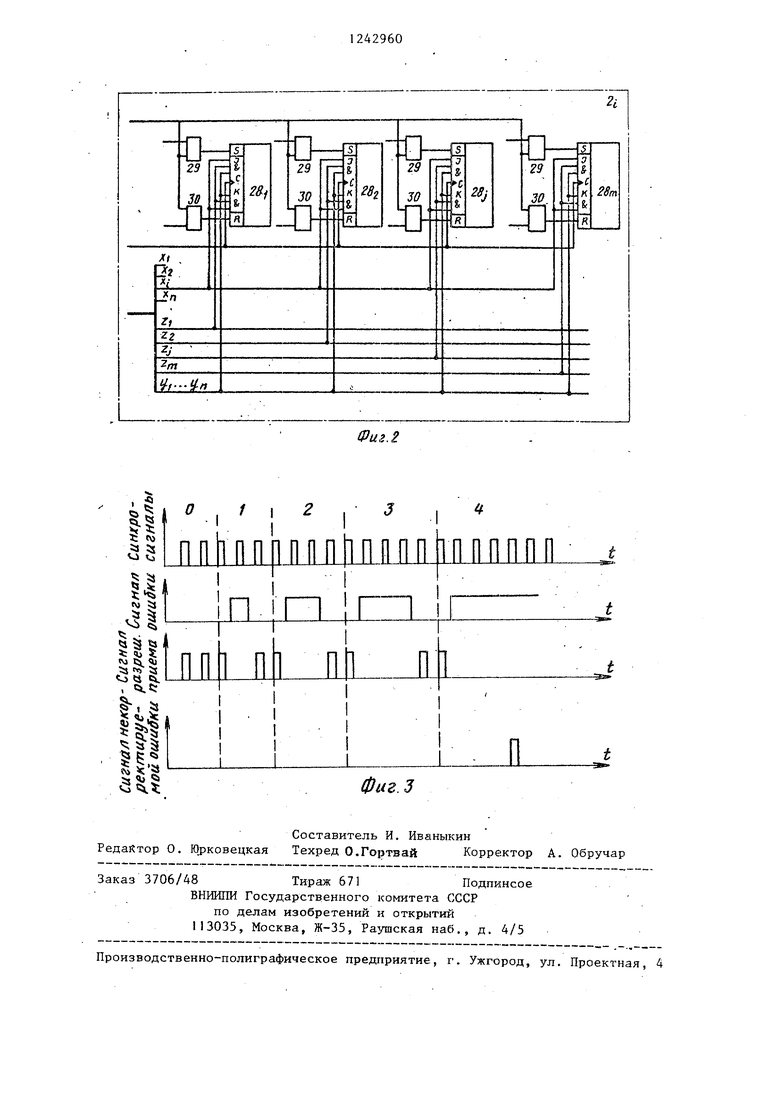

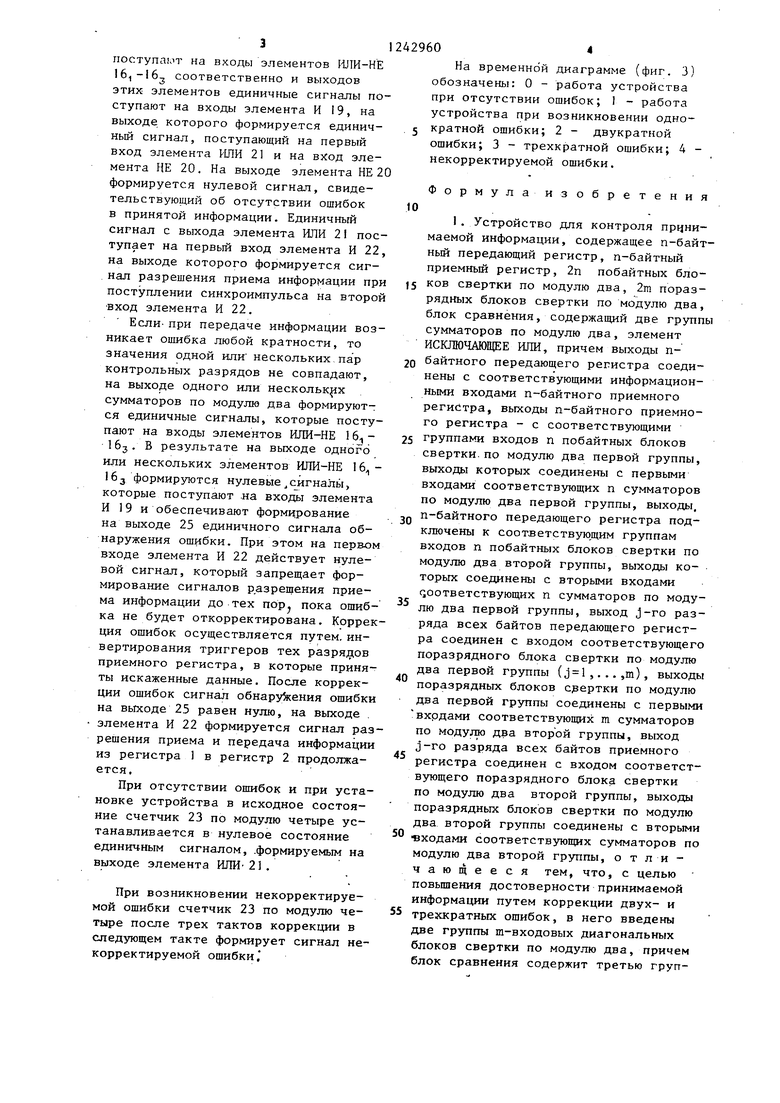

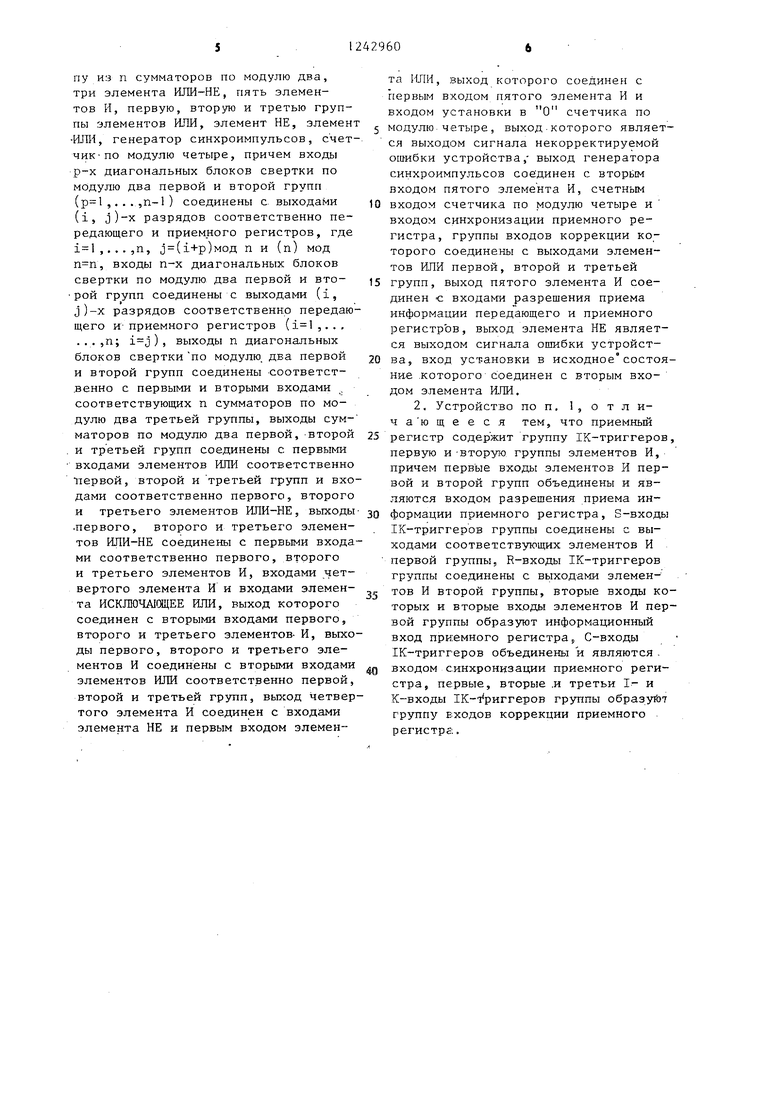

На фиг. 1 приведена структурная схема устройства для контроля принимаемой информации; на фиг. 2 - струк турная схема i-ro байта приемного регистра; на фиг. 3 - временная диаграмма работы устройства.

Устройство для контроля принимаемой информации содержит п-байтный передающий регистр 1, п-быйтный приемный регистр 2, 2п побайтных блоков и 1 f, свертки по модулю два, 2т поразрядных блоков 5 -5 и 6 -6 свертки по модулю два (т - количество разрядов в байте.), 2п диагональных блоков 7| -7 и 8 -8 свертки по модулю два, блок 9 сравнения, содержащий три группы cyNjMaTopOB 10/- 10„, 11,-11„, и. по одулю два, три группы элементов ИЛИ , 13,, и , элементы ИЛИ-НЕ , элементы И , элемент ИСКЛОЧАЮЩЕЕ ИЛИ 8, элемент И 19, элемент НЕ 20, элемент ИЛИ-21, элемент И 22, счетчик 23 по модулю четыре, генератор 24 синхроимпульсов выход 25 ошибки, выход 26 некоррек- ,тируемой ошибки и вход 27 установки в исходное состояние.

Приемный регистр выполнен на IK- триггерах 28 с динамическим С-входом и логикой 3 И на I- и К-вкодах и содержит в каждом разряде элемент И 29 и элемент И 30, образующие первую и вторую группы элементов И.

Устройство работает следующим образом.

В исходном состоянии передающий и приемный 2 регистры и счетчик 23 по модулю четыре находятся в нулевом состоянии.

В ходе работы на вход синхронизации регистра 2 поступают синхроимпульсы, формируемые генератором 24 синхроимпульсов, а на входы разрешения приема информации приемного 2 и передающего регистров - сигнал раз

429602

решения приема -информации с выхода элемента И 22.

Под действием этих сигналов информация с п-байтного передающего рех ист5 ра 1 передается вп-байтный приемный регистр 2.С целью контроля передачи информации содержимое каждого байта i .,. ( ,. . . ,п) передающего регистра I сворачивается в соответствующем бло10 ке 3i свертки по модулю два,- который

. формирует значение контрольного разряда . После приема информации в регистр 2 содержимое каждого его байта сворачивается в соответствующем

15 блоке 4., свертки по модулю два, который формирует значение контрольного разряда , Одноименные j-e разряды всех байтов передающего ре-гистра 1 сворачиваются блоком 5; свертки по

20 модулю два, формирующим значение

контрольного разряда с , а одноименные j-e разряды всех байтов приемного регистра 2 сворачиваются блоком 6j свертки по модулю два, формирующим

25 значение контрольного разряда d; (,...,m).

I .

Кроме того, относящиеся к р-й диагонали разряды передающего регистра 1 ,.| сворачиваются блоком 7р свертки по модули два, формирующим значение контрольного разряда Sp, а относящиеся к р-й диагонали разряды приемного регистра 2 сворачиваются блоком 8р свертки по модулю два, формирующим значение контрольного разряда Гр (р,...,п).

Сформированные значения контрольных разрядов а - и поступают, на входы i-TO сумматора 10 по модулю два, значения с- и dj - на входы j-ro сумматора 11по модулю два, а значения контрольных разрядов Зр и гр - на входы р-го сумматора 12 лр модулю два блока 9 сравнения. В последнем

35

40

45

с помощью сумматоров по модулю Два

производится попарное сравнение зна- ченйй контрольных разрядов а и Ъ , С и dj , Sp и Гр и формируются значения сигналов -х. 5 ZJ , у по формулам

.№. ; .; у -Sp ®r , где ® - символ операции сложения по

модулю два.

При отсутствии ошибок в принятой в.регистр 2 информации значений конт- ольюах разрядов попарно совпадают, значения сигна;аов х,-(i ,. , . ,п) , 2ij (j l ,. . . ,m) и ур ( ,. . . ,п) равны ну.шо, нулевые сигналы , z ; и ур

3

поступак т на входы элементов Ш1И-НЕ 16 -16-5 соответственно и выходов этих элементов единичные сигналы поступают на входы элемента И 19, на выходе которого формируется единичный сигнал, поступающий на первый вход элемента РШИ 21 и на вход элемента Р1Е 20. На выходе элемента НЕ 2 формируется нулевой сигнал, свидетельствующий об отсутствии ошибок в принятой информации. Единичный сигнал с выхода элемента ИЛИ 2I поступает на первый вход элемента И 22 на выходе которого формируется сигнал разрешения приема информации при поступлении синхроимпульса на второй вход элемента И 22.

Если- при передаче информации возникает ошибка любой кратности, то значения одной или нескольких.пар контрольных разрядов не совпадают, на выходе одного или нескольких сумматоров по модулю два формируются единичные сигналы, которые поступают на входы элементов ИЛИ-НЕ 16-, - 163. В результате на выходе одного

или нескольких элементов ИЛИ-НЕ 16з формируются нулевые сигналы, которые поступают на входы элемента И 19 и обеспечивают формирование на выходе 25 единичного сигнала обнаружения ошибки. При этом на первом входе элемента И 22 действует нулевой сигнал, который запрещает формирование сигналов разрешения приема информации до тех пор пока ошибка не будет откорректирована. Коррекция ошибок осуществляется путем, инвертирования триггеров тех разрядов приемного регистра, в которые приняты искаженные данные. После коррекции ошибок сигнал обнаружения ошибки на выходе 25 равен нулю, на выходе . элемента И 22 формируется сигнал разрешения приема и передача информации из регистра 1 в регистр 2 продолжается.

При отсутствии ошибок и при установке устройства в исходное состояние счетчик 23 по модулю четыре устанавливается в нулевое состояние единичным сигналом, .формируемым на выходе элемента ИЛИ 21.

При возникновении некорректируемой ошибки счетчик 23 по модулю че- тыре после трех тактов коррекции в следующем такте формирует сигнал некорректируемой ошибки,

10 js

429604

На временной диаграмме (фиг. 3) обозначены: О - работа устройства при отсутствии ошибок; I - работа устройства при возникновении одно- 5 кратной ошибки; 2 - двукратной ошибки; 3 - трехкратной ошибки; 4 - некорректируемой ошибки.

Формулаиз обретения

1. Устройство для контроля принимаемой информации, содержащее п-байт- ный передающий регистр, п-байтный приемный регистр, 2п побайтных блоков свертки по модулю два, 2т поразрядных блоков свертки по модулю два, блок сравнения, содержащий две группы сумматоров по модулю два, элемент ИСКЛЮЧАКЙЦЕЕ ИЛИ, причем выходы п- байтного передающего регистра соединены с соответствующими информационными входами п-байтного приемного регистра, выходы п-байтного приемного регистра - с соответствующими группами входов п побайтных блоков свертки.по модулю два первой группы, выходы которых соединены с первыми входами соответствующих п сумматоров по модулю два первой группы, выходы, п-байтного передающего регистра подключены к соответствую,щим группам входов п побайтных блоков свертки по модулю два второй группы, выходы которых соединены с вторыми входами соответствующих п сумматоров по модулю два первой группы, выход j-ro разряда всех байтов передающего регистра соединен с входом соответствующего поразрядного блока свертки по модулю два первой группы (,...,m), выходы поразрядных блоков срертки по модулю два первой группы соединены с первыми вхрдами соответствующих га сумматоров по модулю два второй группы, выход j-ro разряда всех байтов приемного регистра соединен с входом соответствующего поразрядного блока свертки по модулю два второй группы, выходы поразрядных блоков свертки по модулю два второй группы соединены с вторыми входами соответствующих сумматоров по модулю два второй группы, отличающееся тем, что, с целью повьш1ения достоверности принимаемой информации путем коррекции двух- и трехкратных ошибок, в него введены две группы т-входовых диагональных блоков свертки по модулю два, причем блок сравнения содержит третью группу из п сумматоров по модулю два, три элемента ИЛИ-НЕ, пять элементов И, первую, вторую и третью группы элементов ИЛИ, элемент НЕ, элемент Ш1И, генератор синхроимпульсов, счетчик-по модулю четыре, причем входы р-х диагональных блоков свертки по модулю два первой и второй групп (,...,п-1) соединены с выходами (i, j)-x разрядов соответственно передающего и приемного регистров, где ,...,п, (1+р)мод п и (п) мод , входы п-х диагональных блоков свертки по модулю два первой и вто- рой групп соединены с выходами (1, j)-x разрядов соответственно передающего и- приемного регистров ( ,.., ... ,п; ) , выходы п диагональных блоков свертки по модулю два первой и второй групп соединены соответственно с первыми и вторыми входами соответствующих п сумматоров по модулю два третьей группы, выходы сум- маторов по модулю два первой, -второй и третьей групп соединены с первыми входами элементов ИЛИ соответственно первой, второй и третьей групп и входами соответственно первого, второго и третьего элементов ИЛИ-НЕ, выходы .первого, второго и третьего элементов ИЛИ-НЕ соединены с первыми входами соответственно первого, второго и третьего элементов И, входами четвертого элемента И и входами элемента ИСКЛЮЧА1СЩЕЕ ИЛИ, выход которого соединен с вторыми входами первого, второго и третьего элементов- И, выходы первого, второго и третьего элементов И соединены с вторыми входами элементов ИЛИ соответственно первой, второй и третьей групп, вьпсод четвертого элемента И соединен с входами элемента НЕ и первым входом элемен-

д (5 20 5 о

5

та ИЛИ, выход которого соединен с первым входом пятого элемента И и входом установки в О счетчика по модулю четыре, выход - которого является выходом сигнала некорректируемой ошибки устройства,- выход генератора синхроимпульсов соединен с вторьЕМ входом пятого элемента И, счетным входом счетчика по модулю четыре и входом синхронизации приемного регистра, группы входов коррекции которого соедине:ны с выходами элементов ИЛИ первой, второй и третьей групп, выход пятого элемента И соединен -с входам:и разрешения приема информации передающего и приемного регистров, выход элемента НЕ является выходом сигнала ошибки устройства, вход уст-ановки в исходное состояние .которого соединен с вторым входом э.пемента И.ПИ.

2. Устройство по п. 1, о т л и- ч а ю щ е е с я тем, что приемньш регистр содержит группу 1К-триггеров, первую и -вторую группы элементов И, причем первые входы элементов И первой и второй групп объединены и являются входом разрешения приема информации приемного регистра, S-входы 1К-триггеров группы соединены с выходами соответствующих элементов И первой группы, R-входы 1К-триггеров группы соединены с выходами элемен- тон И второй группы, вторые входы которых и вторые входы элементов И первой группы образуют информационный вход приемного регистра, С-входы 1К-триггеров объединены и являются . входом синхронизации приемного регистра, первые, вторые .и третьи I- и К-входы ТК-т риггеров группы образуй группу Е;ХОДОВ коррекции приемного регистра.

Составитель И, Иваныкин Редактор О. Юрковецкая Техред О.Гортвай Корректор А. Обручар

Заказ 3706/48Тираж 671Подпинсое

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фи,.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля принимаемой информации | 1991 |

|

SU1820384A1 |

| Устройство для контроля принимаемой информации | 1981 |

|

SU1023333A1 |

| Устройство для контроля принимаемой информации | 1977 |

|

SU739538A1 |

| Устройство для обнаружения ошибок при передаче кодов | 1983 |

|

SU1091211A1 |

| Устройство для обнаружения и исправления ошибок | 1982 |

|

SU1149263A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1392595A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

Изобретение относитс я к цифровой вычислительной техник.е и может быть использовано для обнаружения и коррекции ошибок в трактах пересылки информации электронно-вычислительных машин. Цель изобретения - повы- шение достоверности принимаемой информации за счет коррекции двух- и трехкратных ошибок. Устройство содержит п-байтные передающий и приемный регистры, 2п побайтных блоков свертки по модулю два, 2т поразрядных блоков свертки по модулю два, блок сравнения, две группы т-входо- вых диагональных блоков свертки по модулю два. 1 з.п. ф-лы, 3 ил.

| Устройство для контроля принимаемой информации | 1977 |

|

SU739538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-07-09—Подача