Изобретение относится к вычислительной технике и может быть испо зовано в качестве периферийного уст ройства специализированных и универсальных ЦВМ для вычисления функций , Sin % . Известны специализированные процессоры для вычисления ; э.пементарны функций табличного типа на основе постоянного запоминающего устройства (ПЗУ), в состав которых вхо дит регистр аргумента, в качестве которого используется регистр числа ПЗУ 1. Недостатком известного процессор является бо.пьшой объем памяти. Известен специализированный процессор для вычисления элементарных функций (цифровой интерполятор высокого порядка), содержащий входной регистр, множительное устройство, постоянное запоминающее устройство, в котором хранятся значения узловых точек функции, сумматор, ре гистр функции, две группы элементов И, выходной регистр, б.пок управления, входы входного регистра соединены с выходами ЦВМ и блока управ ления, выгсоды входного регистра doe динены с входами множительного устройства и постоянного запоминающего устройства, выходы ПЗУ соединены .со входами элементов И первой группы, входы множительного устройства соединены с выходами элементов И второй группы, выходы множительного устройства соединены с входами сумматора, входы которого также соединены с выходами элементов И первой группы, входы регистра функции подключены к выходам сумматора и блока управления, а выходы - к входам элементов И второй группы и выходного регистра, выходы блока управления соединены с входами элементов И первой и второй групп, входного и выходного регистров, выходы выходного регистра подключены к входам ЦВМ 2. Нэ.достатком этого процессора является узкий диапазон изменения аргументов. Это связано с представлением аргументов в форме с фиксированной запятой и отсутствием средств применения аргумента к интерзалу О, 1. Принципиально приведение к, интервалу может выполняться в операционном устройстве центрального процессора. Однако, во-первых, необходимо выполнение нескольких команд центральным процессором, прежде чем аргумент

передается собственно специализированному процессору, что приводит к неоправданной загрузке не только операционных устройств центрального процессора, но и командного процессора, во-вторых, увеличивается число линий связи, число которых может достигать нескольких сотен при обмене в парафазном коде.

Цель изобретения расширение диапазона представления аргументов функций.

Поставленная цель достигается тем, что в специализированный процессор, содержащий входной регистр, первый выход которого соединен с nepBfciM входом блока умножения и первым входом сумматора, выход сумматора подключен к первому входу регистра функций, выход которого соединен с первым входом выходного регистра и первыми входами элементов И первой группы, выходы которых подключены ко второму входу блока умножения, .выход блока умножения соединен со вторым входом сумматора, третий вход которого подключен к выходам элементов И второй группы, первые входы которых подключены к выходу постоянного запоминающего устройства, Лервый выход блока управления подключен ко второму входу выходного регистра и вторым входам элементов И первой группы, второй и третий выходы блока управления соединены соответственно со вторым входом регистра функции и со вторыми входами элементов И второй группы, дополнительно введены сдвигатель, запоминаклцее устройство и счетчик порядка, первый выход которого подключен к третьему входу блока умножения, выход блока умножения соединен с первым входом входного регистра, второй выход которого подключен к первому входу сдвигателя, выход сдвигателя соединен со входом постоянного запоминающего устройства, третий выход входного регистра подключен к входу зaпo iннaюlдeгo устройства, выход которого соединен с четвертьлм входом блока умножения, четвертый выход входного регистра подключен к первому входу блока управления, четвертый выход которого соединен с nepBfcw входом счетчика порядка, второй выход счетчика порядка подключен ко второму входу сдвигателя и второму входу блока управления, выход сумматора соединен со вторым входомГвходногорегистра, второй вхо счетчика порядка и третий вход входного регистра подключены к первому и второму входам процессора, к выходу которого подключен выход выходного регистра.

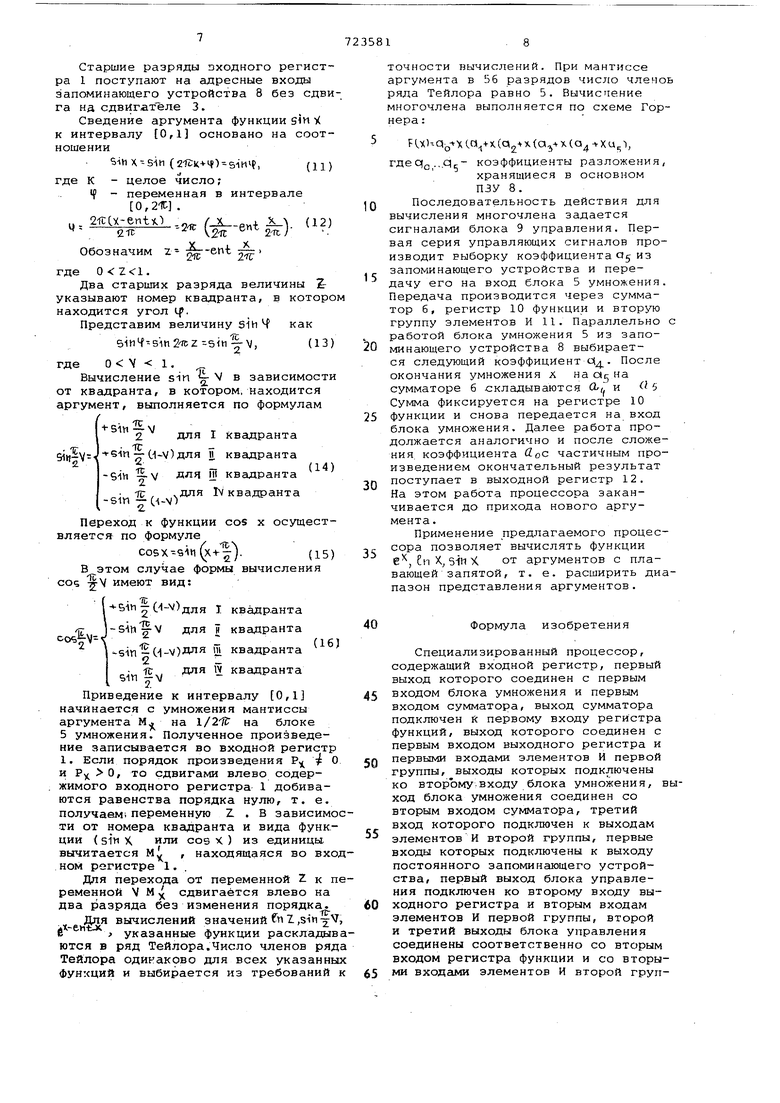

Блок-схема специализированного процессора представлена па чертеже.

11роцессор содержит входной регистр 1, счетчик 2 порядка, сдвигатель 3, запоминающее устройство 4, блок 5 умножения, сумматор 6, первую группу элементов И 7, постоянное запоминаю1Дее устройство 8, блок 9 упррвления, регистр 10 функции, вторую группу элементов И 11, выходной регистр 12.

Процессор работает следующим образом.

Представление чисел в ЦВМ находится в диапазоне + 2). Тогда для функции г диапазону изменения аргументов соответствуют три области изменения функции:

eXi 2

(1)

X о-М

Этим трем областям можно соотнести два интервала изменения аргумента:

для Г и Щ области

/XI iNtn 2 UXMtnS для Я области (2)

При в зависимости от знака X процессор генерирует либо оо либо 0. Вычисления проводятся только для второй области изменения функции. Максимальный порядок аргумента при этом

U--P.eog- N,

(3)

Для вычисления функции f в указанном диапазоне необходимо выделить целую часть аргумента, вычислить функции от обоих частей аргумента и затем перемножить полученные значения:

ioX.geniy.K-ent)

(4)

etiix

где е - функция от целой часx-entx аргумента; 5 функция от дробнОй часаргумента.

Действия по приведению аргумента к интервалу 10,1 начинаются после поступления на входной регистр 1 мантиссы аргумента (Мц), на счетчик 2 порядка аргумента Т ( ) ив блок 9 управления признака функции.

Если порядок аргумента не равен нулю, то в зависимости от знака порядка алгоритм приведения к интервалу разделяется на две В&ТВИ.. Пусть знак порядка аргумента О, тогда при Р L формируется сигнал t сл ,, если Р U г то мантисса аргумента сдвигается влево с одновременным вычитанием единицы из величины порядка. Сдвиг мантиссы продолжается до равенства порядка аргумента нулю. Разряды мантиссы, соответствующие целой части аргумента, хранятся в дополнительных разрядах входного регистра 1 и проверяются затем на равенство ну/по (условие cL}. В случае присутствия ненулевых битов из запоминающего g устройства 4 выбирается значение 6

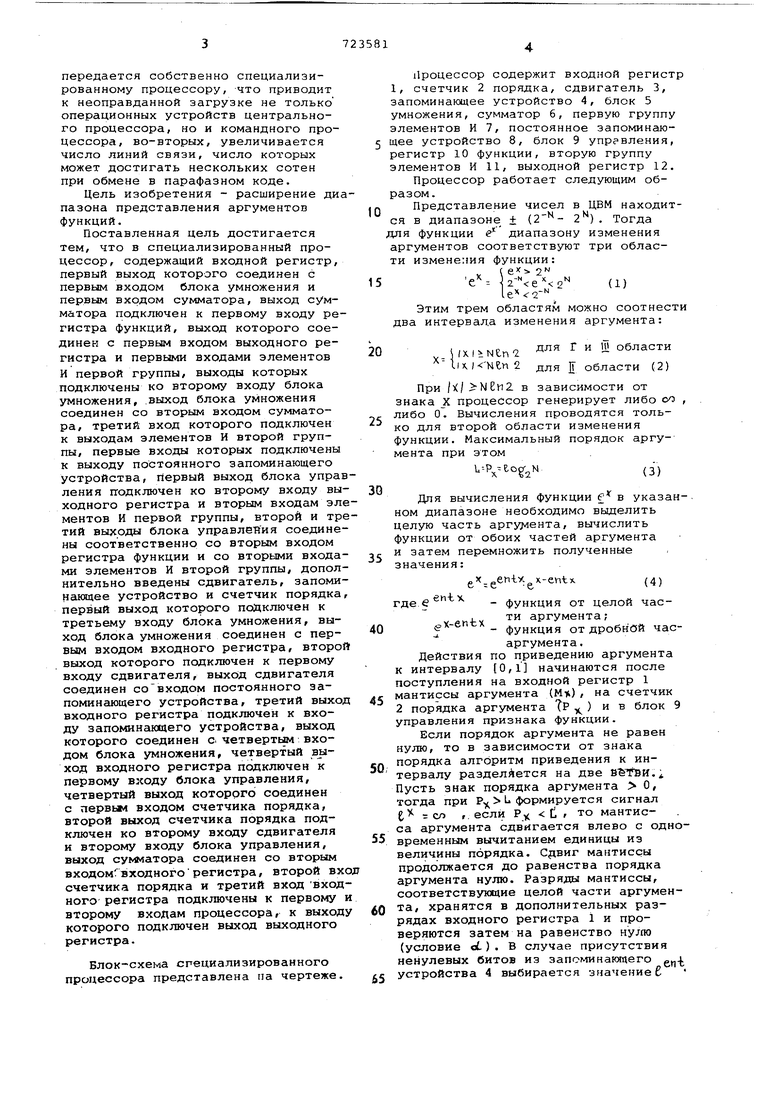

При Ру 0 необходимый сдвиг всей мантиссы аргумента вправо не происходит , а с помощью сдвигателя 3 вправо сдвигаются лишь старшие S разрядов мантиссы, где S - число адресных входов запоминающего устройства 8. Величина сдвига зависит от величины порядка аргумента, но не больше U . Работа сдвигателя 3 для 5 10, управляемого тремя последними разрядами счетчика 2 порядка, поясняется таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

Примечание. Код, получаемый на выходах сд гателя 3, служит адресом запомин щего устройства 8. Приведение к интервалу 0,1 мента функции п X основано на следующем. Пусть аргумент задается выраж РХ Wx2.(5 где М - мантисса аргумента X; Р - порядок аргумента X. Логарифмируя равенство (5), п чаем enx-tnMj T e,h2 . Имеет место равенство enWi ::Eti(Hi-z), где О 2 1; Z MV- 1; М - мантисса, сдвинутая таки образом, что может быть представ лена кодом -i2-c где Z/ - двоичная цифра числа. сдвиг выполняется до первой ситуации, при которой перед запя

+ означает наличие на выходе сдвигателя 3 значения К-го разряда входного регистра 1. той устанавливается единица, т. е. можно записать К - число сдвигов до получения кода (8). Таким образом Е,и X--Е п(лл. 2),п2 tn 2 2 BnCi+2))tnx, .(in где (PX, содержащийся на счетчике 2,.. порядка. . Действия по приведению аргумента функции к интервалу 0,1 начинаются-С анализа знака мантиссы. При отрицательном аргументе формируется сигнал Вычисление невозможно . Если знак мантиссы положительный, то аргумент сдвигается влево до появления в старшем разряде входного регистра 1 единицы. Порядок аргумента соответственно изменяется пропорционгшьно количеству сдвигов. Затем для получения дробной части величины tM (1 +Z) соцержимое регистра сдвигаемся еще раз влево без изменения кода в счетчике 2 порядка. Умножение величи.1ы (Р - к) на Ch выполняется блоком 5 умножения.

Старшие разряды зходного регистра 1 поступают на адресные входы запоминающего устройства 8 без сдвига нд сдвИгателе 3.

Сведение аргумента функции 5Ш i( к интервалу 0,1 основано на соотношении

S-iHX-SiM (sltK-vif S-iHif, (11) где к - целое число;

f - переменная в интервале 0,2Я.

2icixient0 „ (12) 2-fr Vs-n: 2-иУ

Обозначим 2 -etTt

где .

Два старших разряда величины Zуказывают номер квадранта, в котором находится угол if.

Представим величину sih Ч как

6in4--B:n2rcz-s n V,

(13) 0 1.

где

Вычисление s-in V в зависимости от квадранта, в котором, находится аргумент, выполняется по формулам

(14)

Переход к функции cos х осуществляется по формуле

cosx--siii(). (15) В этом случае формы вычисления coq V имеют вид: Приведение к интервалу 0,1 начинается с умножения мантиссы аргумента М на 1/2 на блоке 5 умножения. Полученное произведение записывается во входной регистр 1. Если порядок произведения Р 4 О и Р О, то сдвигами влево содержимого входного регистра 1 добиваются равенства порядка нулю, т. е. получаем переменную Z . В зависимос ти от номера квадранта и вида функции ( sin X или сое ч ) из единицы; вычитается М , находящаяся во вход ном регистре 1. . Для перехода ot переменной Z к пе ременной V М сдвигается влево на два разряда без изменения порядка. Для вычислений значений ч1,sin-j;. указанные функции раскладыва ются в ряд Тейлора.Число членов ряда Тейлора одинак9во для всех указанных функций и выбирается из требований к

точности вычислений. При мантиссе аргумента в 56 разрядов число члено ряда Тейлора равно 5. Вычиспение многочлена выполняется по схеме Горнера:

F иь-Од- х (о X (0,,+ X (а -. X ц ч,

где C(Q ...q,- коэффициенты разложения, хранящиеся в основном ПЗУ 8.

Последовательность действия для вычисления многочлена задается сигналами блока 9 управления. Первая серия управляющих сигналов производит выборку коэффициента Qj из запоминающего устройства и передачу его на вход блока 5 умножения Передача производится через сумматор 6, регистр 10 функции и вторую группу элементов И 11. Параллельно работой блока умножения 5 из запоминающего устройства 8 выбирается следующий коэффициент с(д. После окончания умножения х на 05 на сумматоре б складываются СЬ, и 5 Сумма фиксируется на регистре 10 функции и снова передается на вход блока умножения. Далее работа продолжается аналогично и после сложения, коэффициента doc частичным произведением окончательный результат поступает в выходной регистр 12. На этом работа процессора заканчивается до прихода нового аргумента .

Применение предлагаемого процессора позволяет вычислять функции , In X., sin X. от аргументов с плавающей запятой, т. е. расширить диапазон представления аргументов. Формула изобретения Специализированный процессор, содержащий входной регистр, первый выход которого соединен с первым входом блока умножении и первым входом сумматора, выход сумматора подключен к первому входу регистра функций, выход которого соединен с первым входом выходного регистра и первыми входами элементов И первой группы, выходы которых подключены ко ВТОРОМУ;входу блока умножения, выход блока умножения соединен со вторым входом сумматора, третий вход которого подключен к выходам элементов И второй группы, первые входы которых подключены к выходу постоянного запоминающего устройства, первый выход блока управления подключен ко второму входу выходного регистра и вторым входам элементов И первой группы, второй и третий выходы блока управления соединены соответственно со вторым входом регистра функции и со вторыми входами элементов И второй группы, отличаюшийс я тем, что, с целью расширения диапазона представления аргументов функций, в него дополнительно введены сдвигатель, запоминающее устройство и счетчик порядка, первый выход которого подключен к третьему входу блока умножения, выход блока умножения соединен с первым входом входного регистра, второй выход которого подключен к первому входу сдвигателя выход сдвигателя соединен со входом постоянного запоминающего устройства, .третий выход входного регистра подключен к входу запоминающего устройства, выход которого соединен с четвертым входом б-лока умножения, чевертый выход входного регистра подключен к первому входу блока управления, четвертый выход которого соединен с первым входом счетчика порядка, второй выход счетчика порядка подключен ко второму входу сдвигателя и второму входу блока управления, 5 выход сумматора соединен со вторым входом входного регистра, второй BiioR счетчика порядка и третий вход входного регистра подключены к первому и второму входам процессора, к выхрду которого подключен выход выходного регистра.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-03-25—Публикация

1977-10-21—Подача