ю

о

О5

Изобретение относится к вычислительной технике и может быть использовано в управляю1цих системах и гибридных вычислительных устройствах.

Целью изобретения яв.пяется расширение- функциональных возможностей засчет получения одновременно кода непрерывной величины X, кода функции 1пх и кода функции х , где z - целое положительное или отрицательное число.

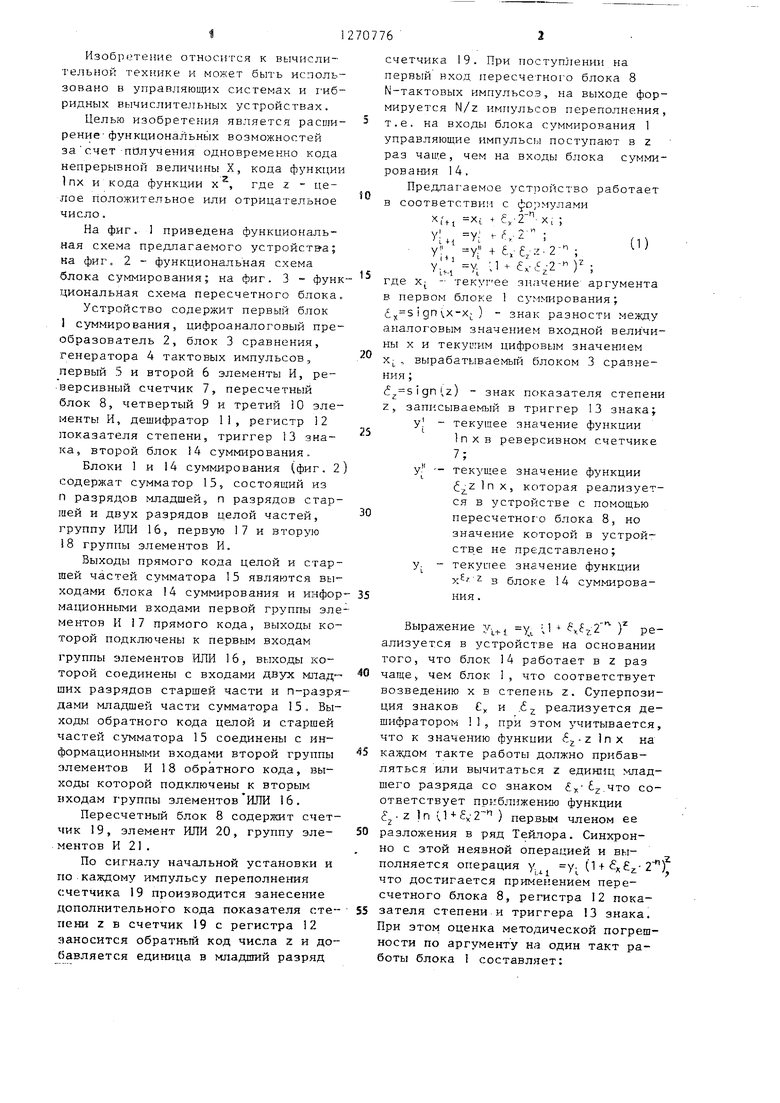

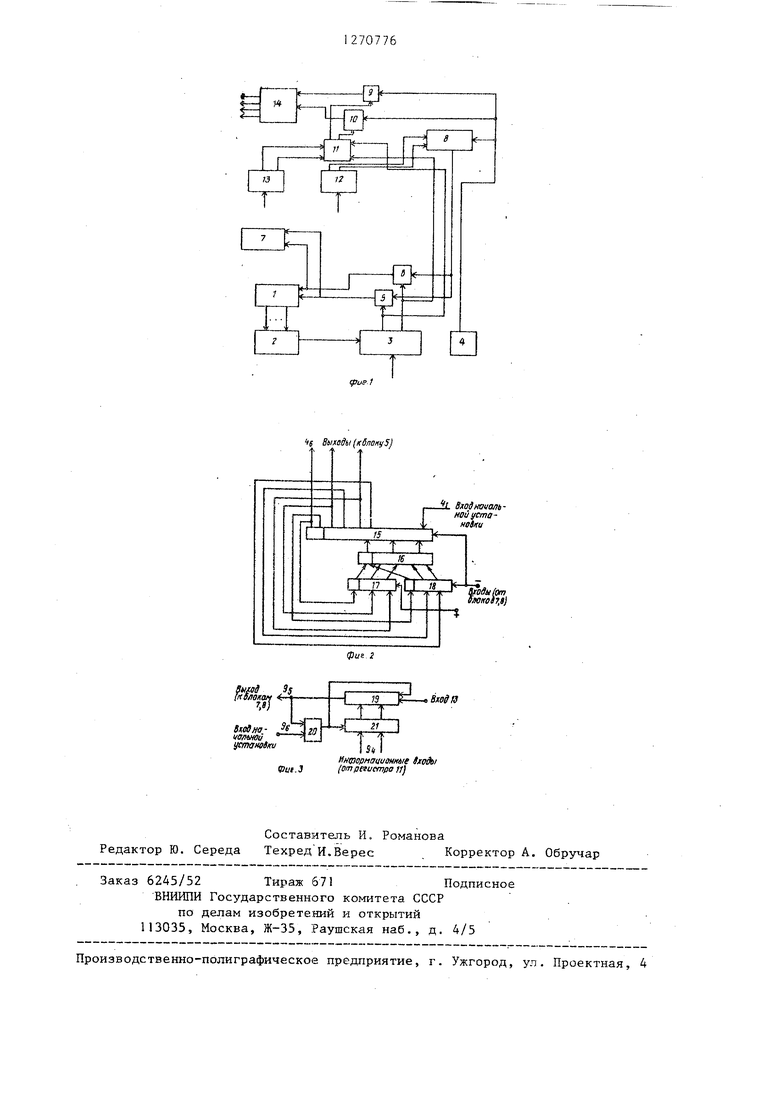

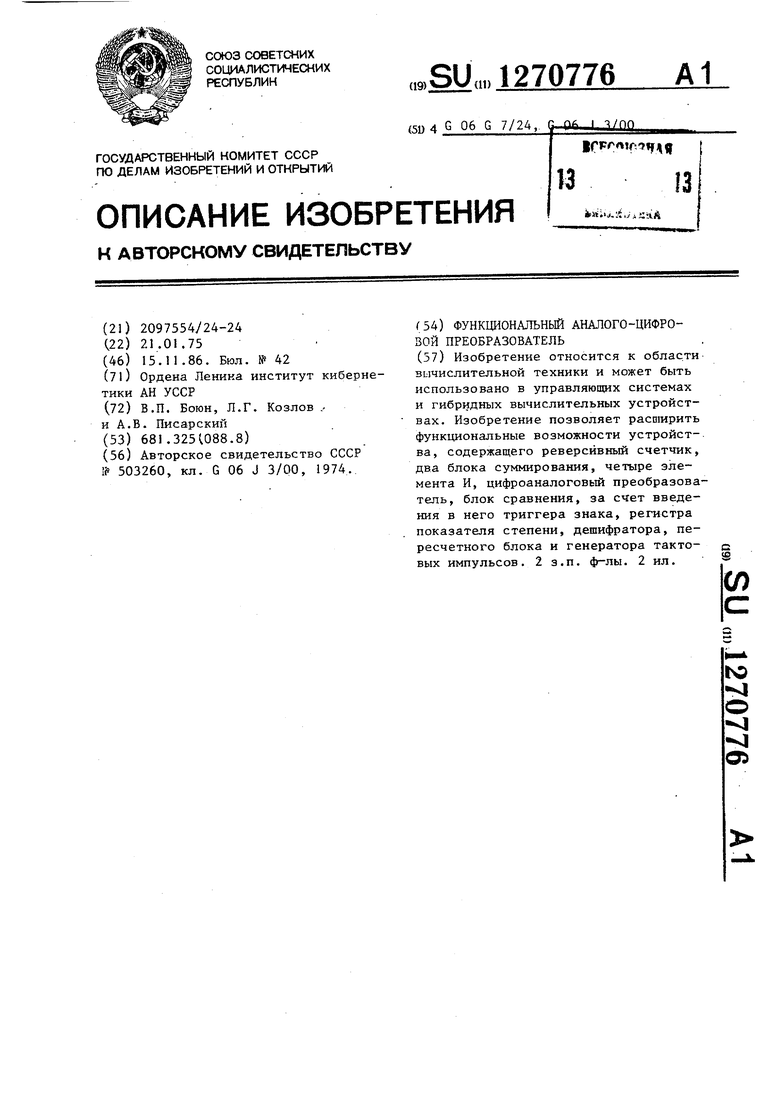

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока суммирования; на фиг. 3 - функциональная схема пересчетного блока.

Устройство содержит первый блок 1 суммирования, цифроаналоговый преобразователь 2, блок 3 сравнения, генератора 4 тактовых импульсов, первый 5 и второй 6 элементы И, реверсивный счетчик 7, пересчетный блок 8, четвертый 9 и третий 0 элементы И, дешифратор 11, регистр 12 показателя степени, триггер 13 знака, второй блок 14 суммирования.

Блоки 1 и 14 суммирования (фиг. 2 содержат сумматор IS, состоящий из п разрядов младшей, п разрядов старшей и двух разрядов целой частей, группу ИЛИ 16, первую 17 и вторую 8 группы элементов И.

Выходы прямого кода целой и старшей частей сумматора 15 являются выходами блока 14 суммирования и информационными входами первой группы элементов И 17 прямого кода, выходы которой подключены к первым входам группы элементов ИЛИ 16, выходы которой соединены с входами двух младших разрядов старшей части и п-разрядами младшей части сумматора 15. Выходы обратного кода целой и старшей частей сумматора 15 соединены с информационными входами второй группы элементов И 18 обратного кода, выходы которой подключены к вторым входам группы элементов ИЛИ 16.

Пересчетный блок 8 содержит счетчик 19, элемент ИЛИ 20, группу элементов И 21 .

По сигналу начальной установки и по каждому импульсу переполнения счетчика 19 производится занесение дополнительного кода показателя степени Z в счетчик 19 с регистра 12 заносится обратный код числа z и добавляется единица в младший разряд

счетчика 19. При поступ}1ении на первый вход пересчетного блока 8 N-тактовых импульсов, на выходе формируется N/Z импульсов переполнения, т.е. на входы блока суммирования 1 управляющие импульс) поступают в z раз чаще, чем на входы блока суммирования 14.

Предлагаемое устройство работает

Б соответстви с фор)улами Х( i ,-2 X, ; v-.-2-

У у:

(1)

I 4-1 t

)

у. y;i + е,-е, ;

.-.,-2-)где х- - текуг-ее значение аргумента в первом блоке 1 суммирования; ,(3 i gn i.x-x ) знак разности между аналоговым значением входной величины X и текуигим цифровым значением х, вырабатываемый блоком 3 сравнения ;

(f., sign(z) - знак показателя степени Z, записываемый в триггер 13 знака; у - текущее значение функции

InxB реверсивном счетчике

7;

у - текущее значение функции

In X, которая реализуется в устройстве с помощью пересчетного блока 8, но значение которой в устройстве не представлено;

у. - текущее значение функции

х в блоке 14 суммирова5 ния.

Выражение y у ;1 + } реализуется в устройстве на основании того, что блок 14 работает в z раз

О чаще чем блок I , что соответствует возведению х в степень г. Суперпозиция знаков „ и реализуется дешифратором П, при этом учитывается, что к значению функции б z Inx на

5 каждом такте работы должно прибавляться или вычитаться z единиц младшего разряда со знаком х.что соответствует приближению функции f. z In (.2 } первым членом ее

0 разложения в ряд Тейлора. Синхронно с этой неявной операцией и выполняется операция у у (1 + ) что достигается применением пересчетного блока 8, регистра 12 пока5 зателя степени и триггера 13 знака. При этом оценка методической погрешности по аргументу на один такт работы блока 1 составляет; а по функции t 2 Работа предлагаемого устройства может быть проиллюстрирована на при мере вычисления, например, функции в следящем режиме, при разрядности в устройстве . Формула изобретени 1. Функциональный аналого-цифров преобразователь, содержащий реверсивный счетчик, два блока суммирования, четыре элемента И, цифроаналоговый преобразователь и блок сравнения. первый вход которого является входной шиной, второй вход соединен с выходом цифроаналогового преобразователя а первый и второй выходы соединены с первыми входами первого и второго элементов И соответственно, выходы которых соединены с первым и вторым входами реверсивного счетчика соответственно, отличающийся тем, что, с целью расширения функциональных возможностей, в преобразователь введены триггер знака, регистр показателя степени, дешифратор пересчетный блок, генератор тактовых импульсов, выход которого соединен с первыми входами третьего и четвертого элементов И и через пересчетный блок со вторыми входами первого и второго элементов И, выходы которых соединены с первым и вторым входами первого блока суммирования соответст венно, а первые входы объединены с первым и вторым входами дешифратора соответственно, третьи входы которого соединены с выходами триггера зна ка, вход которого является второй входной шиной, первый и второй выходы дешифратора соединены со вторыми .входами третьего и четвертого элемен тов И соответственно, выходы которых подключены к первому и второму входа второго блока суммирования соответст 76 выходы которого являются первыми выходными шинами, -а третий вход объединен с третьим входом первого блока суммирования и является третьей входной шиной, выходы первого блока суммирования соединены с выходами цифроаналогового преобразователя, вход регистра показателя степени является четвертой входной шиной, а выходы соединены со вторыми входами пересчетного блока. 2. Преобразователь по п. 1, отличающийся тем, что блоки суммирования выполнены на (2п+2)-разрядном сумматоре, группе элементов ИПИ, двух группах элементов Н, первая группа выходов сумматора является выходами блока суммирования и соединена с первыми входами первой группы элементов И, выходы которой подключены к первым входам группы элементов ИЛИ, выходы которой соединены с группой входов сумматора, вторая группа выходов сумматора соединена с первыми входами второй группы элементов И, выходы которой подключены ко вторым входам группы элементов ИЛИ, первым и вторым входами блока суммирования являются вторые входы первой и второй групп элементов И соответственно, второй вход второй группы элементов И объединен со вторым входом сумматора, третий вход которого является третьим входом блока суммирования. 3. Преобразователь по п. 2, отличающийся тем, что пересчетный блок выполнен на счетчике импульсов, группе элементов И и элементе ИЛИ, первый вход которого соединен с выходом счетчика импульсов и является выходом пересчетного блока, второй вход является входом начальной установки, а выход соединен с первыми входами счетчика и группы элементов И, вторые входы последней являются вторыми входами пересчетного блока, а выходы соединены со вторыми вхрдами счетчика импульсов, третий вход которого является первым входом пересчетного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Регулятор | 1987 |

|

SU1462232A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Генератор векторов | 1986 |

|

SU1361613A1 |

| Аналого-цифровой квадратор | 1983 |

|

SU1120374A1 |

| Статистический анализатор выбросов и провалов напряжения | 1990 |

|

SU1837325A1 |

Изобретение относится к области вычислительной техники и может быть использовано в управляющих системах и гибридных вычислительных устройствах. Изобретение позволяет расширить функциональные возможности устройства, содержащего реверсивный счетчик, два блока суммирования, четыре элемента И, цифроаналоговый преобразователь, блок сравнения, за счет введения в него триггера знака, регистра показателя степени, дешифратора, пересчетного блока и генератора тактос (О вых импульсов. 2 з.п. ф-лы. 2 ил. (Л

ig Выходы {к5паку5)

. BxodHOi/ofltнойустаHOtKU

Л. II /, /7vC

Kni rfL

| Аналого-цифоровое устройство для возведения в куб | 1974 |

|

SU503260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-11-15—Публикация

1975-01-21—Подача