1

Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее блок управления, п запоминаняцих блоков с входными коммутационными элементами, адресные и разрядные формирователи токов записи с выходными коммутационными элементами, которые подключены к входным коммутационным элементам одного из запоминающих блоков, и---дешифратор запоминающих блоков 1 .

Недостатком этого запоминающего устройства является ограничение функциональных возможностей и невысокое быстродействие из-за отсут- ствия режима автоматической перезаписи информсщии из одного массива адресов в другой.

Наиболее близким по технической сущности к предлагаемому изобретению является запоминающее устройство без разрушения информации, содержащее регистр адреса, связанный с первыми, а через формирователи адресных токов записи и первый коммутатор - со вторыми входамип запоминающих блоков, третьи входы которых подключены через дешифратор базового адреса к первым выходам регистра

базового, адреса, а четвертые входы через второй коммутатор и формирователи разрядных токбв записи - к выходам регистра числа, выходы которого соединены с выходами запоминающих блоков, блок управления, первый вход которого связан с регистром установки массива адресов, второй с первым выходом блока задания режимов, а-выход - с регистром базового адреса 2 .

Недостатком этого запоминающего устройства является невысокое быстродействие из-за отсутствия режима

15 автоматической перезаписи информации из одного массива адресов в другой.

Цель изобретения - повышение бы. стродействия устройства за счет введения режима автоматической перезаписи информации из одного массива адресов в другой.

Поставленная цель достигается тем, -что в запоминающее устройство со

25 считыванием без разрушения информации, содержащее накопители, блок управления, формирователь адресных токов записи, формирователь разрядных токов записи, два коммутатора, регистр

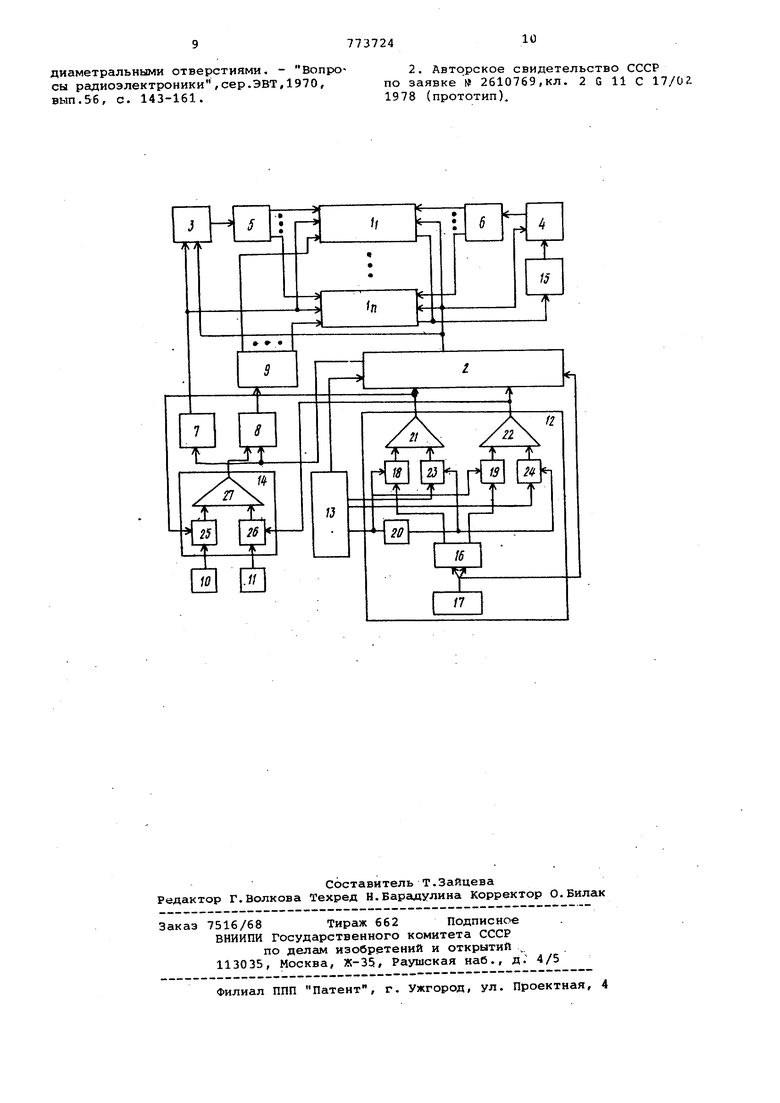

30 адреса, регистр .базового адреса. дешифратор, регистр считывания, ре гистр записи, блок местного управле ния и регистр числа, причем первые и вторые входы накопителей соединены соответственно с первым входом формирователя адресных токов записи и выходом регистра адреса и с вы ходами первого коммутатора,третьи и четвертые входы накопителей подключены соответственно к выходам дешифратора и к выходам второго ком мутатора, вход первого коммутатора соединен с выходом формирователя свдресных токов записи, второй вход которого подключен к пятым входам накопителей, первому выходу блока управления и первому входу формирователя разрядных токов записи, второй вход которого соединен с выходом регистра числа, а выход - со входом второго коммутатора, выходы накопителей подключены ко входу регистра числа, первый вход блока управления соединен с первым выходо блока местного управления, а второй выход г со входом регистра адреса и первым входом регистра базового адреса, выход которого подключен ко входу дешифратора, введены третий коммутатор и блок переключения режимов, первый, второй и третий выходы которого соединены соответственно со вторым, третьим и четвер тыми выходами блока местного управления, а первый, второй и третий выходы блока переключения режимов подключены соответственно ко второму, третьему и четвертому входам блока управления, первый и второй входы третьего коммутатора сое динены соответственно с третьим и четвертым входами блока управления третий и четвертый входы - соответственно с выходом регистра считы вания и с выходом регистра записи, выход третьего коммутатора подключен ко второму входу регистра базо вого адреса. При этом блок переключения режи целесообразно выполнить содержащим триггер, генератор импульсов, четы ре элемента И, элемент НЕ и два элемента ИЛИ, причем выход генератора импульсов соединен со счетным входом триггера, нулевой и единичн выходы которого подключены соответ ственнЬ к первым входам первого и второго элементов И, первый вход третьего элемента И, первый вход четвертого элемента И, вторые входы первого и второго элементов и вход элемента НЕ соединены соответственно с первым, вторым и тре тьим .входами блока переключения режимов.. выход элемента НЕ подключен ко вторым -входам третьего и четвертого элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ выходы второго и четвертого элементов И, подключены соответственно к первому и второму входам второго элемента ИЛИ, выходы генератора импульсов, первого и второго элементов ИЛИ соединены соответственно с первым, вторым и третьим выходами; блока переключения режимов. Третий коммутатор целесообразно выполнить содержащим .пятый и шестой элементы И и третий элемент ИЛИ, причем выходы пятого, шестого эле- . ментов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого соединен с выходом третьего коммутатора, первый и второй входы пятого элeмeнta И подключены соответственно к первому и третьему входам, а первый и второй входы шестого элемента И - ко второму и четвертому входам третьего ком 4утатора. На чертеже изображена принципиальная схема предложенного устройства. Устройство содержит накопители 1, блок 2 управления, формирователь 3 адресных токов, формирователь 4 разрядных токов записи, первый 5и второй б коммутаторы,регистр 7 адреса, регистр 8 базового адреса, дешифратор 9, регистр 10 считывания, регистр 11 записи, блок 12 переключения режимов, блок 13 местного управления, третий коммутатор 14 и регистр 15 числа. Перйые и вторые входы накопителей соединены соответственно с первым входом формирователя 3 адресных токов записи и выходом регистра 7 адреса и с выходами первого коммутатора 5. Третьи и четвертые входы накопителей 1 - 1, подключены соответственно к выходам дешифратора 9 и к выходам второго коглмутатора б. Вход первого коммутатора 5 соединен с выходом формирователя 3 адресных токов записи, второй вход которого подключен к пятым входам накопителей , 1.- 1, первому выходу блока 2 управления и первому входу формирователя 4 разрядных токов записи, второй вход которого соединен с выходом регистра 15 числа, а выход - со входом второго коммутатора б. Выходы накопиЗУ, подключены ко входу телей регистра 15 числа. Первый вход блока 2 управления соедине-н с первым выходом блока 13 местного управления, а второй выход - со входом .регистра 7 адреса и первыми входами регистра 8 базового адреса, выход которого подключен ко входу де,шифратора 9. Первый, второй и третий входы Ьлока 12 .переключения режимов соединены соотв-ётственно со вторым третьим и четвертым выходами блока 13 местного управления. Первый, второй и третий выходы- блока 12 переключения режимов подключены соответственно ко второму, тр.етьему и четвертому входам блока 2 управления. Первый и второй входы третьего коммутатора 14 соединены соответственно с третьим и четвертым входами блока управления, третями и четвертки входы - соответственно с выходом регистра,10 считывания и с выходом регистра 11 записи. Выход третьего коммутатора 14 подключен ко второму входу регистра базового адреса 8. Блок 12 переключения режимов содержит триггер 16, генератор импульсов 17, первый 18 и второй 19 элементы И, элементы НЕ 20, первый 21 и второй 22 элементы ИЛИ, третий 23 и четвертый 24 элементы И. Выход генератора 17 импульсов соединен со счетным входом триггера 16, нулевой и единичный выходы которого подключе ны соответственно к первым входс1м первого 18 и второго 19 элементов и. Первый вход третьего элемента И 23, первый вход четвертого элемента И 24 вторые входы первого 18 и второго 19 элементов И и выход элемента НЕ 20 соединены соответственно с первым, вторым и третьим выходами блока 12 переключения режимов. Выход элемента НЕ подключен ко вторым входам третьего 23 и четвертого 24 элементов И. Выходы первого 18 и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ 21. Выходы второго 19 и четвертого 24 элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ 22. Выходы генератора импульсов 17, первого 21 и второго 22 элементов ИЛИ соединены соответственно с первым, вторым и третьим выходами блока переключения режимов 12. Коммутатор 14 содержит пятый 25 и шестой 26 элементы И и третий 27 элемент ИЛИ. Выхо,ды пятого 25 и шестого 26 элементов И подключены соответственно к . первому и второму входам третьего эл мента ИЛИ 27, выход которого соедине с выходом третьего коммутатора 14. Первый и второй входы пятого элемента И 25 подключены соответственно к первому и третьему входам, а первый и второй входы шестого элемента И 26 ко второму и четвертому входам треть го коммутатора 14. Устройство работает следующим обр зом. Если блоком 13 местного управлени установлен режим перезаписи, то с ег второго выхода поступает потенциал разрешения в блок переключения режим на вторые входы первого 18 и второго 19 элементов И и на вход элемента НЕ 20, с выхода которого поступает потенциал запрещения на вторые входы третьего 23 и четвертого 24 элементов И. Под воздействием импульсов, посту пающих с выхода генератора 17 импуль сов.на счетный вход триггепа 16, последний попеременно изменяет саов состояние. Иэменяющ)-:зся ссстоя 1ия счетного триггера 16 поступают на первые входы открытых элементов И 18 и 19. В результате в соо-.ветствии с состоянием триггера 16 через элементы ИЛИ 21 и 22 на четвертый и третий входы блока 2 управления поступают потенциалы, определяющие режим работы запоминающего устройства, т.е. режим считывания или записи. Эти же потенциалы поступают на первый и второй входы третьего коммутатора 14. Таким образом, осуществляется автоматическое переключение режима работы запоминающего устройства. Потенциал, определяющий режим считывания, поступает с выхода элемента ИЛИ 21 на первый вход пятого элемента И 25, а потенциал, определяюющий режим записи, поступает с выхода элемента ИЛИ 22 на первый вход второго элемента И 26. Таким образом, в зависимости от режима работы открывается элемент И 25 или элемент И 26. В результате через элемент ИЛИ 27 на второй вход регистра базового адреса 8 поступает код одного из накопителей 1 - 1., установленный заранее на регистре 10 считывания и регистре 11 записи, и происходит поочередная выборка того из накопителей 1,,, из которого необходимо считать информацию, того из накопителей 1 - 1, в который эту информацию надо записать. Считанная из выбранного накопителя 1, информация поступает на регистр 15 числа. После автоматического переключения с режима считывания на режим записи и выборки накрпителя 1 - 1,, в который необходимо записать считанную информацию, по сигналам, поступающим со второго выхода блока 2 управления в соответствии с кодом числа, хранящимся в регистре 15 чиспа, сбрасывают формирователи разрядных токов записи 4, выходы которых соединены через разрядный коммутатор 6 с четвер-тыми входами того из накопителей 1у - (,, в котором необходимо записать информацию, и происходит запись этого числа в выбранный накопитель. Текущий адрес накопителей 1к.вырабатывается автоматически в регистре базового адреса 8 по сигналам, поступающим на его вход со второго выхода блока управления. При этом регистр 7 блока работает в хзчетном режиме. Если в блоке 13 местного управления установлен режим Считывание или Запись, то с его второго или третьего выходов соответственно поступает потенциал, определяющий режим, на первые в5{оды третьего и четвертого элементов И 23 и 24, а с четвертого выхода блока 13 местного управления поступает потенциал запре щения на вторые входы первого и второго элементов И 18 и 19 и через элемент НЕ 20 - потенциал раэрешения на вторые входы третьего и четве того элементов И 23 и 24. В результа на втором и третьем выходах блока 12 переключения режимов образуются потенциалы, определяющие режим работы в соответствии с установленным в блоке 13 местного управления. Технико-экономическое преимущество предложенного устройства заключается в том, что оно обеспечивает автоматическое переключение режимов работы устройства совместно с коммутацией базового адреса и установку массива записи, что позволяет с большой скоростью и достоверностью перезаписывать информацию из одного накопителя в другой и, в результате, повысить быстродействие запоминающего устройства со считыванием без разрушения информации . Применение предложенного устройства для отладки программ в цифровых вычислительных системах управления позволяет сократить время отладочных работ, : Формула изобретения 1. Запоминающее устройство со счи тыванием без разрушения информации, содержащее накопители, блок управления, формирователь адресных токов записи, формирователь разрядных токов записи, два коммутатора, регистр адреса, регистр базового адреса, дешифратор, регистр считывания, регист записи, блок местного управления и регистр числа, причем первые и вторые входы накопителей соединены соответственно с первым входом формирователя адресных токов записи и выходом регистра адреса и с выходами первого коммутатора, третьи и четвер тые входы накопителей подключены . соответственно к выходам дешифраторо и к выходам второго коммутатора, вхо первогоКоммутатора соединен с вы. ходом формирователя адресных токов записи, первому выходу блока управле ния и первому входу формирователя ра рядньи; токов записи, второй вход которога соединен с выходом регистра числа, а выход - со входом второго ко1умутатора, выходы накопителей подключены ко входу регистра числэ, первый вход блока управления соединен с первым выходом блока местного управления, а второй выход - со вхо дом регистра адреса и первым входом рюгист.ра базового адреса, выход кото рого подключен ко входу дешифратора отличающеес я .тем, что, с целью повышения быстродействия устройства, оно содержит третий коммутатор и блок переключения режимов, первый, второй и третий входы которого соединены, соответственно, со вторым, третьим и четвертым выходами блока местного управления,а первый,второй и третий выходы блока переключения режимов подключены соответственно ко второму, трютьему и четвертому входам блока управления, первый и второй входы третьего коммутатора соединены соответственно с третьим и четвертым входами блока управления, третий и четвертый входы - соответственно с вы- . ходом регистра считывания и с выходом регистра записи, ВЕКОД третьего коммутатора подключен ко второму входу регистра базового адреса. 2.Устройство по п.1,о т л и ч а ю- . щ е е с я тем,что блок переключения рех;.1ов содержит триггер,генератор импульсов, четыре элемента И,элемент НЕ и два элемента ИЛИ,причем выход генератора импульсов соединен со счетным входом триггера,нулевой и единичные выходы которого подключены соответственно к первым входам первого и второго элементов И, первый вход третьего элемента И, первый вход четвертого элемента И, вторые входы первого и второго элементов И и вход элемента НЕ соединены соответственно с первым, со вторым и с третьим входами блока переключения режимов, выход элемента НЕ подключен ко вторым входам третьего и четвертого элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы второго и четвертого элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выходы генератора импульсов, первого и второго элементов ИЛИ соединены соответ ственно с первым, вторым и третьим выходами блока переключения режимов. 3. Устройство по ПП.1 и 2,0 т л Йчающееся тем, что третий коммутатор содержит пятый и шестой эле- менты И и третий элемент ИЛИ, причем выходы пятого и шестого элементов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого соединен с выходом третьего коммутатора, первый и второй входы пятого элемента И подключены соответственно к первому и третьему входам, а первый и второй входы шестого элемента И - ко второму и четвертому входам третьего коммутатора . Источники информации, принятые во вним.ание при экспертизе 1. Климов И.И , и др. Полупостоянное заполняющее устройство на тороидальных магнитных сердечниках с

диаметральными отверстиями, - Вопросы радиоэлектроники,сер.ЭВТ,1970, Bbm.S6, с. 143-161.

2. Авторское свидетельство СССР по заявке 2610769,кл. 2 G 11 С 17/ог 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для контроля записи информации в блоках памяти | 1981 |

|

SU949720A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Запоминающее устройство | 1979 |

|

SU842956A1 |

| Запоминающее устройство без разрушения информации | 1978 |

|

SU750563A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-04—Подача