Изобретение относится к вычислительной технике, а именно к устройствам отображения графической информаци на дисплеях или графостроителях, а также к устройствам программного управления станками.

В этих устройствах входные данные (координаты начальной точки) преобразуются в унитарный код импульсов, действующих по каждой координате и распределенных во времени так, чтобы траектория рабочего органа была бы наилучшей аппроксимацией дуги окружности , проходящей через начальную точку и имеющей радиус, равней расстоянию от нее до центра координат.

Известен круговой интерполятор, содержащий регистры координат, сумматоры, логические , - вентильные схемы занесения Чиселi генератор тактовых импульсов (.ij .

Недостатком такого интерполятора является небольшая томность аппрокси мации, неравномерность линейной скорости подачи рабочего органе, что е конце концов влияет, например, на томность обработки деталей.

Наиболее близким техническим решением к изобретение является круговой интерполятор, содержащий регистры текущих координат, накопительные сумматоры, логический блок определения знака, тактовый генератор, вентильныб схемы занесения чисел ГзД .

К недостаткам известного устройства относятся значительная методическая погрешность аппроксимации, достигающая одного шага интерполяции, и неравномерность (достигающая 1, раза) линейной скорости подачи при Обработке детали,Кроме того, интерполятор может работать только в первом квад ранте (при положительных координатах X иу).

Целью изобретения является повушение точности и расширение области применения интерполятора.

ГЬэставленная цель достигается тем, в круговой интерполятор, содержащий первый накопительный сумматор, подключенный первыми информационными входами к выходам первого, второго и третьего блоков элементов И, соединенных первыми входами с соответствующими первы)и выходами логического блока, подключенного вторым выходом к сбросовому входу первого накопительного сумматора, третьими выходами - к первым входам .четвертого и пятого

блоков элементов И, первым входом к выходу генератора импульсов, третьим и четвертым выходами соответственно - к суммирующему и вычитающему выходам первого регистра, а пятым и шестым выходами соответственно - к суммирующему и вычитающему входам второго регистра, введены схема сравнения, два блока инверторов, комбинационный сумматор и второй накопительный сумматор,соединенный первыми информационными входами с выходами четвертого и пятого блока элементов И, вторым информационным входом и сбросовым входом соответственно - с четвертым и пятым выходами логического блока, а выходами - с вторыми входами первого блока элементов И и с первыми входами схемы сравнения, подключенной

0 вторыми входами к выходам первого накопительного сумматора и к вторым входам пятого блока элементов И, а выходом - к второму входу логического блока, связанного седьмым выходом с

управляющим входом первого блока инверторов, подключенного информационными Входами к выходам первого регистра, а выходами - к вторым входам третьего блока элементов И и к первым

0 входам комбинационного сумматора, соединенного знаковым выходом с третьим .входом логического блока, информационными выходами - с вторыми входами четвертого блока элементов И, а вторыми входами - с вторыми входами второго блока элементов И, с выходами второго блока инверторов связанного управляющим входом с восьмым выходом логического блока, а входами - с информационными выходами второго регистра, подключенного знаковым выходом к четвертому входу логического блока, соединенного пятым входом со знаковым выходом первого регистра, а шестым

5 входом - к шине Пуск, причем второй вход первого накопительного сумматора подключен к четвертому выходу логического блока.

Предложенная конструкция интерпо-

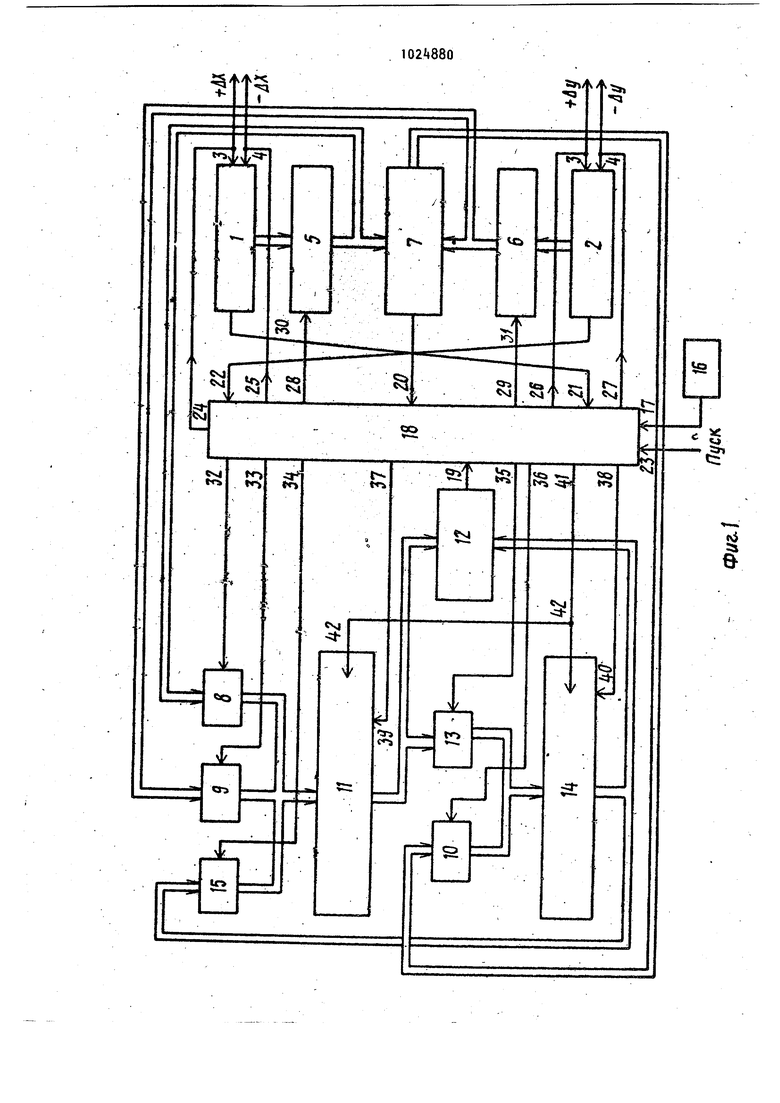

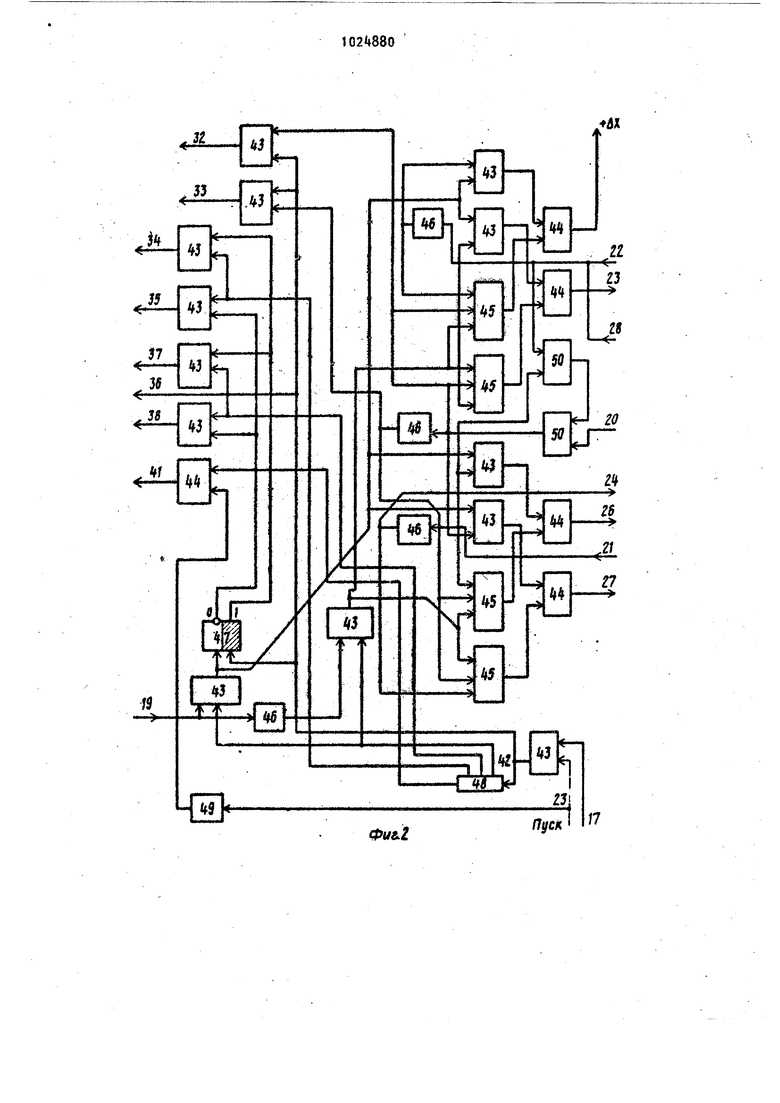

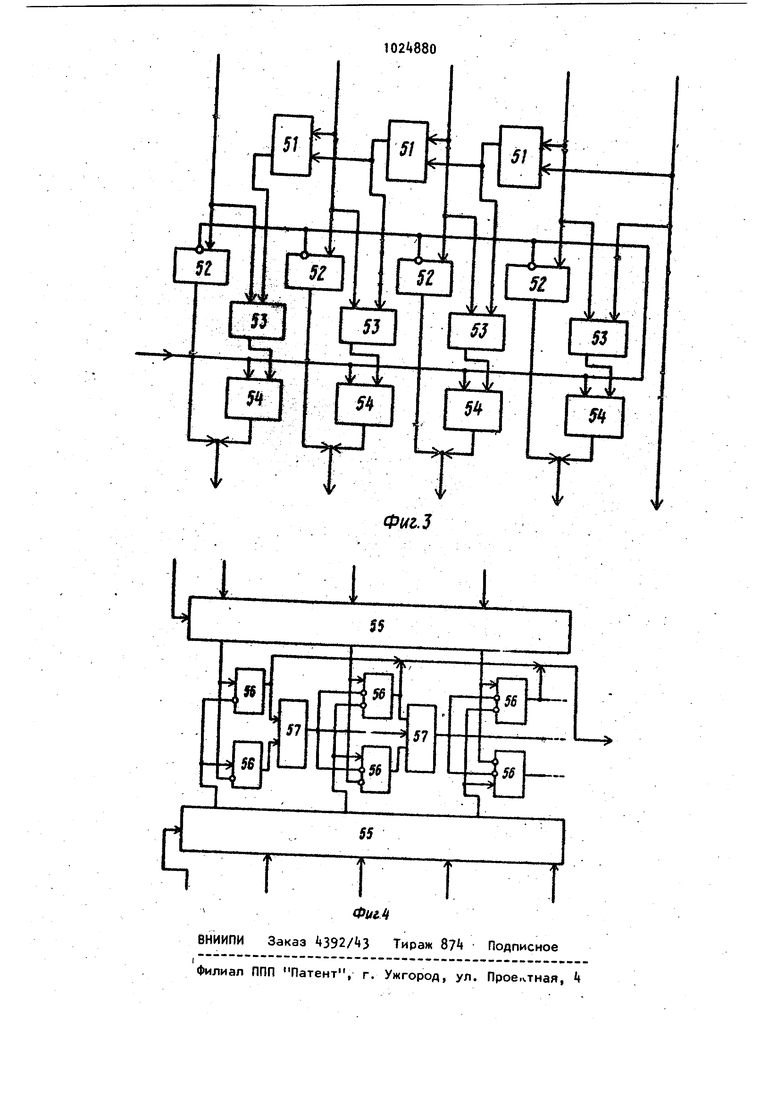

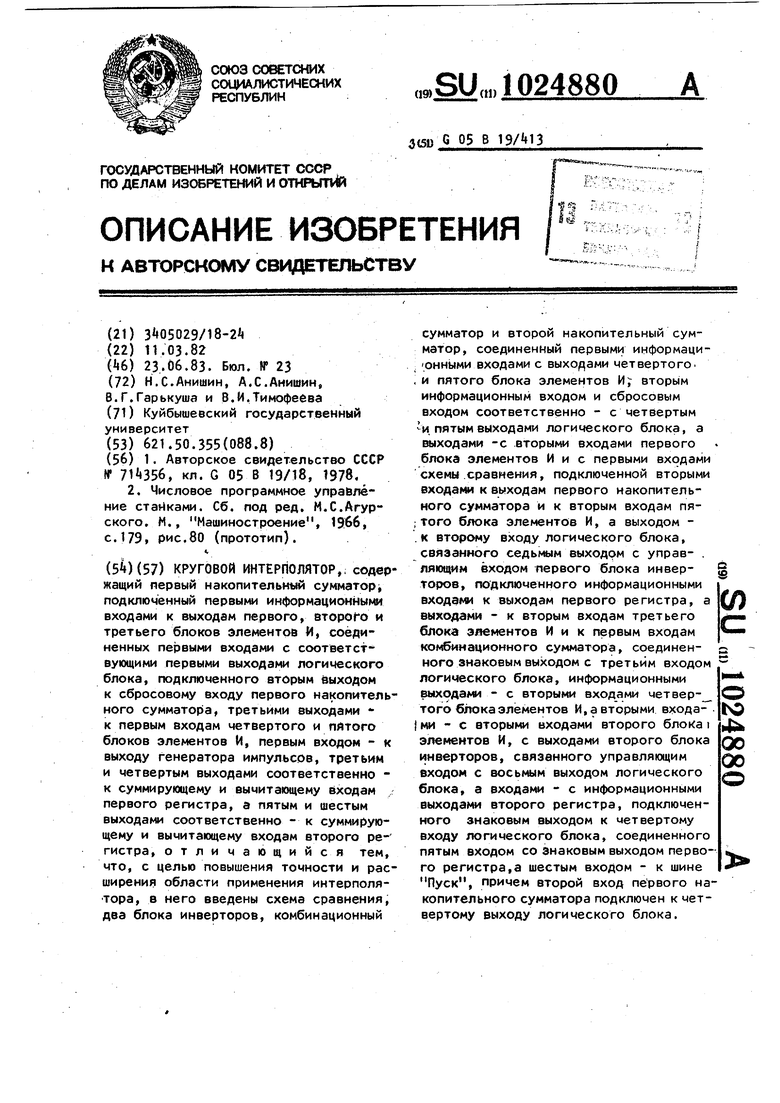

Q яятора обеспечивает его работу с выдачей координатных импульсов под каждый импульс генератора тактовых импульсов по координате, модуль величины которой меньше и оптимальное (в смысле минимума погрешности) раст пределение импульсов по -координате, модуль величины которой больше. Логический блок осуществляет слежение за разностью модулей отклонения двух прогнозируемых ности (одно из ным движением по одной координате, другое -по двум,т.е. по диагонали), получаемой на выходе схемы сравнения и, выбрав меньше из них, задает движен в одно из двух положений, т.е. либо выдает импульс по .одной, либо - импульсы по обеим координатам (по диагонали). На фиг.1 дана структурная схема интерполятора; на фиг.2 - k - соответственно блок-схемы логического блока, блока инверторов и схемы срав нения . Круговой интерполятор содержит пе вый и второй регистры., 1 и 2, суммирую щие входы. 3 первого и второго регистров, вычитающие входы k первого и второго регистров, первый и второй блоки инверторов 5 и 6, комбинационный, сумматор 7,третий блок э 1ементов И 8, второй блок элементов И 9, четвертый блок элементов И 10, первый накопительный сумматор 11, схему срав нения 12.пятый блок элементов И 13, второй накопительный сумматор первый блок элементов И 15 генератор импульсов 16, первый вход 17 логического блока, логический блок 18, второй, третий, пятый, четвертый, шестой входы 19-23 логического блока, первый, шестой, седьмой, восьмой выходы логического блока, управляющие входы 30 и 31 первого и второго блока инверторов; первые выходы 32-З логического блока; третьи выходы 35 и 36 логического блока; второй выход 37 ло гического блока, пятый выход 3.8 логического блока, сбросовые входы 39 и t первого и второго накопительных сумма торов; четвертый выход 1 логического блока, вторые входы 2, первого и второго накопительных сумматоров. Логический блок 18 содержит первые (двухвходовые) элементы И 3, первые элементы ИЛИ 44, вторые (трехвходовые) элементы И 45, элементы НЕ 46, RSтриггер 47, линию временной задержки 48, дифференцирующую цепь 48, схемы СЛОЖЕНИЕ riO МОДУЛО ДВА 50. Волоки инверторов 5 и 6 содержат вторые (двух входовые) эле.менты ИЛИ 51, элементы ЗАПРЕТ 52, схемы СЛОЖЕНИЕ ПО МОДУШ ДВА 53 третьи элементы И 54, Схема сравнения 12 содержит два инвертора 55 четвертые элементы .И 56, третьи элементы ИЛИ 57. 3}02kQSO4 положений от окруж- Выходы второго и третьего блоков них связано с возмож- элементов И 9 и 8, объединяясь поразрядно, связаны с входами первого (п+1)-разрядного накопительного сумматора 11, выход которого поступает на второй вход схемы сравнения 12 и через ()-разрядный блок элементов И 13, объединяясь старшими разрядами с выходами п-разрядного блока элементов И 10, поступают на вход второго (n+V)-разрядного накопительного сумматора Т, выход которого соединен с первым входом схемы сравнения 12, и через (п+Поразрядный блок элементов И 15 на вход сумматора 11, Интерполятор работает следующим образом. В исходном состоянии накопительные сумматоры И и I сброшены в О, а в регистры t и 2 занесены координаты начала круговой траектории (относительно центра круга). По сигналу Пуск, поступающему на вход 23 логического блока 18, высокий потенциал, дифференцируясь с помощью цепочки 49, через элемент ИЛИ и выход производит установку в состояние 4V и +2 накопительных сумматоров 11 и 1 соответственно. Очередной импульс от тактового генератора 16,пройдя открытый элемент И 43, поступает на вход линии задержки 48 и, пройдя на вход R триггера 47, устанавливает его в О. Кроме того, . он проходит на вход Зб и разрешает перепись числа с выхода комбинационного сумматора 7, равного разности модулей координат ±(х) и +(у) с теми или иными знаками, задаваемыми блоками инверторов (знака) 5 и 6 в зависимости от квадранта, через блок элементов И 10 на подсуммирование накопительным сумматором 14. Причем под- . суммирование производится со сдвигом/ на один разряд влево, т.е. фактически подсуммируется величина 2(+/х/+/у/). Кроме того,этим же сигналом с выхода элемента И 43 в накопительный сумматор 11 через блоки элементов И 9 или 8 подсуммируется 2х или 2у в зависимости от того, что больше по модулю у или X. Это определяется 1-й и 2-й логическими схемами СЛОЖЕНИЕ ПО МОДУШ ДВА 50, входами которых являются знак X, знак у и знак их разности, снимаемые через входы 21, 22 и 20 логического блока 18 с регистров I и 2 и комбинационного сумматора 7. В зависимости от сигнала на выходе 2-й схемы 50 открывается либо один, либо другой логический элемент 3, которые и пропускают сигнал На выход 32 или 33. Они соединены с синхровходами (п-разрядных) блоков элементов И 9 и 8; пропускающих числа на вход накопительного сумматора 11. Установившиеся после суммирования значения с сумматоров 11 и И подаются на вход схемы сравнения 12, которая сравнивает содержимое обоих сумма торов по модулю и выдает сигнал 1 если содержимое первого сумматора больше содержимого второго сумматора fi. Этот сигнал поступает через вход 19 в логический блок 18 -через соответствующий логический элемент стробируемый сигналом с первого промежуточного выхода линии задержки, на запуск логических элементов, формирующих приращение ±дх и +йу, которые поступают через выходы 24-2 на вход увеличения или уменьшения текущих значений координат, содержащихся в регистрах 1 и 2., Эти сигналы приращений являются выходами интерполятора. Кроме того, сигнал с выхода логического элемента И поступает на вход триггера kj, где он запоминается на время одного такта. Сигнал с второго промежуточного Ехода линии задержки обеспечивает через выход 37 или 38 сброс 6 О того накопительного сумматора (из 11 и И), модуль числа в котором больше. Это делается с помощью соответствующих элементов И 13, управляемых выходами триггера, запомнившего соотношение этих значений в данном такте. Сигнал с третьего прокйжуточного выхода линии задержки tS с помощью соответствующих элементов И 13 обеспечивает занесение меньшего числа од.ного из сумматоров в другой, который перед этим был сброиен в О. Это выполняется под управлением триггера if. Выходной сигнал с линии задержки kB через логический элемент ИЛИ до бавляет через выход il и входы k2 cy маторов 1 к значению первого суммэтора 11 и 2 - второго сумматора I. Величина линии задержки 48 должна быть выбрана не больше периода тактовых импульсов генератора 1б за вычетом времени,,необходимого на одно подсуммирование числа к сумматору 11 и Vt. Интерполятор может быть реализован на интегральных микросхемах, а также на МИС или СИС. В основу алгоритма цифрового кругового интерполятора положен принцип движения либо по диагонали (т.е. им-, пульсы есть по обеим координатам), если меньшее по модулю число находится во втором накопительном сумматоре И, Либо по координате, модуль величины которой меньше (т.е. импульс есть только по этой координате, если меньшее число по модулю находится на первом сумматоре 11. Числа, находящиеся в сумматорах, пропорциональны прогнозируемым отклонениям траектории, от окружности при двух возможных продолжениях движения (по диагонали или вдоль одной из координат). Так происходит на каждом такте вплоть до такта, когда текущие координаты достигнут конечных значений, jзадаваемых извне. Элементы этого сравнения на фиг.1 не показаны. Благодаря применению вновь введенных блоков (сумматоры, инверторы знака, схема сравнения) снижена методическая погр ешность вдвое, она не более 0,5 шага интерполяции, коэффициент неравномерности снижен с I, до 1,12 (т.е. С/Тдо лГ5/2). Кроме того, предлагаемый интерполятор может работать в любом квадранте, т.е. при любых знаках текущих координат, в том числе и переходя из квадранта в квадрант. Методическая (а том числе и максимальная) погрешность снижена в два раза. Это позволяет, например, выбрать шаг вдвое больше и, таким образом, ускорить процесс интерполяции без какого-либо ухудшения качества обработки или изображения. Более равномерное поступление импульсов, а соответственно и более равномерная скорость обработки позволяет отказаться от дополнительных узлов модуляции яркости луча ЭЛТ, улучшает динамические характеристики систем программного управления. Улучшает также качество изображения на экране ЭЛТ за счет лучших динамических свойств интерполятора.

П

Пуси

Фи&2

| название | год | авторы | номер документа |

|---|---|---|---|

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Цифровой интерполятор | 1983 |

|

SU1140098A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

КРУГОВОЙ ИНТЕРПОЛЯТОР,, содержащий первый накопительный сумматор подключенный первыми информационйыкм входами к выходам первого, второго и третьего блоков элементов И, соединенных пе{эвыми входами с соответствующими первыми выходами логического блока, подключенного вторым выходом к сбросовому входу первого накопительного сумматора, третьими выходами к первым входам четвертого и питого блоков элементов И, первым входом - к выходу генератора импульсов, третьим и четвертым выходами соответственно к суммирующему и вычитающему входам / первого регистра, а пятым и шестым выходами соответственно - к суммирующему и вычитающему входам второго регистра, отли чающийся тем, что, с целью повышения точности и расширения области применения интерполятора, в него введены схема сравнения, два блока инверторов, комбинационный сумматор и второй накопительный сумматор, соединенный первыми ииформаци. юнными входами с выходами четвертого. , и пятого блока элементов И; вторым информационным входом и сбросовым входом соответственно - с четвертым ц пятым выходами логического блока, а выходами -с вторыми входами первого блока элементов И и с первыми входами схемы .сравнения, подключенной вторыми входами к выходам первого накопительного сумматора и к вторым входам пя,того блока элементов И, а выходом .к второму входу логического блока, связанного седьмым выходам с управ- . ляющим входом первого блока инверS торов, подключенного информационными входами к выходам первого регистра, а выходами - к вторым входам третьего блока элементов И и к первым входам комбинационного сумматора, соединенного знаковым выходом с третьим входом логического блока, информационными выхода 1 - с вторыми входами четвер- Ю того блока элементов И, а вторыми входаj ми - с вторыми входами второго блока i 4 элементов И, с выходами второго блока 00 00 инверторов, связанного управляющим входом с восьмым выходом логического блока, а входами - с информационными выходами второго регистра, подключенного знаковым выходом к четвертому входу логического блока, соединенного пятым входом со знаковым выходом первого регистра,а шестым входом - к шине Пуск, причем второй вход первого накопительного сумматора подключен к четвертому выходу логического блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Числовое программное управление стайками | |||

| Сб | |||

| под ред | |||

| М.С.Агурского | |||

| М., Машиностроение, 1966, с.179, рис.80 (прототип) | |||

Авторы

Даты

1983-06-23—Публикация

1982-03-11—Подача