1

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам отображения графической информации на экране электроннолучевой трубки (ЭЛТ) или на графопостроителе, а также программного управления металлорежущими станками.

Известен цифровой линейный интерполятор l.

Недостатком является неравномерность распределения импульсов во времени и то, что быстродействие интерполятора по сравнению с его тактовой частотой на некоторых кодах уменьшается вдвое. Это приводит к тому, что скорость отработки луча ЭЛТ будет заниженной, соответственно время построения - завышенным, и отклонение фактической траектории луча от требуемой прямой линии, определяемое нерегулярностью импульсов в последовательностях по обеим координатам, может быть значительным (большим величи

ны одного шага интерполяции по координате) .

Кроме того, время отработки луча ЭЛТ различных координатных приращений у этих интерполяторов не прямо пропорционально величине этих приращений, что приводит (в силу зависимости яркости изображения от скорости перемещения луча по экрану к неравномерности свечения отдельных участков кривых (одни участки будут ярче других) . В случае станков с программным управлением неравномерность следования импульсов дополнительно увеличивает динамическую ошибку отработки траектории рабочего органа.

Наиболее близким техническим решением к изобретению является цифровой линейный интерполятор, содержащий регистры приращений, накапливающие сумматоры, логические схемы, генератор тактовых импульсов 2.

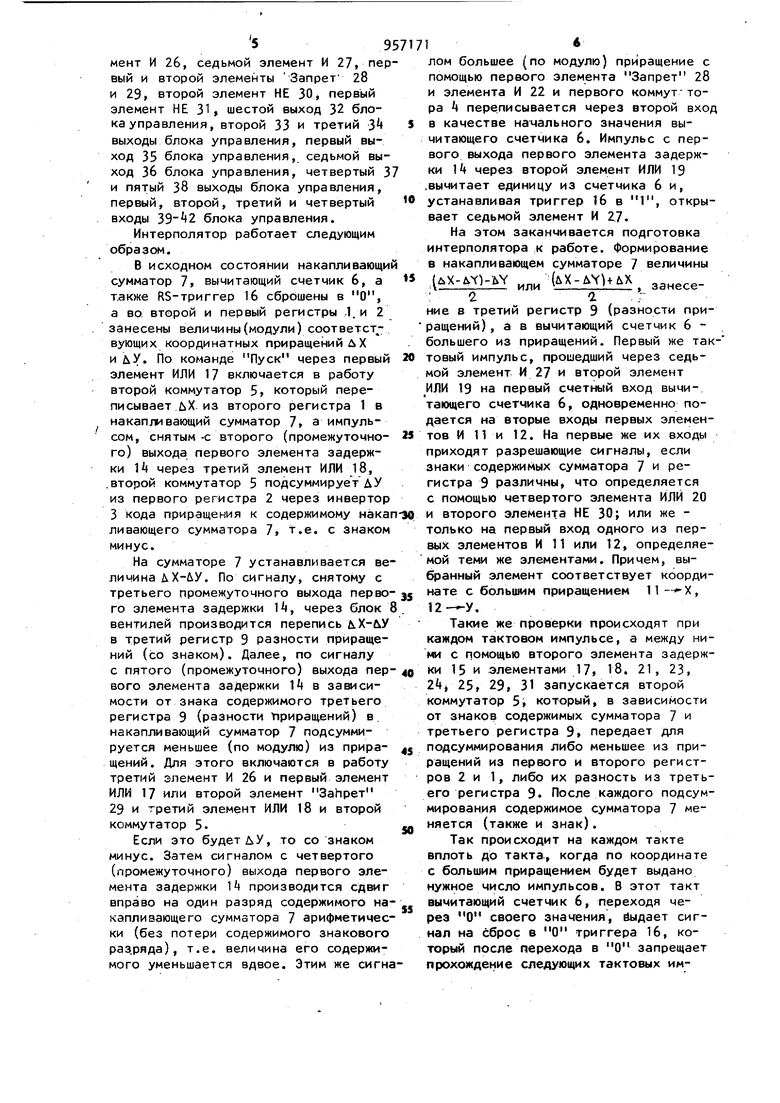

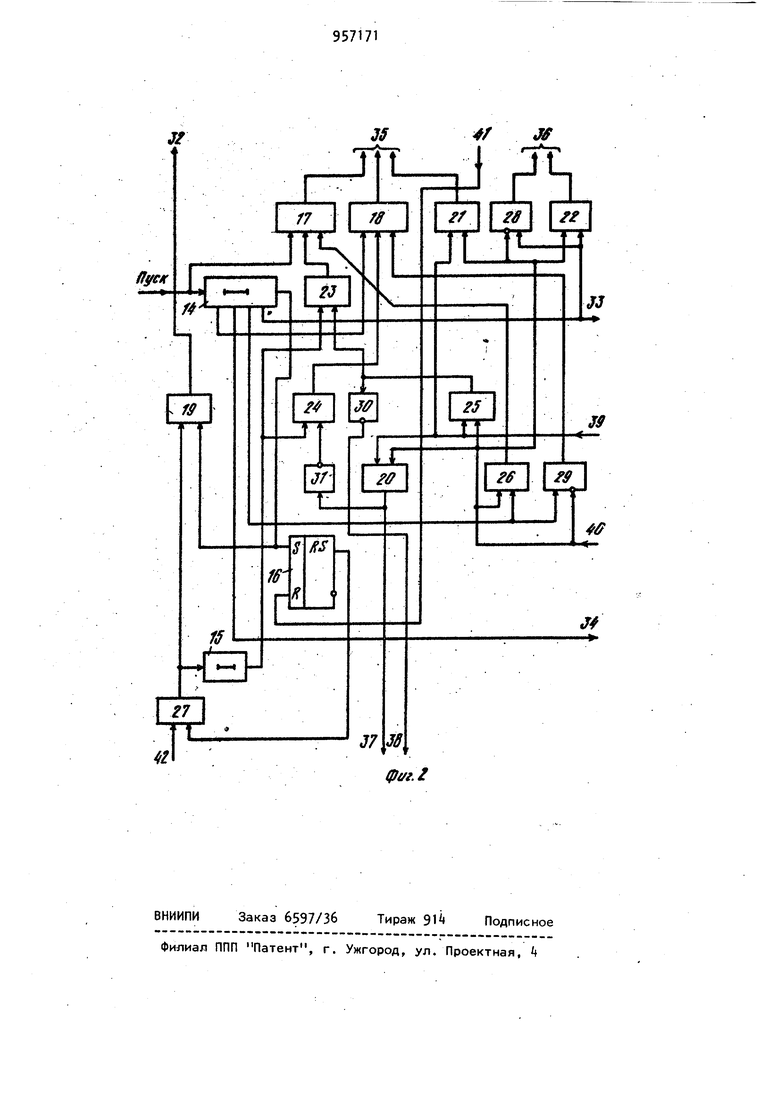

К недостаткам известного устройства относится высокая методическая погрешность, достигающая величины од ного шага интерполяции по координате и низкое быстродействие. Целью изобретения является повышение точности и быстродействия интерполятора. Поставленная цель достигается тем что в цифровой линейный интерполятор, содержащий первый и второй регистры, два первых элемента И, генератор импульсов и накапливающий сумматор, введены два коммутатора, вычитающий счетчик, блок вентилей, бло управления и инвертор, соединенный входом с выходом первого регистра и с первым входом первого коммутатора, подключенного вторым входом к выходу второго регистра и к первому входу второго коммутатора, связанного вторым входом с выходом инвертора, TpeT им входом - с первым выходом третьег регистра, четвертым входом с первым выходом блока управления, а выходом с первым входом накапливающего сумматора, подключенного вторым входом и первым выходом соответственно к второму выходу и к первому входу бло ка управления, а вторым выходом - к первому входу блока вентилей, соединенного вторым входом с третьим выходом блока управления, а выходом с входом третьего регистра, подключенного вторым выходом к второму вхо ду блока управления, связанного, четвертым и пятым выходами соответствен но с первыми входами первых элементов И, подключенных вторыми входами к шестому выходу блока управления и к первому входу коммутатора, связанного вторым входом с выходом первого коммутатора, подключенного выходом к третьему входу блока управления, соединенного седьмым выходом и четвертым входом соответственно с треть им входом первого коммутатора и с выходом генератора импульсов. Кроме того, блок управления содер жит первый элемент задержки, подключенный входом через первый элемент ИЛИ к первому выходу блока управления , первым выходом - к S- входу RS-триггера и через второй элемент ИЛИ к шестому выходу блока управления, вторым выходом через третий эле мент ИЛИ к первому выходу блока упра ления , третьим выходом к третьему выходу блока управления, четвертым выходом к второму выходу блока управления и через второй элемент И и первый элемент Запрет.к седьмому вы-г ходу блока управления, а пятым выходом к первым входам третьего элемента И и второго элемента Запрет, связанных выходами с вторыми входами соответственно первого и третьего элементов ИЛИ, а вторыми входами с вторым входом блока управления, с первыми входами четвертого элемента ИЛИ и четвертого элемента И, с вторыми входами первого элемента Запрет и второго элемента И и с первым входом элемента Неэквивалентность, подключенного выходом к первому выходу блока управления, а вторым входом к первому входу блока управления, к второМу входу четвертого элемента И и четвертого к второму входу четвертого ИЛИ, соединенного выходом с четвертым выходом блока управления и с входом первого элемента НЕ, подключенного выходом к первому входу пятого элемента И, связанного выходом с третьим входом третьего элемента ИЛИ, а вторым входом через шестой элемент И - с трет1 им входом первого элемента ИЛИ и через второй элемент Задержки - с вторым входом второго элемента ИЛИ и выходом седьмого элемента И, подключенного первым входом к четвертому входу блока управления, а вторым входом - к прямому выходу RS-триггера, соединенного R-входом с третьим входом блока управления, причем пятый выход блока управления подключен к выходу второго элемента НЕ, соединенного входом с выходом четвертого элемента И и вторым входом шестого элемента И. На фиг. 1 изображена рхема предлагаемого интерполятора; на фиг. 2 схема блока управления. Интерполятор содержит второй регистр 1, первый регистр 2, инвертор 3, первый k и второй 5 коммутаторы, вычитающий счет ик 6, накапливающий сумматор 7 блок 8 вентилей, третий регистр 9 генератор 10 импульсов, первые элементы И 11 и 12, блок 13 управления. Блок 13 управления содержит первый 14 и второй 15 элементы задержки, RS-триггер 16, первый элемент ИЛИ 17, третий элемент ИЛИ 18, второй элемент ИЛИ 19 четвертый элемент ИЛИ 20, элемент Неэквивалентность 21, второй элемент И 22, шестой элемент И 23, пятый элемент И 24, четвертый элемент И 25, третий элемент И 26, седьмой элемент И 27, пер вый и второй элементы Запрет 28 и 29 второй элемент НЕ 30, первый элемент НЕ 31, шестой выход 32 блока управления, второй 33 и третий З выходы блока управления, первый выход 35 блока управления, седьмой выход 36 блока управления, четвертый 3 и пятый 38 выходы блока управления, первый, второй, третий и четвертый входы блока управления. Интерполятор работает следующим образом. В исходном состоянии накапливающи сумматор 7, вычитающий счетчик 6, а также RS-триггер 16 сброшены в О, а во второй и первый регистры .1. и 2 занесены вел и чины (модули) соответст;вующих координатных приращений ДХ и . По команде Пуск через первый элемент ИЛИ 17 включается в работу второй коммутатор 5 который переписывает Х из второго регистра 1 в накапливающий сумматор 7, а импульсом, снятым -с второго (промежуточного) выхода первого элемента задержки Н через третий элемент ИЛИ 18, .второй коммутатор 5 подсуммирует АУ из первого регистра 2 через инвертор 3 кода приращения к содержимому нака ливающего сумматора 7, т.е. с знаком минус. На сумматоре 7 устанавливается ве лимина АХ-&У. По сигналу, снятому с третьего промежуточного выхода перво го элемента задержки 1, через блок вентилей производится перепись й. в третий регистр 9 разности приращений (со знаком). Далее, по сигналу с пятого (промежуточного) выхода пер вого элемента задержки }k в зависимости от знака содержимого третьего регистра 9 (разности 11риращений) в. накапливающий сумматор 7 подсуммирует ся меньшее (по модулю) из приращений. Для этого включаются в работу третий элемент И 2б и первый элемент ИЛИ 17 или второй элемент ЗаЬрет 29 и третий элемент ИЛИ 18 и второй коммутатор 5. Если это будетЛУ, то со знаком минус. Затем сигналом с четвертого (промежуточного) выхода первого элемента задержки производится сдвиг вправо на один разряд содержимого на капливающего сумматора 7 арифметичес ки (без потери содержимого знакового раз.ряда), т.е. величина его содержимого уменьшается вдвое. Этим же сигна лом большее (по модулю) приращение с помощью первого элемента Запрет 28 и элемента И 22 и первого коммут тора k переписывается через второй вход в качестве начального значения вычитающего счетчика 6. Импульс с первого выхода первого элемента задержки 1 через второй элемент ИЛИ 19 .вычитает единицу из счетчика 6 и, устанавливая триггер 16 в 1, открывает седьмой элемент И Z7. На этом заканчивается подготовка интерполятора к работе. Формирование в накапливающем сумматоре 7 величины i/.x-4X) „. (&х-лчи х ....... : 2 1 ние в третий регистр 9 (разности приращений), а в вычитающий счетчик 6 большего из приращений. Первый же тактовый импульс, прошедший через седьмой элемент И 27 и второй элемент ИЛИ 19 на первый счетный вход вычитающего счетчика 6, одновременно подается на вторые входы первых элементов И 11 и 12. На первые же их входы приходят разрешающие сигналы, если знаки содержимых сумматора 7 и регистра 9 различны, что определяется с помощью четвертого элемента ИЛИ 20 и второго элемента НЕ 30; или же только на первый вход одного из первых элементов И П или 12, определяемой теми же элементами. Причем, выбранный элемент соответствует координате с большим приращением , 12--У. Такие же проверки происходят при каждом тактовом импульсе, а между ними с помощью второго элемента задерж 5 и элементами 17, 18. 21, 23, 2 25, 29, 31 запускается второй коммутатор 5, который, в зависимости от знаков содержимых сумматора 7 и третьего регистра 9, передает для подсуммирования либо меньшее из приращений из первого и второго регистров 2 и 1, либо их разность из третьего регистра 9. После каждого подсуммирования содержимое сумматора 7 меняется (также и знак). Так происходит на каждом такте вплоть до такта, когда по координате с большим приращением будет выдано нужное число импульсов. В этот такт вычитающий счетчик 6, переходя через О своего значения, Ёыдает сигнал на сброс в О триггера 16, который после перехода в О запрещает прохождение следующих тактовых импульсов через седьмой элемент И 27 и таким образом прекращает работу блока 13 управления и всего интерполятора в целом. Этот же сигнал о переполнении вычитающего счетчика 6 выдается в качестве сигнала Конец интерполяции. Применением вновь введенных блоков в состав интepпoлiRTOpa и связей между ними и остальными блоками получено быстродействие интерполятора совпадающее с частотой генератора тактовых импульсов, что примерно в 2 раза выше, чем в известных интерполяторов. Это позволяет ускорить по строение графиков на ЭЛТ (и в частности, отказаться от дорогостоящих ЭЛТ с запоминающим экраном и заменить их на более дешевые кинескопы) Максимальная методическая погрешность снижена также.в 2 раза. Это позволяет, например, выбрать шаг вдвое большим и, таким образом, ускорить построение графиков без какого-либо ухудшения качестве изображения. Равномерное поступление импульсов по координатам позволяет отказаться от дополнительных узлов модуляции яркости луча ЭЛТ в зависимости от величин приращений, улучшает динамические характеристики систем программного управления. Улучшается также качество изображения на экране ЭЛТ за счет лучших динамических свойств интерполятора. Формула изобретения 1 . Цифровой линейный интерполятор, содержащий первый и второй регистры два первых элемента И, генератор им пульсов и накапливающий сумматор, отли чающий ся тем, что с целью повышения точности и быстро действия интерполятора, в него введ ны два коммутатора, вычитающий счет чик, блок вентилей, блок управления и инвертор соединенный входом с выходом первого регистра и с первым входом первого коммутатора, подключенного вторым входом к выходу второ го регистра и к первому входу второго коммутатора, связанного вторым вх дом с выходом инвертора, третьим вхо дом - с первым выходом третьего регистра, четвертым входом с первым вы ходом блока управления, а выходом с первым входом накапливающего сумматора, подключенного вторым входом и первым выходом соответственно к второму выходу и к первому входу блока управления, а вторым выходом - к первому входу блока вентилей, соединенного вторым входом с третьим выходом блока управления, а выходом с входом третьего регистра, подключенного вторым выходом к второму входу блока управления, связанного четвертым и пятым выходами соответственно с первыми входами первых элементов И, подключенных вторыми входами к шестому выходу блока управления и к первому входу коммутатора, связанного вторым входом с выходом первого коммутатора, подключенного выходом к третьему входу блока управления, соединенного седьмым выходом и четвертым входом соответственно с третьим входом первого коммутатора и с выходом генератора импульсов. 2. Устройство по п. 1, о т л и чающееся тем, что блок управления содержит первый элемент задержки, подключенный входом через первый элемент ИЛИ к первому входу блока управления, первым выходом - к S-входу RS-триггера и через второй элемент ИЛИ к шестому выходу блока управления, вторым выходом через третий элемент ИЛИ к первому выходу блока управления, третьим выходом к третьему выходу блока управления, четвертым выходом к второму выходу блока управления и через второй элемент И и первый элемент Запрет к седьмому выходу блока управления, а пятым выходом к первым входам третьего эле-, мента И и второго элемента Запрет- , связанных выходами с вторыми входами соответственно первого и третьего элементов ИЛИ, а вторыми входами с вторым входом блока управления, с первыми входами четвертого элемента ИЛИ и четвертого элемента И, с вторыми входами первого элемента Запрет и второго элемента И и с первым входом элемента Неэквивалентность, подключенного выходом к первому выходу блока управления, а вторым входом - к первому входу блока управления, к второму входу четвертого элемента И и к второму входу четвертого элемента ИЛИ, соединенного выходом с четвертым выходом блока управления и с входом первого элемента НЕ, подключенного выходом

95

к первому входу пятого элемента И, связанного выходом с третьим входом третьего элемента ИЛИ, а вторым входом через шестой элемент И - с третьим входом первого элемента ИЛИ и через второй элемент Задержки - с вторым входом второго элемента ИЛИ и выходом седьмого элемента И, подключенного первым входом к четвертому входу блока управления, а вторым входом - к прямому выходу RS-триггера, соединенного R-входом с третьим входом блока управления, причем пятый выход блока управления подклю7110

чен к выходу второго элемента НЕ,

I соединенного входом с выходом четвертого элемента И и с вторым входом шестого элемента И.

Источники информации, принятые во внимание при экспертизе

1.Основы построения устройства оперативного вывода информации. Под ред. М.С. Безродного. М., Энергия 1973, с. 65-66.

2.Авторское свидетельство СССР № 600569, кл. G 06 G 7/30, 1975 (прототип).

J/

4f Jff

| название | год | авторы | номер документа |

|---|---|---|---|

| Круговой интерполятор | 1982 |

|

SU1024880A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Цифровой интерполятор | 1983 |

|

SU1140098A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1462247A1 |

| Круговой интерполятор | 1989 |

|

SU1665343A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Интерполятор | 1986 |

|

SU1401481A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

41

ф1/г.2

Авторы

Даты

1982-09-07—Публикация

1981-03-25—Подача