вертого третьего эпементов И соединены с выходомэлементов - с третьими выходами блока упэлемента эадержки, а выходы этихравнения. 1140098

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

1. ЦИФРОВОЙ ИНТЕРПОЛЯТОР, содержащий блок управления, блок вычис:Ления разности и последовательно соединенные счетчики текущих координат, первый коммутатор и первый накапливающий сум- матор, второй вход которого подключен к первому входу цифрового интерполятора, а выход - к первому входу блока управления, соединенного первым выходом с управляющим входом первого коммутатора, а вторым - с первыми входами счетчиков текущих координат и выходом цифрового интерполятора, выходы счетчиков текущих координат через блок вычисления разности подключены к третьему входу первого коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей путем о6еспе юния 1шфровой эллиптической ин терполяцин устройства, в него введены первый и второй регистры, второй коммутатор, второй накапливающий сумматор и элемент И, выход которого соединен с вторым выходом цифрового интерполятора, а второй вход - с. вторым выходом блока управления, выход второго накапливающего сумматора подключен к второму входу блока управления, третий выход которого соеданен с первым входом второго коммутатора, второй и третий входы которого соединены с выходами первого и второго регистров, а третьи входы блока управления являются вторыми входами цифрового интерполятора, третьи входы которого соединены с входами первого и второго регистров, четвертый вход соединен со вторым входом второго т акапливающего сумматора, а пятые в-оды - с вторыми входами счетчиков текуп11 х координат. 2. Интерполятор по п. 1, о т л и ч а ю щ и и с я тем, что блок управления содержит генератор импульсов, два переключателя, три элемента задержки, RS -триггер, элемент НЕ ,четыре элемента И и элемент ИЛИ, первый вход которого соедине с вторым входом блока и через первый элемент задержки с S входом RS триггера, R -вход которого подключен к ъторому входу блока управления, а прямой выход - к первым входам первого и второго элементов И, вторые входы которых соединены с выходом генератора импульсов, а третьи входы - через первый переключатель с первым входом блока управления, выходы первого и второго элементов И подключены к второ. у выходу блока управления и через второй и третий элементы задержки и второй переключатель к первому выходу блока управления, второй «ыход второго переключателя соединен с вторым входом элемента ИЛИ, второй вход блока управления подключен к первому входу третьего элемента И и через элемент НЕ к перво.иу входу четвертого элемента И, вторые входы третьего и чет

1

Изобретение относится к автоматике и вычислительной технике и может быть применено в устройствах вывода графической информации, а также в системах числового программного управления оборудованием.

При машинном построении чертежей часто необходимо чертить аксонометрические и изометрические виды деталей, содержацдах круглые отверстия, валы, втулки и другие компоненты, имеюидие круглые и щшиндрические поверхности. Проекции этих деталей имеют эллиптические линии.

Эллиптические интерполяторы используются при обработке на станках с программным управлением эллиптических профилей и контуров.

Известны цифровые интерполяторы, содержащие накапливающие сумматоры, коммутаторы, счетчики, генераторы импульсов, логические схемы, блок управления, связанный с другими узлами и интерполятора .

Однако они интерполируют окружность, но не могут интерполировать эллипс. Кроме того, они имеют значительную методическую погрешность работы, вызванную особенностью алгоритмов, положенных в их основу (выбо очередного шага по знаку оценочной функции).

Наиболее близок к предлагаемому по технической сущности круговой интерполятор, содержащий накапливающий сумматор, входы и выходы которого соединены соответственно с выходом коммутатора, первым входом интерполятора и входом блока управления, соединенного своими выходами с первым входом коммутатора, выходами интерполятора и входами счетчиков, выходами подключенных к вторым входам интерполятора, выходы которых соединены с вторыми входами коммутатора. Интерполятор содержит блок вычисления разности, подключенный входами к выходам обоих счетчиков, а выходом - к третьему входу коммутатора. Его методическая погрешность в два раза меньше вышеупомянутых и составляет полшага интерполяции (2).

Однако известный интерполятор обладает ограниченными функциональными возможностями, в частности, он не может выполнять цифровую эллиптическую интерполяцию.

Цель изобретения - расширение функциональных возможностей путем обеспечения цифровой эллиптической интерполяции.

Поставленная цель достигается тем, что в .цифровой интерполятор, содержащий блок управления, блок вычисления разности и последовательно соединенные счетчики текущих координат, первый коммутатор и первый накапливающий сумматор, второй вход которого подключен к первому входу цифрового интерполятора, а выход - к первому входу блока управления, соединенного первым выходом с управляющим входом первого коммутатора, а вторым - с первыми входами счетчиков текущих координат и выходом цифрового интерполятора, выходы счетчиков текущих координат через блок вычисления разности подключены к третьему входу первого коммутатора, введены первый и второй регистры, второй коммутатор, второй накапливаюишй сумматор и элемент И, выход которого соединен с вторым выходом цифрового интерполятора, а второй вход - со вторым выходом блока управления, выход второго накапливающего сумматора подключен к второму входу блока управления, третий вь1ход которюй соединен с первым входом второго коммутатора, второй и третий входы которого соединены с выходами первого и второго регистров, а третьи входы блока упраления являются вторыми входами цифрового интерполятора, третьи входы которого соедииены со входами первого и второго регистров, четвертый вход соединен с вторым входом второго накапливающего сумматора, а пятые входы - со вторыми входами счетчиков текущих координат.

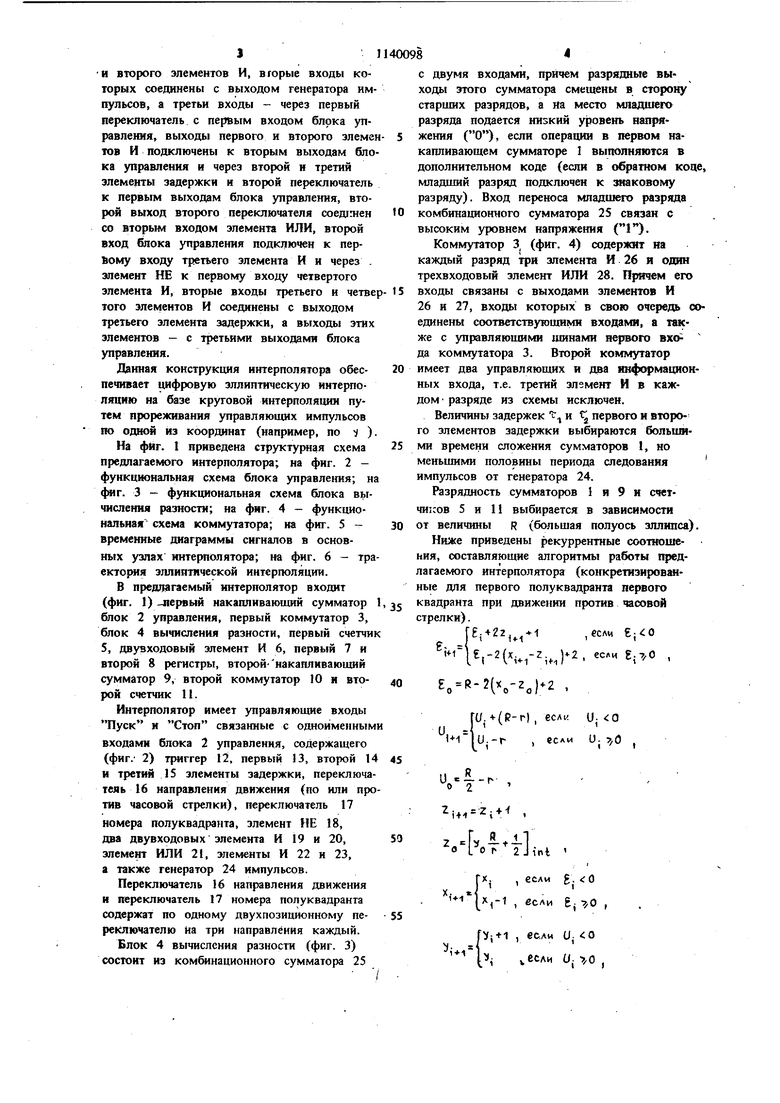

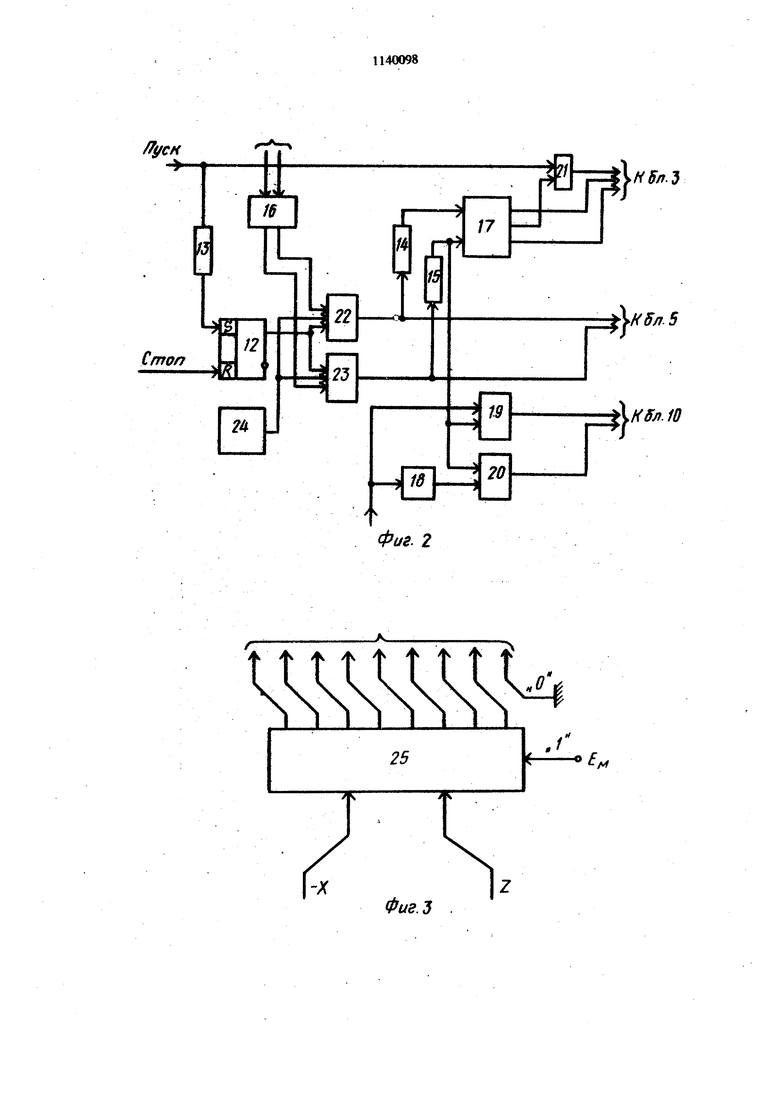

Блок управления содержит генератор импульсов, два переключателя, три элементазадержки, R5-триггер, четыре элемента И и элемент ИЛИ, первый вход которого соединен с вторым входом блока и через первый элемент эадержки с Э входом

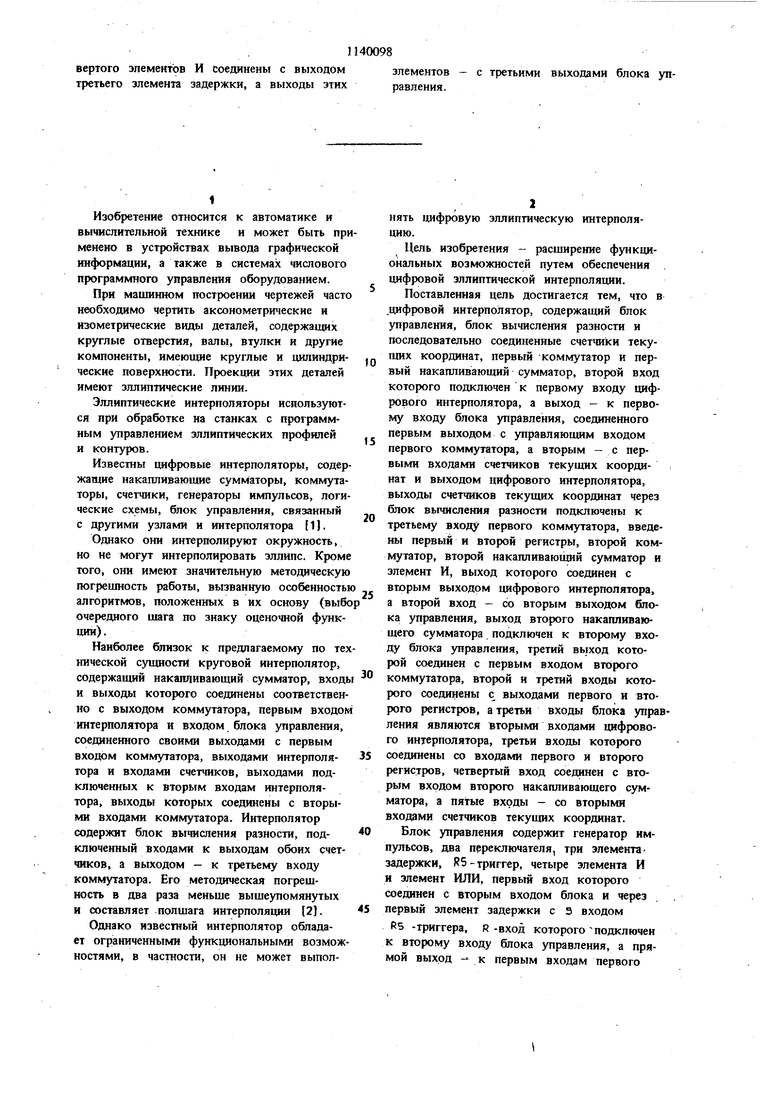

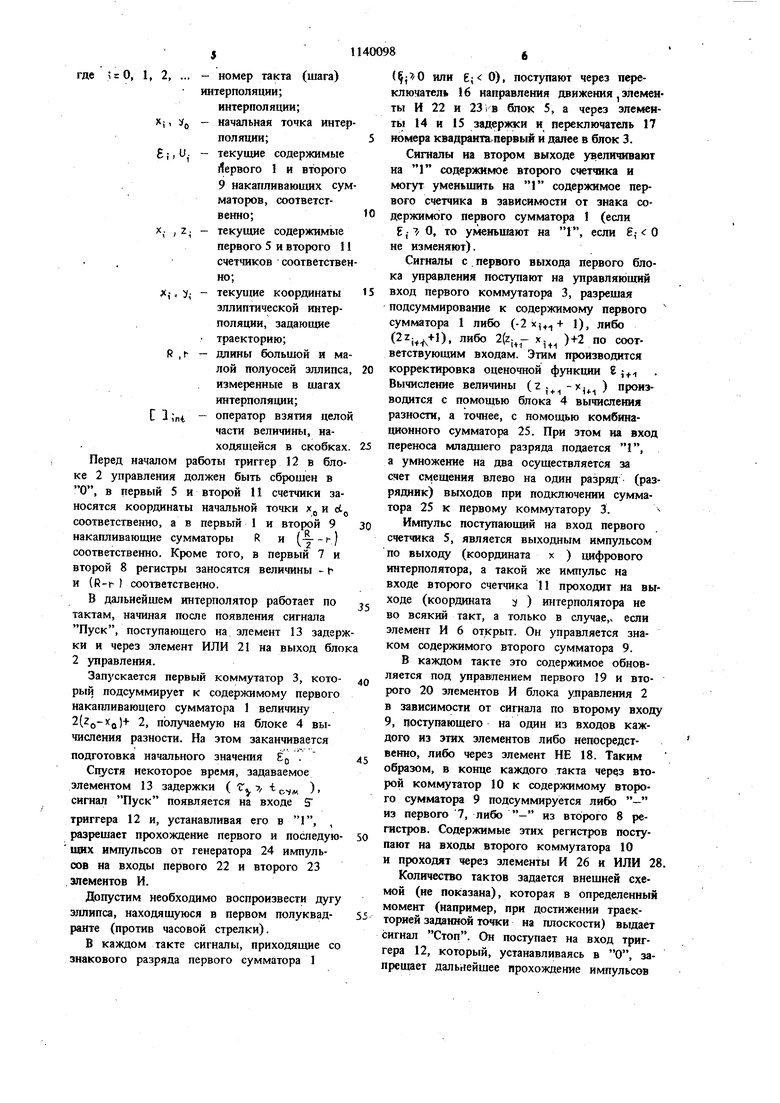

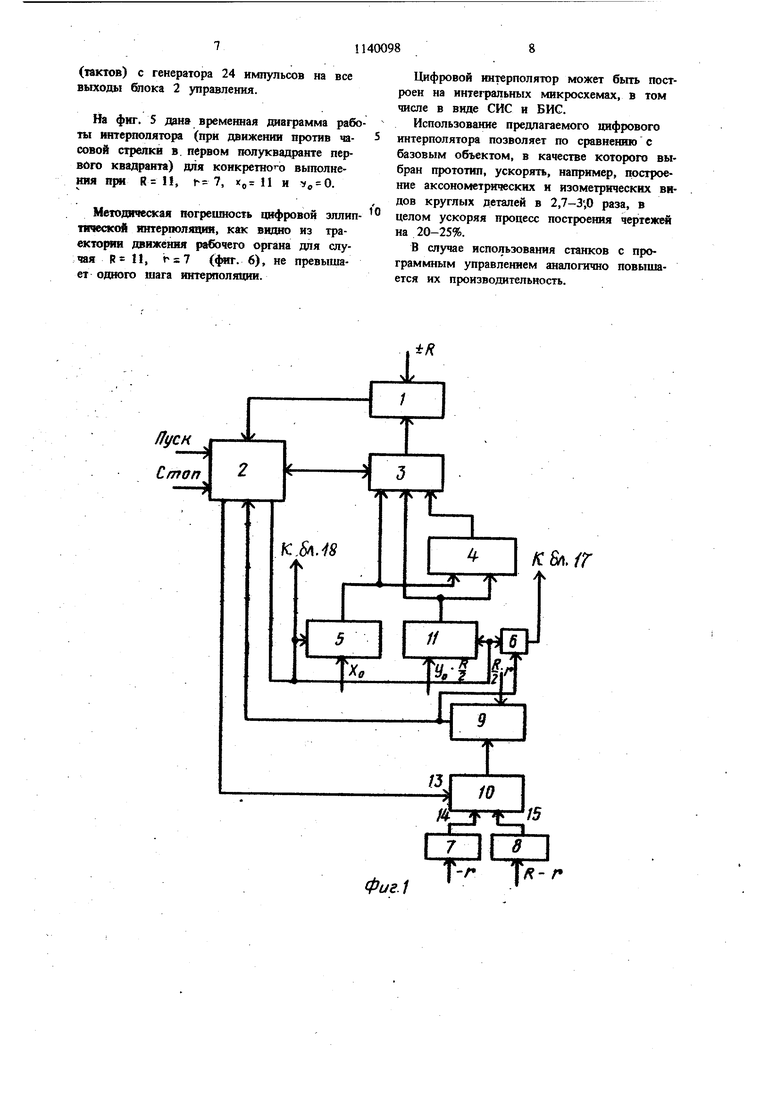

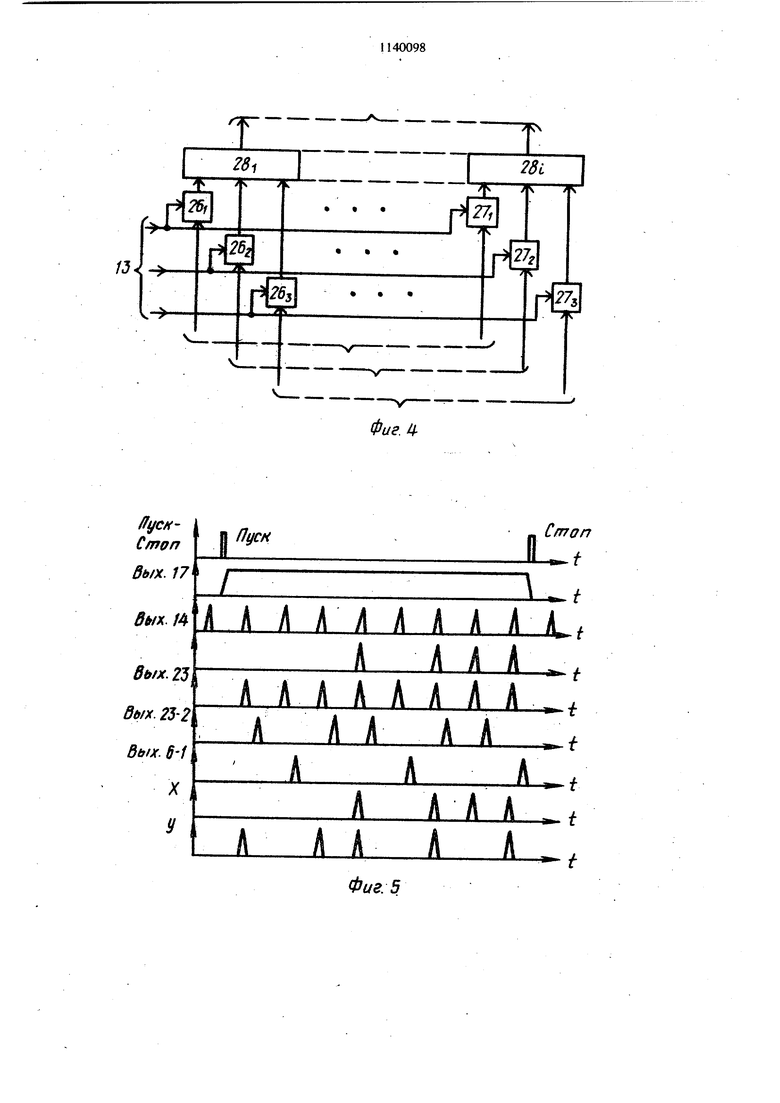

ft5 -триггера, R-вход которого подключен к второму входу блока управления, а прямой выход - к первым входам первого J и второго элементов И, вторые входы которых соеданены с выходом генератора импульсов, а третьи входы - через первый переключатель с первым входом блока управления, выходы первого и второго элеме тов И подключены к вторым выходам бло ка управления и через второй и третий элементы задержки и второй переключатель к первым выходам блока управления, второй выход второго переключателя соедтмен со вторым входом элемента ИЛИ, второй вход блока управления подключен к первому входу третьего элемента И и через . элемент НЕ к первому входу четвертого элемента И, вторые входы третьего и четве того элементов И соединены с выходом третьего элемента задержки, а выходы этих элементов - с третьими выходами блока управления. Данная конструкция интерполятора обеспечивает цифровую эллиптическую интерполяцию на базе круговой интерполяции путем прореживания управляющих импульсов по одной из координат (например, по ч ) На фиг. 1 приведена структурная схема предлагаемого интерполятора; на фиг. 2 функциональная схема блока управле1шя; н фиг. 3 - функциональная схема блока вьгчисления разности; на фиг. 4 - функциональная схема коммутатора; на фиг. 5 временные диаграммы сигналов в основных уэлах интерполятора; на фиг. 6 - тра екто|жя зллиптической интерполяции. В предлагаемый интерполятор входит (фиг. 1)-лервый накапливающий сумматор блок 2 управления, первый коммутатор 3, блок 4 вычисления разности, первый счетчи 5, двувходовый элемент И 6, первый 7 и второй 8 регистры, второй-накапливающий сумматор 9, второй коммутатор 10 и второй счетчик 11. Интерполятор имеет управляющие входы Пуск и Стоп связанные с одноименным входами блока 2 управления, содержащего (фиг. 2) триггер 12, первый 13, второй 14 и третий 15 элемеиты задержки, переключа тель 16 направления движения (по или про тив часовой стрелки), переключатель 17 номера полуквадрапта, элемент 18, два двувходовых элемента И 19 и 20, элемент ИЛИ 21, элементы И 22 и 23, а также генератор 24 импульсов. Переключатель 16 направления движения и переключатель 17 номера полуквадранта содержат по одному двухпозиционному переКлючателю на три направления каждый. Блок 4 вычисления разности (фиг. 3) состоит иэ комбинационного сумматора 25 8 с двумя входами, причем разрядные выходы этого сумматора смещены в сторону старших разрядов, а rta место младшего разряда подается ннзкий уровень напряжения (О), если операции в первом накапливающем сумматоре 1 выполняются в дополнительном коде (если в обратном коце, младший разряд подключен к знаковому разряду). Вход переноса младшего разряда комбинационного сумматора 25 связан с высоким уровнем напряжения (1). Коммутатор 3, (фиг. 4) содержит на каждый разряд три элемента И 26 и один трехвходовый элемент ИЛИ 28. Причем его входы связаны с выходами элементов И 26 и 27, входы которых в свою очередь соединены cooтвeтcтвyюши ffl входами, а также с управляющими шинами первого вхо да коммутатора 3. Второй коммутатор имеет два управляющих и два информационных входа, т.е. третий элемент И в каждом разряде из схемы исключен. Величины задержек и t первого и второго элементов задержки выбираются большими времени сложения сумматоров 1, но меньшими половины периода следования импульсов от генератора 24. Разрядность сумматорюв 1 и 9 и счетчиков 5 и 11 выбирается в зависимости от величины R (большая полуось эллипса). Ниже приведены рекуррентные соотношения, составляющие алгоритмы работы предлагаемого интерполятора (конкретизироваиные для первого полуквадранта первого квадранта при движении против часовой стрелки). i + -t Zi + ЬМ Гх. ,ес ,-1 , если j7,0 , , ес.Аи Uj о Ъ V .если U: 1,0

е i 0, 1, 2, ... - номер такта (шага) интерполяции;

интерполяции;

X;, УО - начальная точка интерполяции;

;, и. - текущие содержимые Лервого 1 и второго 9 накапливающих сумматоров, соответственно;

Х; , Z. - текущие содержимые первого 5 и второго 11 счетчиков соответственно;

X;, у- - текущие координаты эллиптической интерполяции, задающие траекторию; R ,(- - длины больщой и малой полуосей эллипса измеренные в шагах интерполяции; f 3 ,-р - оператор взятия цело части величины, находящейся в скобках Перед началом работы триггер 12 в блоке 2 управления должен быть сброшен в О, в первый 5 н второй 11 счетчики заносятся координаты начальной точки х и оС соответственно, а в первый 1 н второй 9 накапливающие сумматоры R и (у-г) соответственно. Кроме того, в первый 7 и второй 8 регистры заносятся величины н (R-h I соотаетственно. В дальнейшем интерполятор работает по тактам, начиная после появления сигнала Пуск, поступающего на элемент 13 задерж ки и через элемент ИЛИ 21 на выход бло 2 управления. Запускается первый коммутатор 3, который подсуммирует к содержимому первого накапливающего сумматора 1 величину 2(2д-)(ц)+ 2, получаемую на блоке 4 вычисления разности. На этом заканчивается подготовка начального значения EQ . Спустя некоторое время, задаваемое элементом 13 задержки ( i c,v« ) сигнал Пуск появляется на входе 5 триггера 12 и, устанавливая его в 1, , разрешает прохождение первого и последую них импульсов от генератора 24 импульсов на входы первого 22 и второго 23 элементов И. Допустим необходимо воспроизвести дугу эллипса, находящуюся в первом полуквадранте (против часовой стрелки). В каждом такте сигналы, приходящие со знакового разряда первого сумматора I

(§{/0 или Е; 0), поступают через переключатель 16 направления движения , элементы И 22 и 23IB блок 5, а через элементы 14 и 15 задержки и пе{ ключатель 17

номера квадранта первый и далее в блок 3.

Сигналы на втором выходе увеличивают на 1 соде{ «(Ммое второго счетчнка и могут уменьшить на 1 содержимое первого счетчика в зависимости от знака содержимого первого сумматора 1 (если

Е ( 7/ О, то уменьшают на 1, если S,- О не изменяют).

Сигналы с . первого выхода первого блока управления поступают на управляющий

вход первого коммутатора 3, разрешая подсуммированне к содержимому первого сумматора 1 либо (-2xj+ + 1), либо (), либо 2( х, )+2 по соответствующим входам. Этим производится корректировка оценочной функции 6 Вычисление величины ( ; - х,. ) производится с помощью блока 4 вычисления разности, а точнее, с помощью комбинационного сумматора 25. При зтом на вход переноса младшего разряда подается 1, а умножение на два осуществляется за счет смещения влево на один разряд (разрядник) выходов при подключении сумматора 25 к первому коммутатору 3. Импульс поступающий на вход первого счетчика 5, является выходным импульсом по выходу (координата х ) цифрового интерполятора, а такой же импульс на входе второго счетчнка 11 проходит на выходе (координата ) интерполятора не во всякий такт, а только в случае, если элемент И 6 открыт. Он управляется знаком содержимого второго сумматора 9. В каждом такте это содержимое обновляется под управлением первого 19 и второго 20 элементов И блока улравления 2 в зависимости от сигнала по второму входу 9, поступающего на один из входов каждого из этих элементов либо непосредственно, либо через элемент НЕ 18. Таким образом, в конце каждого такта через второй коммутатор 10 к содержимому второго сумматора 9 подсуммнруется либо - из первого 7, либо - из второго 8 регистров. Содержимые этих регистров поступают на входы второго коммутатора 10 и проходят через элементы И 26 и ИЛИ 28. Количество тактов задается внещней схемой (не показана), которая в определенный момент (например, при достнженин траекторней заданной точки на плоскости) вьщает сигнал Стоп. Он поступает на вход триггера 12, который, устанавливаясь в О, запрещает дальнейшее прохождение импульсов

(тактов) с генератора 24 импупъсоъ на все выходы блока 2 управления.

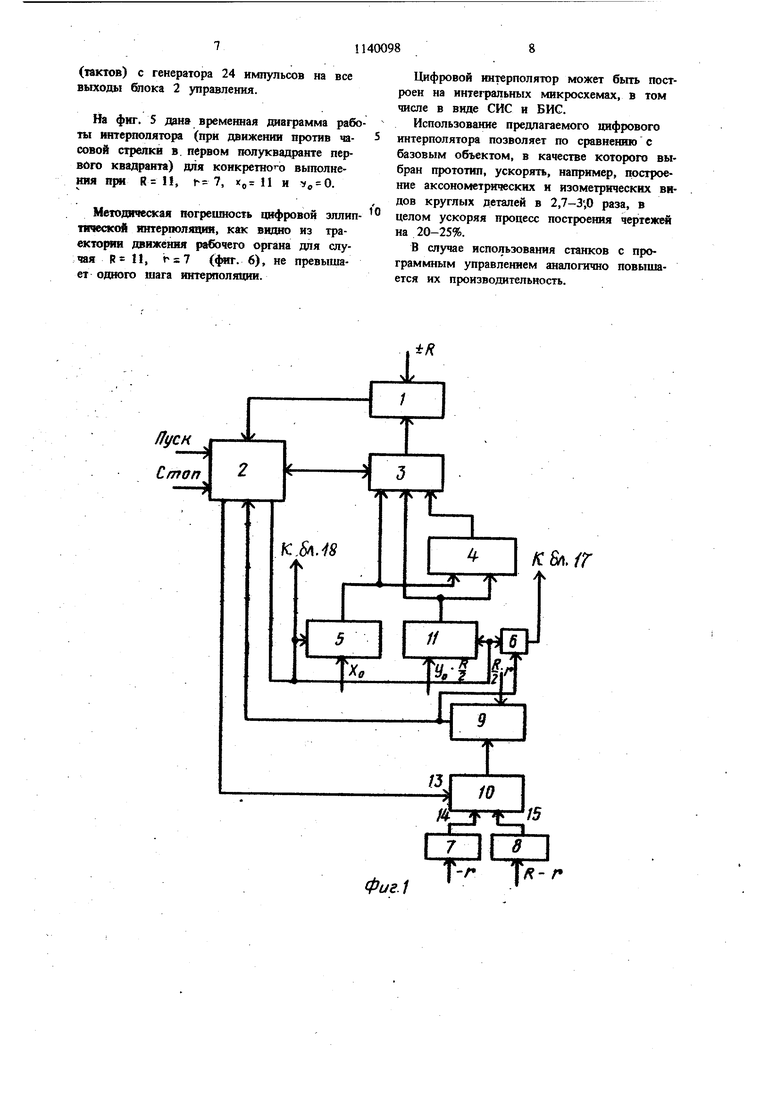

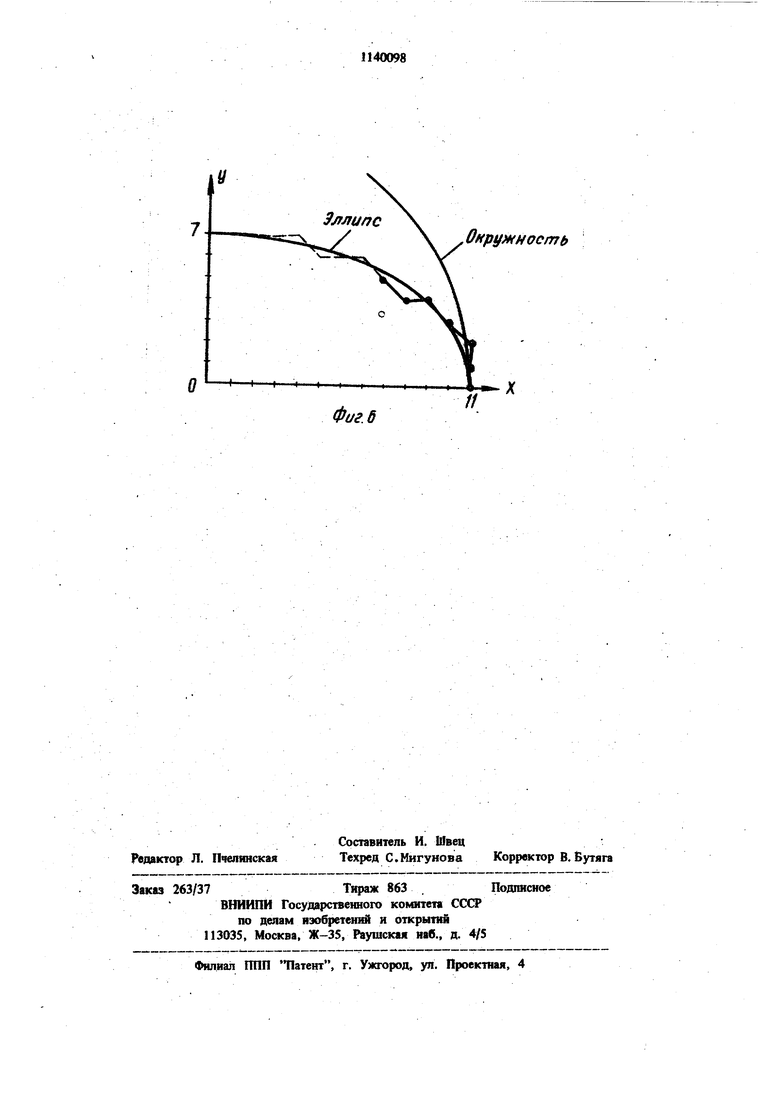

На фиг. 5 дан временная диаграмма работы интерполятора (прн движении против часовой стрелки в. первом полуквадранте первого квадраита) для конкретного выполнения П1Ж , -7, f,-II и -Уд-О.

Методическая погрешность цифровой эллиптячеоо юперооляфш, как видно из траектории движения рабочего органа для случая R И, Ь 7 (фиг. 6), не превышает одного шага интерполяции.

ус/

Стоп

Цифровой интерполятор может бьпъ построен на интегральных микросхемах, в том числе в виде СИС и БИС.

Использование предлагаемого цифрового интерполятора позволяет по сравнению с базовым объектом, в качестве которого выбран прототип, ускорять, например, построенне аксонометрических и изометрических видов круглых деталей в 2,7-3,0 раза, в целом ускоряя процесс построения чертежей на 20-25%.

В случае использования станков с программным управлением аналогично повышается их производительность.

К..1Г

ШС4

Т-г лк-г

Фиг.1

t t t t t t t Т t

mw

-XIZ

.S

HSn.S

Н5Л.10

Фиг. 2

25

Фие.:5 .

Фие.Ц.

Фив. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР .N 758074, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Круговой интерполятор | 1980 |

|

SU875343A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-02-15—Публикация

1983-10-11—Подача