1

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств.

Известно устройство для умножения чисел, содержащее регистры множимого и множителя, сумматор и логические элементы. OWUKO в этом устройстве отсутствует возможность умножения отрицательных чисел на два разряда.

Наиболее близким техническим решением к изобретению является устройство, содержащее регистр множимого, регистр множителя, комбинационный сумматор, регистр поразрядных сумм и регистр переносов, причем выход регистра переноса подключен к первому входу комбинационного сумматора, выход суммы по модулю два комбинационого сумматора подключен к входу регистра подразрядных сумм, выход переноса первого младшего разряда комбинационного сумматора подключен к входу второго младшего разряда регистра переноса, выход переноса второго младшего разряда комбинационного сумматора подключен к входу первого младшего разряда комбинационного сумматора, входные шины.

Недостатком известного устройства является

узкий диапазон перемножаемых чисел и низкое быстродействие.

Цель изобретения - расширение диапазона умножаемых чисел и повышение быстродействия.

Это достигается тем, что в устройство введены группы элементов И, триггер, дешифратор, причем выход регистра множимого подключен к входам элементов И первой группы, вторые входы которых подключены к выходу децшфратора и к входу триггера, выход которого подключен к первому входу дешифратора и к первым входам элементов И второй группы, вторые входы которых подключены к первой входной шине, к первым входам элементов И третьей и четвертой rpymi, выходы элементов И четвертой группы подключены к второму входу комбинационного сумматора, второй выход которого подключен к первым входам элементов И пятой группы, выходы ко торых подключены к входу регистра переноса, выходы элементов И первой группы подключены к третьему входу комбинационного сумматора, четвертый вход которого подключен к выходам элементов И второй грутшы, выходы двух младших разрядов комбинационного сумматора подключены к соответствующим входам элементов И третьей

3

rpyiuibi, вторые входы элементов И пятой груниь. подключе1 ы к второй входной шине,

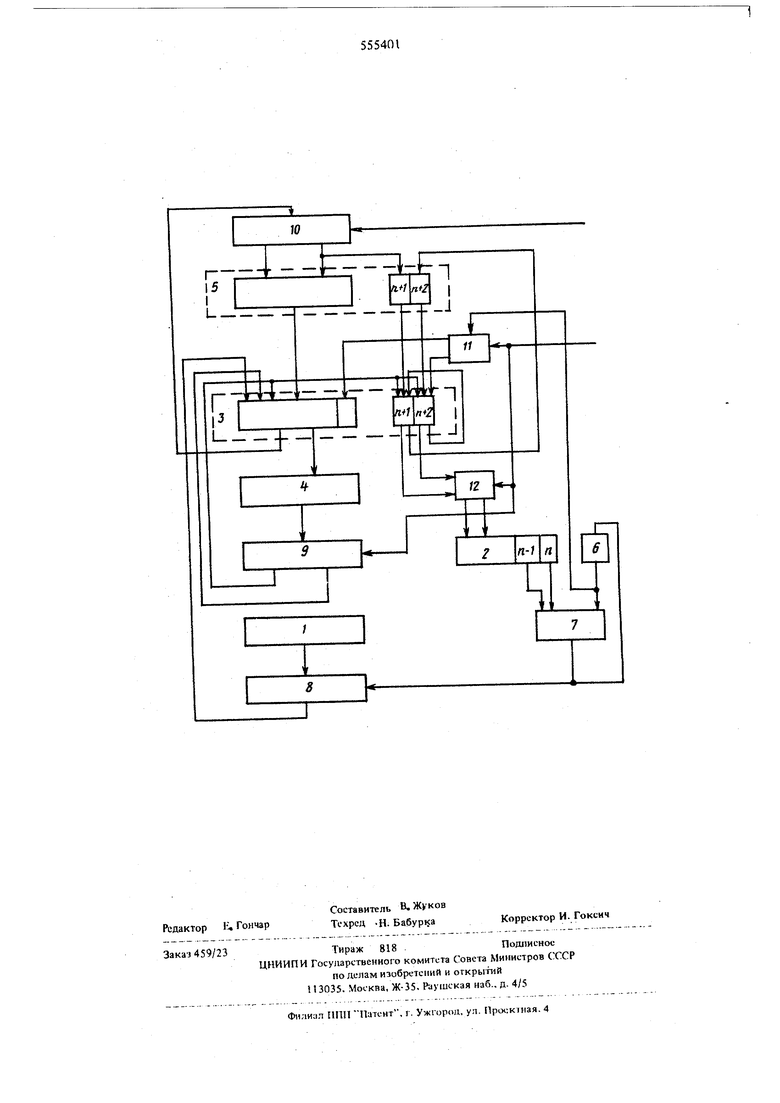

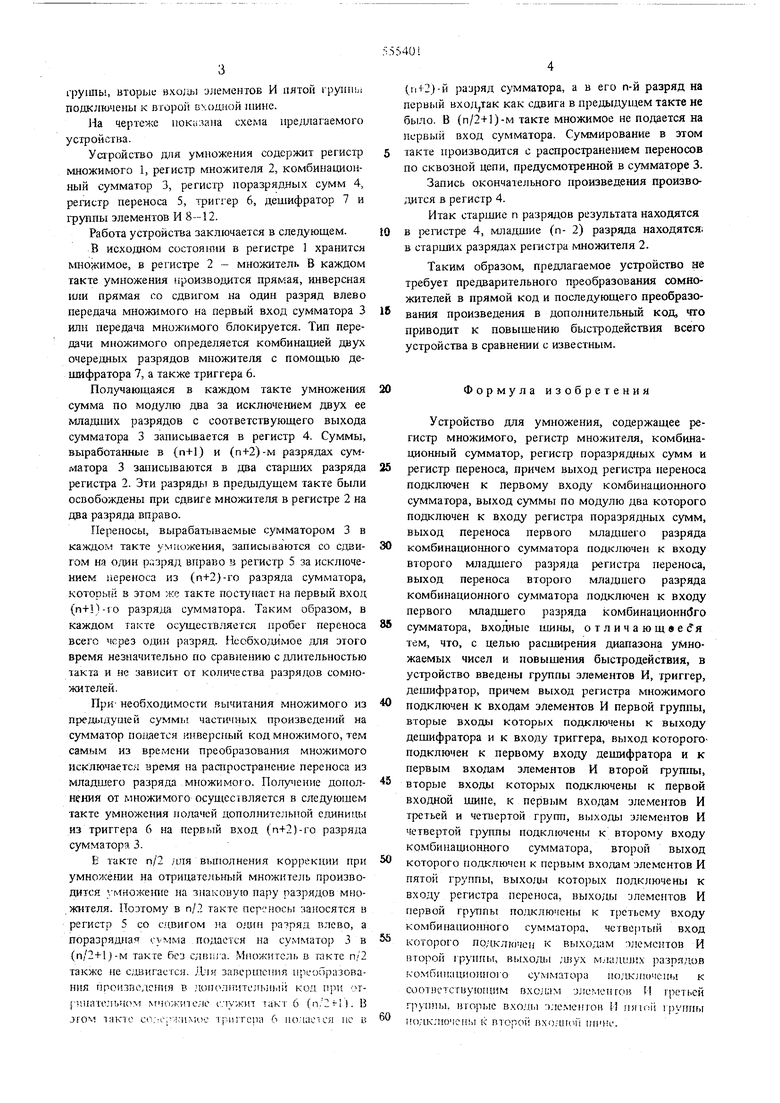

Ла чертеже 11окн; а 1а схема предлагаемого устройства.

Ует-ройство для умножения содержит регистр множимого 1, регистр множителя 2, комбинационный сумматор 3, регист т поразрядаых сумм 4, регистр переноса 5, триггер 6, дешифратор 7 и группы элементов И 8-12.

Работа устройства заключается в следующем.

В исходном состоятш в регистре 1 хранится кшожимое, в регистре 2 множитель В каждом такте умножения производится прямая, инверсная шш прямая со сдвигом на один разряд влево передача множимого на первый вход сумматора 3 или передача множимого блокируется. Тип передачи множимого определяется комбинацией двух очередных разрядов множителя с помощью дешифратора 7, а также триггера 6.

Получающаяся в каждом такте умножения сумма по модулю два за исключением двух ее младших разрядов с соответствующего выхода сумматора 3 записьшается в регистр 4. Суммы, выработанные в {п+1) и (п+2)-м разрядах сумматора 3 записываются в два старших разряда регистра 2. Эти разряды в предыдущем такте были освобождены при сдвиге множителя в регистре 2 на два разряда вправо.

Переносы, вырабатываемые сумматором 3 в каждом такте умножения, записываются со сдвигом на O/1J1H разряд вправо в регистр 5 за исключением переноса из (п+2)-го разряда сумматора, который в этом же такте поступает на первый вход (п+)-го разряда сумматора. Таким образом, в каждом такте осуществляется пробег переноса всего через одан разряд. Необходимое для этого время незначительно по сравнению с длительностью такта и не зависит от количества разрядов сомножителей.

При- необходамости вычитания множимого из предыдуглей суммы частичных произведений на сумматор подается инверсный код множимого, тем самым из времени преобразования множимого исключается аремя на распространение переноса из младшего разряда множимого. дополнения от множимого осудюствляется в следуюшем такте умножения подачей дополнительной единицы из триггера 6 на первый вход (п-ь2)-го разряда сумматора 3.

В такте п/2 для выполнения коррекции при умноже1ши на отридательшлй множитель производится умножение па знаковую пару разрядов множителя. Поэтому в п/2 такте переносы за}юсятся в регистр 5 со сдвигом j,a один разряд влево, а поразряд 1ая сумма подается на сумматор 3 в (п/2+lj-M такте без c;usnra. Множитель в гакте п,2 также не сдаигастся. Яч;; завершения преобразования ПРОИЗПС/ГСНИЯ в .UOI(. lfMTe(bJU.ri код С)Тj-Hi,iaTo:ib(M NT40 Ki ie;ie служит акт б (n/Zfl). В jrov 1ЯК1С с(Х:0.-- ;11Л1ис TjunTciKi 6 iio.uieiCH по в

()-й разряд сумматора, а в его п-й разряд на первый вход,так как сдвига в предыдуидем такте не было. В (п/2+1)-м такте множимое не подается на первый вход сумматора. Суммирование в этом такте производится с распространением переносов по сквозной депи, предусмотренной в сумматоре 3.

Запись окончательного произведения проиэводатся в регистр 4.

Итак старшие п разрядов результата находятся в регистре 4, младшие (п- 2) разряда находятся; в старших разрядах регистра множителя 2.

Таким образом, предлагаемое устройство не требует предварительного преобразования сомножителей в прямой код и последующего преобразования произведения в дополнительный код, что приводит к повышению быстродействия всего устройства в сравнении с известным.

Формула изобретения

Устройство для умножения, содержащее регистр множимого, регистр множителя, комбинационный сумматор, регисф поразрядных сумм и регистр переноса, причем выход регисфа переноса подключен к первому входу комбинационного сумматора, выход суммы по модулю два которого подключен к входу регистра поразрядных сумм, выход переноса первого младшего разряда комбинациошюго сумматора подключен к входу второго младшего разряда регистра переноса, выход переноса второго младшего разряда комбинадиошюго сумматора подключен к входу первого младшего разряда комбинационнйго сумматора, входные шины, отличающее (Гя тем, что, с целью расширения диапазона умножаемых чисел и повышения быстродействия, в устройство введены группы элементов И, триггер, дешифратор, причем выход регистра множимого подключен к входам элементов И первой группы, вторые входы которых подключены к выходу дешифратора и к входу триггера, выход которогоподключен к первому входу дешифратора и к первым входам элементов И второй грушп 1, вторые входы которых подключены к первой входной шипе, к первым входам элементов И третьей и четвертой групп, выходы элементов И четвертой группы подключен. к второму входу комбинационного сумматора, второй выход которого подключен к первым входам элементов И пятой группы, Bbixoju.i которых подключены к входу регистра переноса, выходы элементов И первой группы подключены к третьему входу комбинационного сумматора, четвертый вход которого по/(ключеп к выходам njie.vfcitTOB И второй группы, В1.ходы -ujyx млашиих разрядов Гч-омб1П1ацноино10 сумматора подключены к соотвстсгвуЕошим входам злемсигов П третьей группы, вторые входы эле.менток И пикм i ругшы 1()дк;ио1си:,1 к пторсп; вхо.чисч lunni.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

Авторы

Даты

1977-04-25—Публикация

1975-10-02—Подача