с нулевым входом второго триггера, И-НЕ, выход которого соединен с нувыход которого является третьим вы- левым входом первого триггера, едиходом блока, третий вход которого ничный вход которого является четсоединен с вторым входом элемента вертым входом блока.

102A92i|

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для контроля логических узлов | 1984 |

|

SU1188740A2 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1307459A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля многовыходных логических элементов | 1985 |

|

SU1345198A1 |

1.. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ, содержащее генератор тестов, блок управления, анализатор сигнатур, причем группа информационных выходов генератора тестов соединена с входами проверяемых узлов, первый управляющий выход генератора тестов соединен с первым входом блока управления, второй вход которого соединен с вторым управляющим выходом генератора тестов, синхровход которого соединен с первым выходом блока управления, второй выход которого соединен с синхровходом анализатора сигнатур, управляющий вход которого соединен с третьим выходом блока управления, третий вход которого соединен с выходом анализатора сигнатур, четвертый вход блока управления является входом запуска устройства, о т л и чающееся тем, что, с целью повышения быстродействия, в него введен мажоритарный блок, и групп (где п - число проверяемых узлов) информационных входов которого соединены соответственно с п группами выходов проверяемых узлов, группа выходов мажоритарного блока соединена соответственно с группой информационных входов анализатора сигнатур, выход которого соединен с управляющим входом анализатора сигнатур, второй выход блока управления соединен с синхровхо. дом мажоритарного блока. 2.Устройство по п. 1, о т л и ч а ю щ е е с я тем, что мажоритарный блок содержит п мажоритарных элементов, дешифратор, узел индикации, причем информационные входы блока индикации соединены соответственно с выходами дешифратора, управляющий вход которого соединен с синхровхоI дом блока индикации и является синхровходом блока, управляющий вход блока индикации является управляющим входом блока, выходы мажоритарных элементов соединены соответственно с информационными входами, дешифратор ра и являются группой выходов блока tt групп информационных входов блока соединены соответственно с входами Ю мажоритарных элементов. Oil 3.Устройство по п, 1, о т л и CD чающееся, тем, что блок управto ления содержит два триггера, генера(i тор импульсов, элемент И, элемент И-НЕ J п.ричем выход первого триггера соединен с управляющим входом генератора импульсов, выход которого соединен .с первым входом элемента И и является первым выходом блока, второй выход которого соединен с выходом элемента И, второй вход которого соединен с единичным входом второго триггера и является первым входом блока, второй вход которого соединен с первым входом элемента И-НЕ,

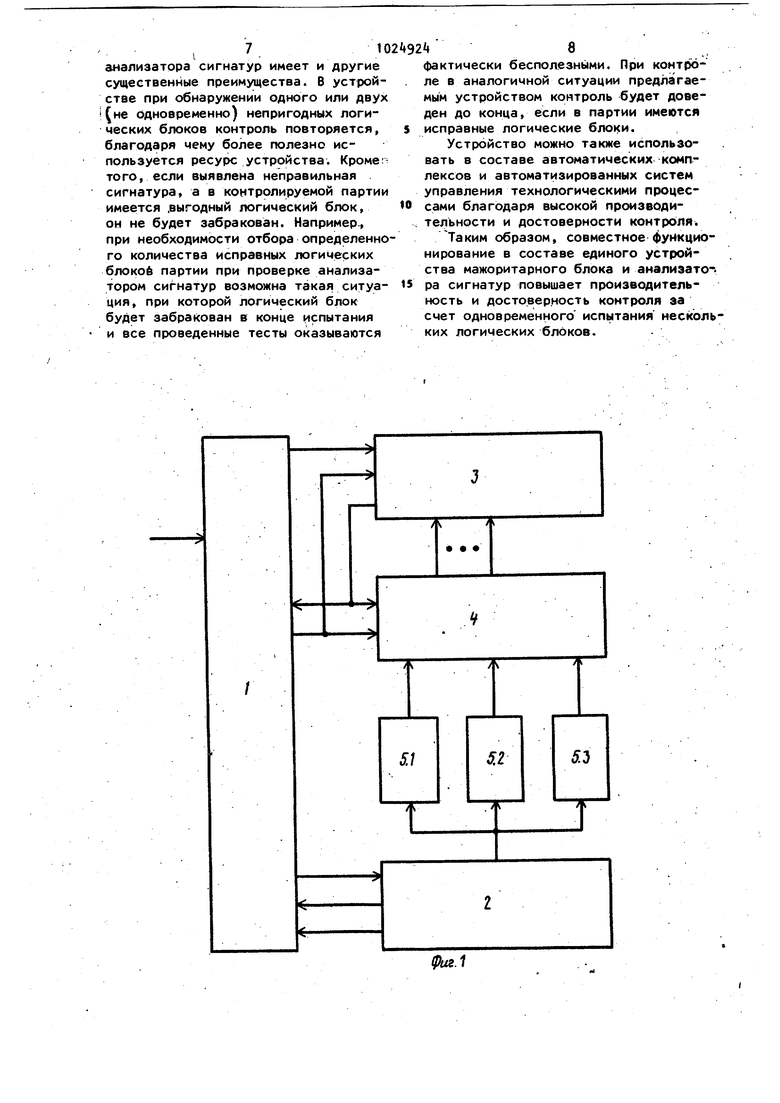

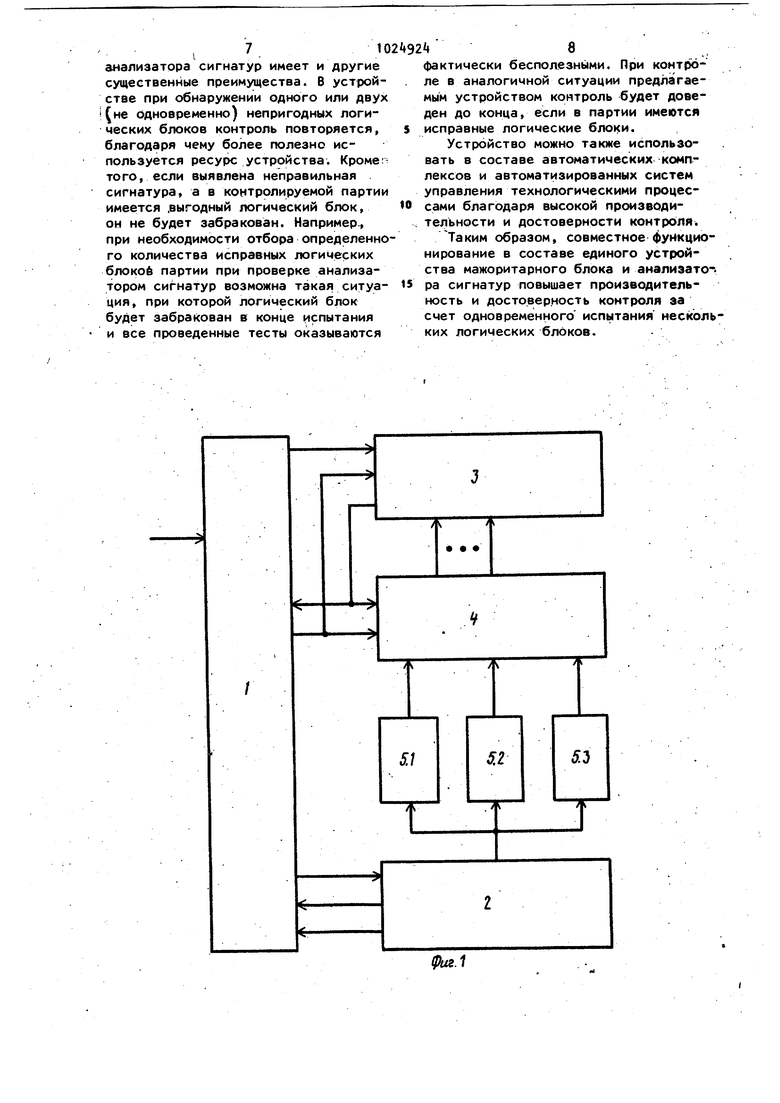

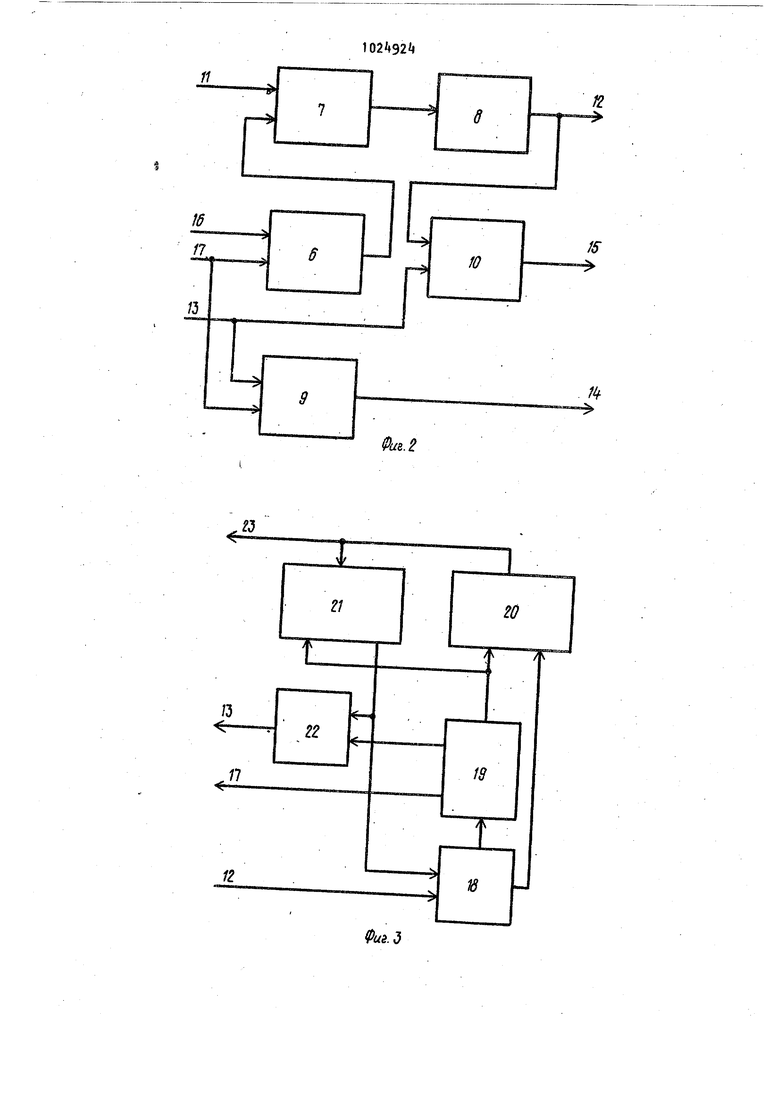

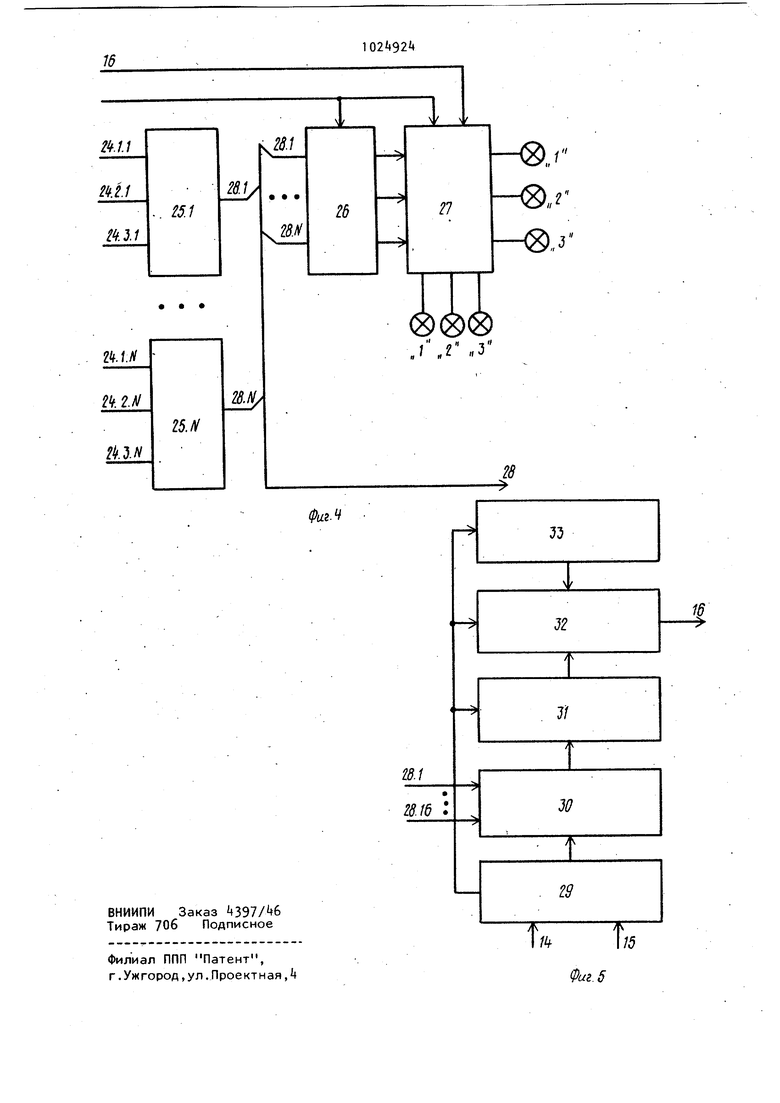

i Изобретение относится к вычислительной технике, в частности к аппаратуре контроля логических вычислительных машин, и может быть использовано в электронике для контроля логических микросхем средней и большой степени интеграции, а также .в составе автоматических комплексов и автоматизированных систем управления производства ТЭЗов, контролеров и других логических блоков, Известно устройство для контроля микросхем, где в качестве аппаратурного стимулятора используется двоичный счетчик, а в качестве регистра тора выходов - блок сравнения с выходами эталонной микросхемы 1J . Недостатком этого устройства является необходимость эталонной микро схемы, потому что неисправности сиетемы стимуляции максируются совпадающими выходами эталонной и контролируемой микросхем, так как стимуляция производится параллельно и не. контролируется, . Наиболее близким к изобретению по технической сущности является . устройство для обнаружения неисправностей, содержащее генератор тестов, блок управления, анализатор сигнатур причем группа информационных выходов генератора тестов соединена с входам проверяемого узла, первый управляющий выход генератора тестов соединен с первым входом блока управления, второй вход которого соединен с вторым управляющим выходом генератора тестов, синхровход которого соединен с первым выходом блока управления, второй выход которого соединен с синхровходом анализатора сигнатур, управляющий вход которого соединен с третьим выходом блока управления, третий вход которого соединен с выходом анализатора сигнатур, четвертый вход блока управления является входом запуска устройства И , Недостатками известного устройст- ва являются невозможность проверки одновременно нескольких проверяемых узлов и невозможность в случае обнаружения неисправности осуществлять проверку оставшихся проверяемых узпов, что снижает быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство для контроля Логических узлов, содержащее генератор тестов, блок управления, анализатор сигнатур, причем группа информационных выходов генератора тестов соединена с входами проверяемых узлов, первый управляющий выход генератора тестов соединен с первым входом блока управления, второй вход которого соединен с вторым управляющим выходом генератора тестов, синхрсвход которого соединен с первым выходом блока управления, второй выход которого соединен с синхровходом анализатора сигнатур, управляющий вход которого соединен с третьим выходом блока управления, третий вход которого соединен с выходом анализатора сигнатур, четвертый вход блока управления является входом запуска устройства, введен мажоритарный блок, п групп (где п число проверяемь1х узлов информационных входов которого соединены соответственно с П группами выходов проверяемых узлов, группа выходов мажоритарного блока соединена соответственно с группой информационных входов анализатора сигнатур, выход которого . соединен с управляющим входом анализатора сигнатур, второй выход блока управления соединен с синхровходом мажоритарного блока. При этом иажоритарный блок содержит |i мажоритарных элементов, дешифратор, узел индикации, причем информационные входы блока индикации соединены соответственно с выходами дешифратора, управляющий вход которого соединен с синхровходом блока индикации и является синхровходом блока, управляющий вход блока индикации является управляющим входом блока, выходы мажоритарных элементов соединены соответственно с информаци онными входами дешифратора и являются группой выходов блока, п групп информационных входов блока соединены соответственно с входами мажоритарных элементов. Кроме того, блок управления содержит два триггера, генератор импульсов, элемент И, элемент И-НЕ, причем выход первого триггера соединен с управляющим входом генерато ра импульсов, выход которого соедин с первым входом элемента И и является первым выходом блока, второй выход которого соединен с выходом элемента И, второй вход которого со динен с единичным входом BToporq триггера и является первым входом блока, второй вход которого соедине с первым входом элемента Й-НЕ, с нулевым входом второго триггера, выход которого является третьим выходом блока, третий вход которого соединен с вторым входом элемента И-НЕ, выход которого соединен с нулевым входом первого триггера, ед ничный вход которого является четве тым входом блока. На фиг. V показана схема предлаг емого устройства на фиг. 2 - блок управления{ на фиг. 3 - генератор тестов;на фиг. k - мажоритарный, блок; на фиг. 5 анализатор сигнат Устройство содержит блок 1 управ ления, генератор 2 тестов, анализатор 3 сигнатур и мажоритарный блок Ц. Одинаковые выходы проверяемых узлов 5.1 -5.3 соединены с соответствующими входами мажоритарного бло ка 4. Блок 1 управления содержит элеме ИЛИ-НЕ 6, триггер 7, генератор 8 им пульсов, триггер 9 и элементИ 10. При подаче разрешающего уровня Начало контроля на вход 11 триггер 7 разрешает работу генератора 8 импульсов, который формирует на вых де 12 синхроимпульсы, поступающие на элемент И 10 и генератор 2 тесто При поступлении разрешающего уровня по входу 13 от генератора 2 триггер 9 формирует сигнал Пуск высокого уровня на выходе I, а элемент И 10 при этом пропускает синхроимпульс на выход 15, поступающий на мажоритарный блок . Триггер 7 управления запрещает работу генератора 8 импульсов при поступлении сигнала Неправильная сигнатура на вход 16 от анализатора 3 сигнатур и Конец контроля на вход 17 от генератора 2 тестов. Триггер 9 при поступлении сигнала Конец контроля на вход 17формирует команду Стоп низкого уровня на выход 1. Генератор 2 тестов содержит узел 18считывания, узел 19 памяти, буферный регистр 20, узел 21 контроля по четности и элемент И 22.При поступлении синхроимпульса на вход .12 узел 18считываний формирует адрес узла 19и сигнал записи в буферный регистр 20. На выходной шине узла 19 формируется параллельный код, который переписывается в буферный регистр 20 по команде записи. Узел 21 формирует разрешающий уровень при совпадении выходов узла 19 памяти и буферного регистра 20. При несовпадении выходов узел 21 формирует запрещающий уровень, узел 18 считывания блокируется на текущем адресе и при поступлении следующего синхроимпульса по входу 12 производит повторную запись в буферный регистр 20. Этим же уровнем блокируется формирование разрешающего урбвня на выходе 13 элемента 22. Разрядность используемой двоичной комбинации на выходной шине зависит от количества входов контролируемых логических блоков 5. - 5..3. Два старших разряда выходной шины узла 19 выполняют следующие функции. При считывании последней тестовой комбинации появление уровня логического нуля в предпоследнем разряде соответствует выдаче команды Конец измерения на выходе 17. Уровень логического нуля в старшем разряде выходной шины узла 19 блокирует формирование разрешающего уровня на выходе 23. Это необходимо для организации начальных установок для контролируемых логических узлов 5.1 - 5.3. Мажоритарный блок имеет входы 2, мажоритарные элементы 25.1 2511, где П - число контролируемых выходов логических узлов (ni 1-1б), дешифратор 26 и узел 27 индикации. Мажоритарные элементы 25 осуществляЮТ мажорирование (выбор по большинс ву) . При этом на выходе 28 мажоритар ного элемента 25 формируется информа ция, присутствующая на большинстве его входов 2. Узел 27 индикации в .зависимости от наличия на входе 15 синхроимпульсов и на входе 16 - сигнала Неправильная сигнатура включает лампочки Контроль повторить или Брак. При правильном функционировании всех контролируемых логических блоков индикация отсутствует. Анализатор 3 сигнатур содержит распределитель 29 импульсов, регистр с элементами 30 сложения по модулю два, peгиcтt) 31 памяти, узел 32 сравнения и узел 33 памяти. Начальная установка производится сигналом Пуск высокий уровень), поступающим на вход И распределителя 29 импульсов. С этого момента до при хода команды Стоп (низкий уровень) на вход Н, при поступлении каждого синхроимпульса на вход ,15 р аспределитель импуль ов формирует импульсы, управляющие работой анализатора 3 сигнатур. На входы 28.1 - 28.16 регистра сдвига с элементами 30 сложения по модулю два поступает информация с выходов мажоритарного блока Регистр с элементами 30 сложения по модулнэ два имеет обратные связи, кот торые совместно с входами 28.1-28.16 соединены с элементами сложения по модулю два. Сформированный таким образом код является сигнатурой, которая поступает в регистр 31 памяти для хранения. Узел 32 сравнени производит по команде распределител 29 импульсов сравнение сигнатур, хранящихся в регистре 31 памяти и узле 33 памяти. При несовпадении сигнатур формируется команда Непра вильная сигнатура, поступающая на выход 16. Устройство работает следующим образом. При подаче разрешающего уровня Начало контроля блок 1 управления формирует синхроимпульсы, которые поступают на вход генератора 2 гее-. тов. На выходе.генератора 2 тестов формируется необходимое количество комбинаций, устанавливающих контролируемые логические блоки 5.1-5-3 в исходное состояние. Затем генерато 2 тестов формирует разрешающий уро24вень и синхроимпульс блока 1 управления поступает на мажоритарный блок .Мажоритарный блок k производит сравнение каждого разряда и форми-рует на выходах параллельный код, соответствующий мажоритарнодти. Если информация на входах мажоритарных элементов не совпадает, мажоритарный блок А в зависимости от присутствия синхроимпульса и команды Неправильная сигнатура индицирует номер контролируемого логического узла Брак, Контроль повторить. При правильном функционировании всех контролируемых логических блоков индикация отсутстйует. Параллельный код с выходов мажоритарного блока k поступает на входы анализатора 3 сигнатур, который преобразует его в последовательность шестнадцатиричных комбинаций . или сигнатуру. Сигнатура формируется после каждой тестовой комбинации и сравнивается с расчетной (эталонной) . Контроль автоматически прекращается при появлении неправильной сигнатуры и после последней правильной. Контролируемые логические узлы 5.1 - 5-3 признаются годными, если верна последняя сигнатура и нет индикации Крак. Если индикация Брак есть, индицируемые логические блоки забраковываются , а остальные признаются годными. Если контроль прерывается и есть индикация Контроль повторить, . индицируемый логический блок проходит повторный онтроль в составе следующей контролируемой группы. Применение мажоритарного блока в устройствах контроля, приводит к значительному увеличению количества оборудования (для трехвходовых мажоритарных элементов - в три раза). Этим объясняется их ограниченное распространение. В предлагаемом устройстве утраивается количество контролируемых блоков, а не каналов, передающих информацию, т.е. недостаток становится, таким образом, преимуществом. Однако наличие мажоритарного блока само по себе не только не решает задачу контроля, но и не повышает производительность. Для реализации положительного эффекта от мажоритарности необходимо распознать полученную информацию, т.е. определить соответствие правильному функционированию логического блока. Эту задачу решает анализатор сигнатур. Совместное функционирование мажоритарного блока и

анализатора сигнатур имеет и другие существенные преимущества. В устройстве при обнаружении одного или двух (не одновременно) непригодных логических блоков контроль повторяется, благодаря чему более полезно используется ресурс устройства. Кромеп того, если выявлена неправильная сигнатура, а в контролируемой партии имеется .выгодный логический блок, он не будет забракован. Например., при необходимости отбора определенного количества исправных логических блокоб партии при проверке анализатором сигнатур возможна такая ситуация, при которой логический блок будет забракован в конце испытания и все проведенные тесты оказываются

фактически бесполезными. При контроле в аналогичной ситуации предлагаемым устройством контроль будет доведен до конца, если в партии имеются исправные логические блоки.

Устройство можно также использовать в составе автоматических комплексов и автоматизированных систем управления технологическими процессами благодаря высокой производитех1ьности и достоверности контроля.

Таким образом, совместное функционирование в составе единого устройства мажоритарного блока и анализато-. ра сигнатур повышает производительность и достоверность контроля за счет одновременного испытания нескольких логических блоков.

L

17

/3

12

д

15

/«

-НЭ.,/

-®. )„з

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № | |||

| кл | |||

| Q 0 | |||

Авторы

Даты

1983-06-23—Публикация

1981-07-07—Подача