(Я

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ по авт. св. № 1024924, отличающееся тем, что, с целью повышения достоверности контроля, в него введены аналиазтор сигнатур тестовых сигналов и элемент ИЛИ, причем группа информационных выходов генератора тестов соединена с группой информационных входов анализатора сигнатур тестовых сигналов, вход синхронизации и вход обнуления которого соединены соответственно с вторым и третьим выходами блока управления, выходы ошибки анализатора сигнатур и анализатора сигнатур тестовых сигналов соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с третьим входом блока управления, второй вход разрешения мажоритарного блока соединен с выходом ошибки анализатора сигнатур тестовых сигналов.

ОС 00

4

S.2

fi;

S.3

Изобретение относится к вычислительной технике, в частности к аппаратуре контроля логических вычислительных машин, и может быть использовано в электронике для контроля логических микросхем средней и большой степени интеграции, а также в составе автоматических комплексов и автоматизированных .систем управления производства ТЭЗов, контролеров и других логических блоков.

Цель изобретения - повышение достоверности контроля.

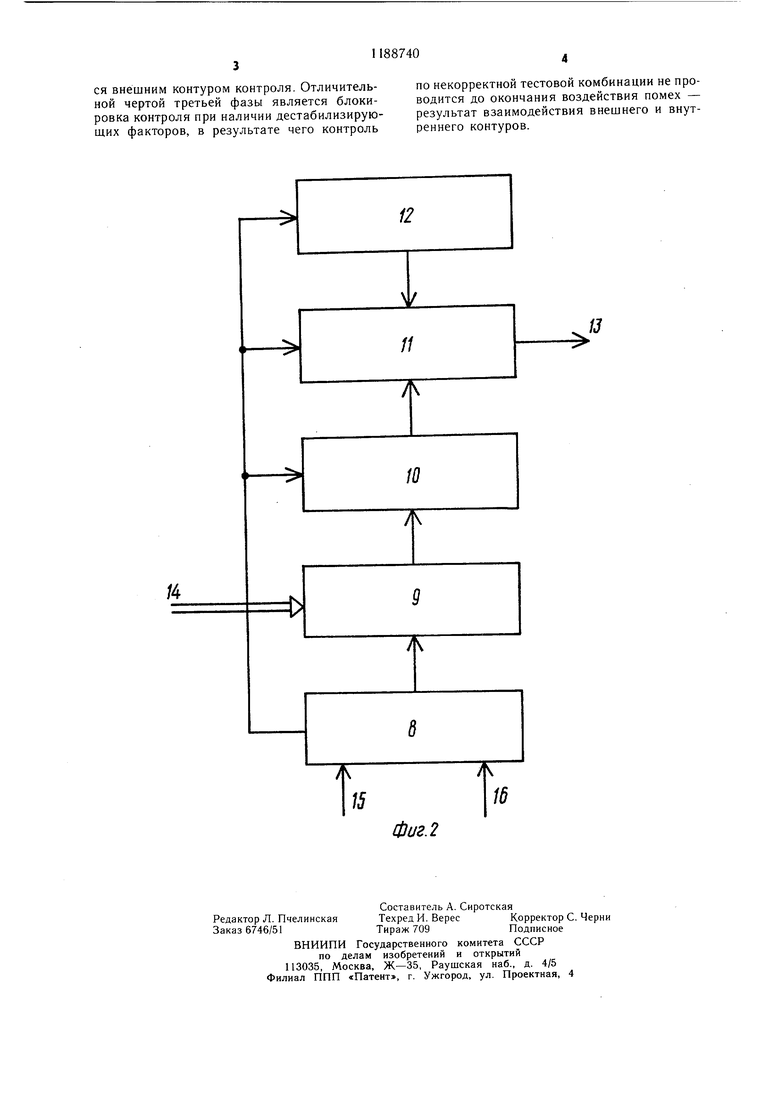

На фиг. 1-показана схема предлагаемого устройства; на фиг. 2 - анализатор сигнатур тестовых сигналов.

Устройство содержит блок 1 управления, генератор 2 тестов, анализатор 3 сигнатур, анализатор 4 сигнатур тестовых сигналов, и мажоритарный блок 5, контролируемые логические узлы 6.1-6.3 и элемент ИЛИ 7.

Блок I управления, генератор 2 тестов и анализатор 3 сигнатур выполнены по основному авт. св. № 1024924.

Анализатор 4 сигнатур тестовых сигналов имеет распределитель импульсов 8, сигнатурный анализатор 9, регистр 10 памяти, схему 11 сравнения, блок 12 памяти, выход 13 неправильного теста, информационные входы 14 анализатора сигнатур тестовых сигналов, вход 15 обнуления и синхровход 16.

Мажоритарный блок 5 содержит дополнительную ячейку индикации, соответствующую выходу неправильного теста анализатора и сигнатур тестовых сигналов.

Устройство работает с..1едуюш,им образом.

Начальная установка производится сигналом «Пуск (высокий уровень), поступающим на вход 15 распределителя 8 импульсов. С зтого момента до прихода команды «Стоп (низкий уровень) на вход 15 при поступлении каждого синхроимпульса на вход 16 распределитель 8 формирует импульсы, управляющие работой анализатора и сигнатур тестовых сигналов. На информационные входы 14 сигнатурного анализатора поступают те же тестовые сигналы от генератора 2 тестов, что и на входы контролируемых логических узлов 6.1-6.3. Сформироншнный таким образом код является сигнатурой, которая поступает в регистр 10 памяти для хранения. Схема 11 сравнения производится по команде распределителя 8 импульсов сравнение сигнатур, хранящихся в регистре 10 памяти и блоке 12 памяти. При несовпадении сигнатур формируется команда «Неправильный тест, которая поступает на выход 13.

При подаче разрешающего уровная «Начало контроля блок 1 управления формирует синхроимпульсы, которые поступают на вход генератора 2 тестов. На выходе генератора 2 тестов формируется необходимое количество комбинаций, устанавливающих контролируемые логические узлы 6.1-6.3 в исходное состояние. Параллельно тестовые

комбинации поступают на вход 14 анализатора сигнатур 4 тестовых сигналов, где по выдаче генератором 2 тестов разрешающего уровня и блоком 1 управления синхроимпульса происходит их преобразование в сигнатуры и формирование команды «Неправильный тест при появлении неправильной тестовой комбинации. В этом случае процедура контроля прерывается и затем контроль повторяется.

Если искажение тестовой комбинации на выходе генератора 2 тестов в результате воздействия дестабилизирующих факторов (внешних помех, бросков по цепям питания и т. д.) произойдет после того,

как анализатор сигнатур 4 тестовых сигналов сформировал правильную сигнатуру, то генератор 2 тестов формирует сигнал, блокирующий работу блока 1 управления до окончания действия помехи.

Одновременно синхроимпульсом блока 1

0 управле 1ия запускается мажоритарный блок 5, который производит сравнение каждого разряда, формирует на выходах параллельный код, соответствующий мажоритарности и если информация на входах мажоритарных элементов не совпадает, в зависимости от присутствия синхроимпульсов и команд «Неправильная сигнатура, «Неправильный тест индицирует номер контролируемого логического узла «Брак или «Контроль повторить. При правильном функциониQ ровании всех контролируемых логических узлов 6.1-63 и генератора 2 тестов, индикация отсутствует. Параллельный коде выходов мажоритарного блока 5 поступает на входы анализатора 3 сигнатур, который преобразует его в последовательность шестнадцатиричных комбинаций или сигнатуру. Сигнатура формируется после каждой тестовой комбинации и сравнивается с расчетной (эталонной). Контроль автоматически прекращается при появлении неправильной сигнатуры и после последней правильной.

0 Контролируемые логические узлы 6.1-6.3 признаются годными, если верна последняя сигнатура и нет индикации «Брак. Если индикация «Брак есть, индицируемые логические узлы забраковываются. Если контроль прерывается и есть индикация «Контроль повторить, индицируемый, логический узел проходит повторный контроль в составе следующей контролируемой группы.

Таким образом, организован двухконтурQ ный контроль тестовых сигналов: внешний и внутренний. Внутренний контур контроля организован анализатором сигнатур тестовых сигналов. Благодаря этому устройство имеет три фазы активного контроля тестовых сигналов. Первая фаза имеет место 5 при формировании тестовых сигналов и осуществляется внутренним контуром контро ля. Характерная особенность второй фазы - проверка корректности тестов - проводится внешним контуром контроля. Отличительной чертой третьей фазы является блокировка контроля при наличии дестабилизирующих факторов, в результате чего контроль

-

/4

по некорректной тестовой комбинации не проводится до окончания воздействия помех - результат взаимодействия внешнего и внутреннего контуров.

12

/J

//

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1984-05-11—Подача